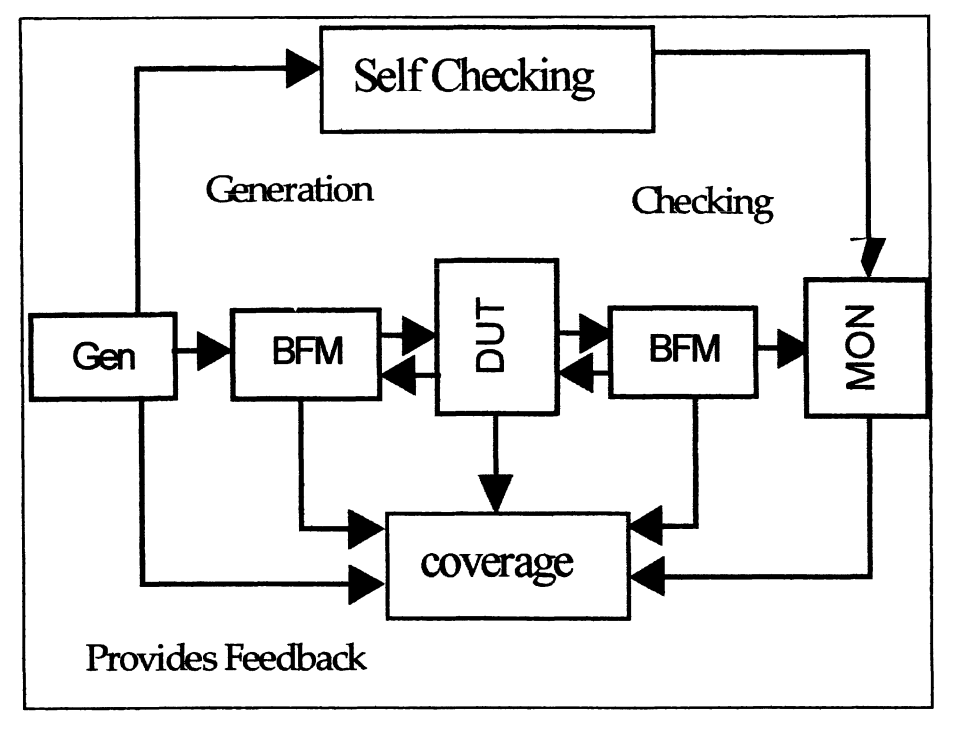

下圖是一個典型的EDA仿真驗證環境,其中主要的組件就是激勵生成、檢查和覆蓋率收集。

這三者缺一不可。

激勵生成是我們驗證環境的第一個關鍵組件,用于驅動DUT到一個預期的狀態。

在DUT正在處理激勵以及完成激勵處理之后我們需要實時的或者離線的checker機制來確保芯片按照預期行為工作。

覆蓋率是最終的量化機制、也可以理解為激勵的反饋機制。我們不斷地激勵著DUT,同時也在進行檢查,整個過程中通過覆蓋率的量化來反饋驗證工程師有沒有驗證完成?哪里還需要繼續驗證?

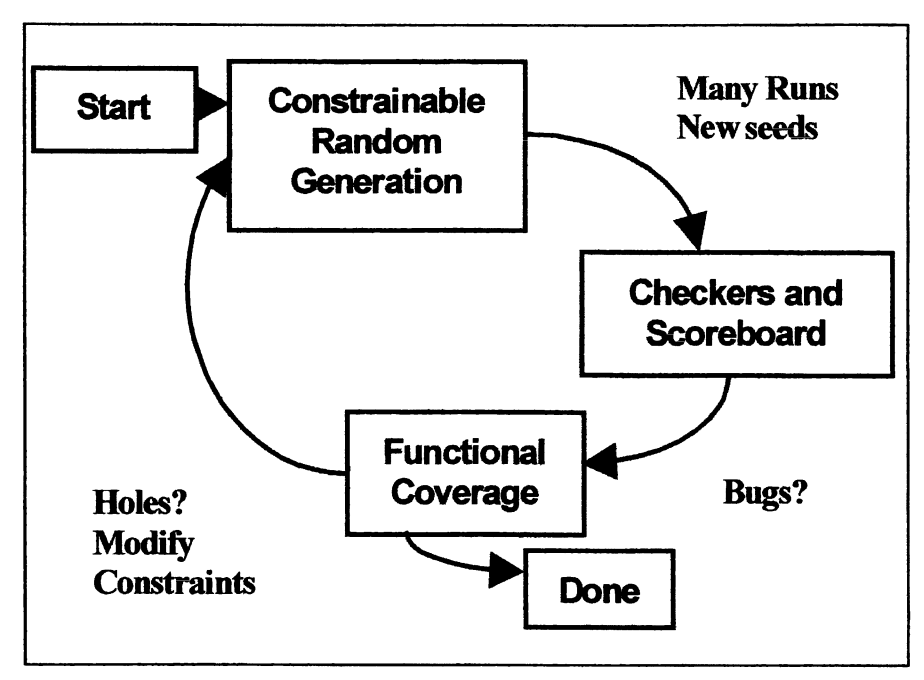

下圖是覆蓋率反饋到激勵,以及表明驗證是否完成的一個流程。在這個流程中,我們不斷地根據覆蓋率調整激勵發送的隨機機制,直到只剩幾個邊界場景很難覆蓋到,我們再構造定向用例。

這是一個比較高效的現代EDA仿真驗證流程,整個流程中激勵生成、檢查機制和覆蓋率量化都需要保證完備性。

完備的激勵+完備的檢查機制+完備的覆蓋率量化才能夠獲得有信心的驗證結果,缺一不可。另外,這三者中的任何一個做到絕對的完備就是非常難的。

如果覆蓋率完備了,也可以保證激勵的完備。如果發現用例構造過程非常困難,大概率是驗證環境架構的不合理。要么趨向于定向用例,你需要維護非常多的sequence,經常一個需求會讓你改動多個sequence;要么趨向完全隨機,可控性比較差。這兩個情況都降低驗證效率。

checker是必須要保證完備的,否則就算你激勵覆蓋到了某個場景,你也識別不出來問題。驗證的重點是發現所有的bug,然后才是盡可能地保證激勵完備性。如果非要分個優先級,個人覺得checker的完備要高于激勵的完備。因為如果你遺漏了某個bug,更上層的驗證環境也許可以通過集成你的checker來發現問題。

覆蓋率也非常重要。否則就是在黑暗中胡亂開槍射擊,你不知道去過哪里,也就不知道后面要往哪里去了。

保證激勵、檢查和覆蓋率的完備,全部都是難點。

審核編輯:劉清

-

eda

+關注

關注

71文章

2813瀏覽量

174564 -

EDA仿真技術

+關注

關注

0文章

5瀏覽量

5459 -

DUT

+關注

關注

0文章

190瀏覽量

12578

原文標題:驗證環境中的激勵、檢查和覆蓋率

文章出處:【微信號:芯片驗證工程師,微信公眾號:芯片驗證工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

西門子EDA助力提升IC設計驗證效率

IC驗證云平臺優勢明顯,這家本土EDA公司如何御風先行?

EDA2俠客島難題挑戰·2025已正式開啟

新思科技推出基于AMD芯片的新一代原型驗證系統

Verilog 電路仿真常見問題 Verilog 在芯片設計中的應用

芯華章發布FPGA驗證系統新品HuaProP3

EDA與傳統設計方法的區別

芯華章生態戰略亮相DAC,發布全流程敏捷驗證管理器FusionFlex,并聯合華大九天推出數模混合仿真解決方案

芯華章推出EDA全流程敏捷驗證管理器昭睿FusionFlex

大規模 SoC 原型驗證面臨哪些技術挑戰?

一個高效的現代EDA仿真驗證流程

一個高效的現代EDA仿真驗證流程

評論