之前的文章中介紹了新舊字符設備驅動開發(fā)的方式,并利用虛擬的字符設備來學習其開發(fā)流程,沒有涉及到操作Linux開發(fā)板上的硬件。 對硬件的操作,究其本質最終都是要操作處理器的寄存器。 因此在操作硬件之前,我們需要先了解有關GPIO的寄存器配置原理及方法

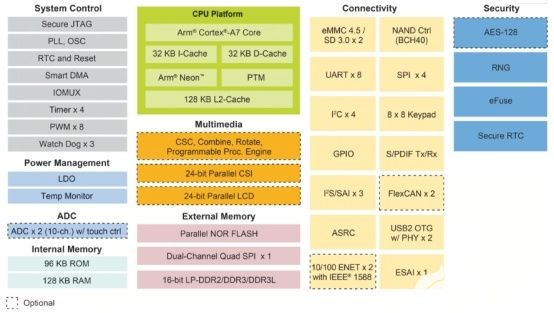

1. 認識i. MX6ULL處理器GPIO

1.1 基本概念

以下是一些名詞縮寫及其含義:

- IO:Input Output,用于CPU與外界進行信息交互

- GPIO:General Purpose IO ports,通用IO口

- SNVS:Secure Non-Volatile Storage 安全的非易失性存儲

- IOMUX:Input Output Multiplexer 輸入/輸出多路復用器

- IOMUXC:Input Output Multiplexer Controller 輸入/輸出多路復用控制器

- SW:Switch 開關

1.2 GPIO邏輯結構

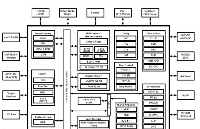

下圖為i. MX6ULL處理器的GPIO硬件結構框圖,其中PAD1和PAD2表示i.MX6ULL芯片引出的GPIO引腳,其余部件均位于芯片內部

上圖中各部分的功能和作用如下

PAD1 :GPIO引腳,其左側通過IOMUX復用選擇器連接到各種寄存器上

IOMUX復用選擇器:用于將芯片引腳與最左側的各種寄存器連接起來

IOMUXC復用控制器:IO通過MUX寄存器來配置復用功能,如GPIO、IIC等; 通過PAD寄存器來配置引腳屬性,如驅動能力,是否使用上下拉電阻等

Block外設功能控制塊:例如具有PWM輸出功能的引腳,它需要PWM外設的支持

GPIO外設:GPIO是每個IO都有的外設,是IO控制的基本功能, 如輸出高低電平、 檢測電平輸入等。 當需要使用引腳的GPIO功能時,就要配置GPIO外設中的各個寄存器

PAD2 :另一個引腳,它與PAD1有一根信號線連接,表示部分引腳的輸出可以作為另一個引腳的輸入

1.3 GPIO命名

i.MX6ULL處理器的GPIO被分為5組,且每組的數(shù)量不同,具體可查閱數(shù)據(jù)手冊

另外根據(jù)IO類別,可以分為兩大類:SNVS域IO和通用域IO,這兩類IO本質上是一樣的

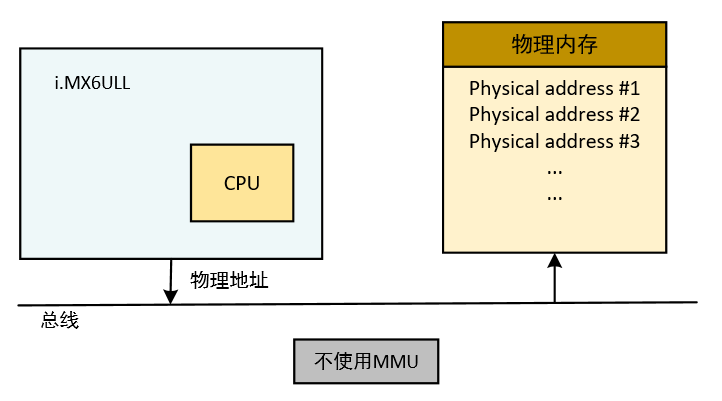

2. 配置i. MX6ULL處理器GPIO

下面以GPIO1_IO00引腳為例,介紹GPIO配置的步驟

2.1 時鐘配置

I.MX6ULL每個外設都有一個外設時鐘,使用GPIO時,也必須先使能對應的時鐘。 CCM (Clock Controller Module)時鐘控制模塊寄存器用來使能外設時鐘。 CMM一共有CCM_CCGR0~CCM_CCGR6這7個寄存器,控制著I.MX6U的所有外設時鐘開關

以CCM_CCGR0為例,它是個32位寄存器,每2位控制一個外設的時鐘,比如 bit31:30 控制著GPIO2 的外設時鐘,兩個位就有 4 種操作方式:

若要打開GPIO2的外設時鐘,只需要設置CCM_CCGR0的bit31和bit30為1即可,即 CCM_CCGR0=3 << 30

2.2 IO配置

配置MUX寄存器:配置復用功能

IOMUXC_SW_MUX_CTL_PAD_GPIO1_IO00寄存器地址為:0x020E005C,只用到了最低的5位,bit0~bit3就是設置復用功能的,該引腳可復用為9種不同功能的IO

配置PAD 寄存器:配置引腳屬性

IOMUXC_SW_PAD_CTL_PAD_GPIO1_IO00寄存器地址為:0x020E02E8,只用到了低17位,用于設置速度、驅動能力、壓擺率等

2.3 GPIO配置

上面的MUX和PAD寄存器都是配置IO的,當把IO配置為了GPIO功能后,還需要繼續(xù)對GPIO外設的各種寄存器進行配置

配置DR寄存器:數(shù)據(jù)寄存器,一個GPIO組最大只有32個IO,32位DR寄存器中的每一個位對應一個GPIO

當設置為輸出模式,向指定的位寫入數(shù)據(jù),相應的IO就會輸出相應的高低電平; 當設置為輸入模式,比如GPIO1_IO00引腳接地的話,GPIO1. DR的bit0就是0

配置GDIR寄存器:方向寄存器,設置GPIO的工作方向是輸入還是輸出,每個位對應一個IO

若要設置GPIO1_IO00為輸入,則GPIO1.GDIR=0;反之GPIO1.GDIR=1

配置PSR寄存器:狀態(tài)寄存器,每個IO對應一個位,用于獲取對應的GPIO的狀態(tài)

是一個只讀寄存器,功能類似于輸入狀態(tài)下的DR寄存器

配置ICR1/ICR2寄存器:中斷控制寄存器,每兩位對應一個GPIO,ICR1用于配置低16個GPIO,ICR2用于配置高16個GPIO

例如設置GPIO1_IO15為上升沿觸發(fā)中斷,則GPIO1.ICR1 = 2 << 30

配置IMR寄存器:中斷屏蔽寄存器,每個IO對應一個位,用于控制GPIO的中斷使能和禁止

例如要使能GPIO1_IO00的中斷,則GPIO1.MIR=1

配置ISR寄存器:中斷狀態(tài)寄存器,每個IO對應一個位,只要某個GPIO的中斷發(fā)生,ISR中相應的位會被置1

可通過讀取ISR寄存器來判斷GPIO中斷是否發(fā)生,相當于中斷標志位。 處理完中斷后,必須清除中斷標志位

配置EDGE_SEL寄存器:邊沿選擇寄存器,每個IO對應一個位,用來設置邊沿中斷, 并會覆蓋ICR1和ICR2的設置

若相應位被置1,相當于設置了對應GPIO雙邊沿(上升沿和下降沿)觸發(fā)。 例如,設置GPIO1.EDGE_SEL=1,則表示雙邊沿觸發(fā)中斷,無論 GFPIO1_CR1的設置為多少

3. GPIO配置總結

綜上所述,i.MX6ULL的IO作為GPIO使用,需要進行以下幾個步驟的配置:

- 使能GPIO對應的時鐘

- 配置MUX寄存器,設置IO的復用功能,使其復用為GPIO功能

- 配置PAD寄存器,設置IO的上下拉、速度等

- 配置GPIO的各種寄存器,設置輸入/輸出、是否使用中斷、默認輸出電平等

裸機開發(fā)中,需要自已定義寄存器及其地址,通常代碼如下:

/* 寄存器物理地址 */

#define CCM_CCGR1_BASE (0X020C406C)

#define SW_MUX_SNVS_TAMPER3_BASE (0X02290014)

#define SW_PAD_SNVS_TAMPER3_BASE (0X02290058)

#define GPIO5_DR_BASE (0X020AC000)

#define GPIO5_GDIR_BASE (0X020AC004)

-

處理器

+關注

關注

68文章

19265瀏覽量

229671 -

寄存器

+關注

關注

31文章

5336瀏覽量

120249 -

Linux

+關注

關注

87文章

11296瀏覽量

209358 -

開發(fā)板

+關注

關注

25文章

5035瀏覽量

97384 -

GPIO

+關注

關注

16文章

1204瀏覽量

52059

發(fā)布評論請先 登錄

相關推薦

i.MX6ULL 驅動開發(fā)7—按鍵輸入捕獲與GPIO輸入配置與高低電平讀取

I.MX6ULL終結者開發(fā)板裸機仿真jlink調試

i.MX6ULL核心板資源

I.MUX6ULL的初始化方法

ARM裸機篇之i.MX6ULL處理器資料分享

關于i.MX6ULL配置GPIO

飛凌i.MX6ULL開發(fā)板的評測,再次進階擁有更高的性價比

基于NXP i.MX6ULL處理器的FETMX6ULL-C核心板

基于i.MX6ULL應用處理器的FETMX6ULL-C核心板

【i.MX6ULL】驅動開發(fā)4——點亮LED(寄存器版)

使用pinctrl和gpio子系統(tǒng)實現(xiàn)LED燈驅動

基于i.MX6ULL的掉電檢測設計與軟件測試

i.MX6ULL處理器GPIO寄存器配置原理及方法

i.MX6ULL處理器GPIO寄存器配置原理及方法

評論