你認為你的射頻 (RF) 采樣設計運行的還不錯,其原因在于你選擇了合適的器件,并且定義了時鐘源。不過先等一等;你所要完成的工作還遠非如此。在不進行適當的頻率規劃,以確保諧波或時鐘混合雜散中產生出潔凈頻譜的情況下,即使是最好的器件也會造成性能下降。我在上一篇博文中討論了與交錯轉換器有關的某些缺陷。頻率規劃始終是良好收發器設計的一部分,不過RF采樣更加關鍵,這是因為信號一直處于所需的頻率頻帶范圍內。與其它具有中間頻率 (IF) 或基頻級 (BB) 的配置不同,RF采樣架構不具有清潔頻譜的窄頻帶通道濾波功能。

在這些發射器中,管理要求將嚴格限制雜散乘積的等級,使其落在所需頻帶內,并且剛好在頻帶外。這些轉換器內產生的雜散乘積在到達功率放大器 (PA) 之前無法被有效過濾掉。一旦受到輻射,這些乘積就有可能干擾其它用戶。

用一個RF采樣數模轉換器 (DAC) 進行的頻率規劃確保了折返回第一那奎斯特區域內的諧波含量不在所需頻帶之內,或者在其附近。針對指定應用的頻帶是固定的;它是不可調節的,不過你可以調節轉換器的采樣率。增加采樣速率可以生成一個更大的那奎斯特區域;然而,這并不能確保一個最優方案。

發射器頻率規劃示例

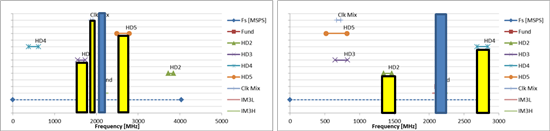

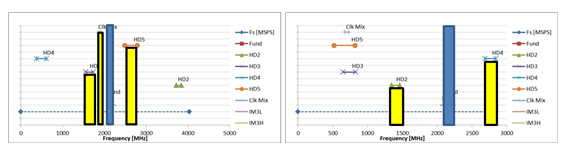

我們來看一個發射器示例,它的運行頻率為2.14GHz,信號寬度為60MHz。圖1顯示的是具有8024MHz高頻時鐘速率的第一那奎斯特區域頻譜。在這個速率下,所需要的頻帶(用藍色標出)很清楚,但是第三和第四階諧波,以及已知的雜散(用黃色標出)位于所需的頻帶附近。這些雜散積很難被過濾掉。

圖1b顯示的是同一頻率,不過時鐘速率減少為5683.2MHz。在這個時鐘速率下,高階諧波或者時鐘混合雜散都不會位于所需頻帶的附近。在這個示例中,較低采樣率方法比較適用,這是因為你可以輕松地將高階雜散濾除掉。

圖1:時鐘頻率為8024MHz (a) 和5683.2MHz (b) 時的頻譜圖

接收器頻率規劃示例

對于接收器來說,頻率規劃目標稍微不同。源自帶內和帶外信號的干擾會嚴重影響接收器的靈敏度。通過在RF輸入端上進行適當的限帶濾波,你可以最大限度地降低其它用戶信號或發射器干擾所形成的帶外干擾源。你無法過濾掉帶內干擾源。頻率規劃確保來自帶內干擾源的諧波含量不會折返回所需頻帶的內部。與發射器的情況不同,恰恰折返回頻帶外部的諧波含量不是一個問題。

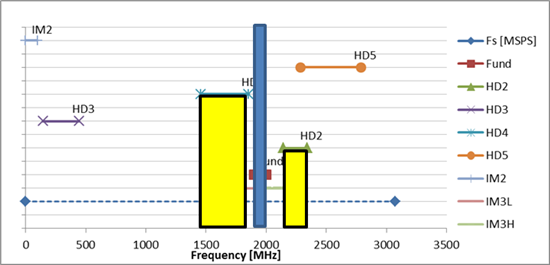

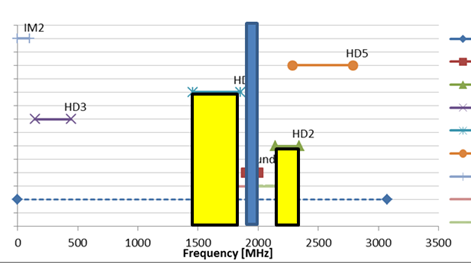

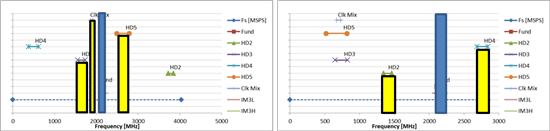

圖2顯示的是一個100MHz寬的信號,在中央頻率為1950MHz的頻帶范圍內運行。時鐘頻率為6144MHz。在這個配置中,所有這些較高階諧波都位于頻帶外部。第二和第四諧波很接近,但是不在頻帶內部。這是一個傳統低IF架構所不能比擬的。使用同樣信號帶寬運行的較低采樣率模數轉換器 (ADC) 無法實現一個干凈的頻譜,這是因為折返諧波覆蓋了整個那奎斯特區域。

圖2:時鐘頻率為6144MHz,中央頻率1950MHz頻帶范圍內,頻帶寬度為100MHz時的頻譜圖

你可以修改時鐘頻率來在所需頻率發生變化時保持一個潔凈頻譜。在使用傳統架構時,對于頻率規劃的調整需要你修改合成器和IF或基帶濾波器級。只需調節采樣率,RF采樣架構就可實現簡單頻率規劃調整。由于在不同頻帶下運行只需要對時鐘頻率進行調節,RF采樣架構可以很輕松地適應不同頻帶和應用的要求。

審核編輯:郭婷

-

轉換器

+關注

關注

27文章

8724瀏覽量

147415 -

dac

+關注

關注

43文章

2299瀏覽量

191204 -

RF

+關注

關注

65文章

3055瀏覽量

167114

發布評論請先 登錄

相關推薦

用一個RF采樣數模轉換器進行的頻率規劃

做頻譜圖,怎樣能將橫坐標變成采樣頻率

用一個RF采樣數模轉換器 (DAC) 進行的頻率規劃

我國明確TD-LTE頻率規劃 頻譜是TD-SCDMA數倍

頻率規劃產生潔凈頻譜

多頻段射頻采樣接收器參考設計

射頻采樣設計 發射器頻率規劃示例

頻率規劃技術可消除頻譜中的干擾雜散信號

射頻接收系統:中頻采樣和IQ采樣的比較和轉換

射頻采樣:頻率規劃產生潔凈頻譜介紹

射頻采樣:頻率規劃產生潔凈頻譜

射頻采樣:頻率規劃產生潔凈頻譜

評論