車輛在動態稱重時,作用在平臺上的力除真實軸重外,還有許多因素產生的干擾力,如:車速、車輛自身諧振、路面激勵、輪胎驅動力等,給動態稱重實現高 測量造成很大困難。若在消除干擾的過程中采用模擬方法濾波,參數則不能過大,否則將產生過大的延遲導致不能實現實時處理,從而造成濾波后的信號仍然含有相當一部分的噪聲。所以必須采用數字濾波消除干擾。

FIR濾波的原理及實現

本文采用FIR數字濾波,其原理如公式1所示。

Y(n)=(1)

其中h(k)為系統濾波參數,x(n)為采集的信號,Y(n)為濾波后的輸出信號。

FIR濾波器的h(n)0≤n≤N-1

H(z)=(2)

在本文中N=17。由于h(n)具有對稱性質,即:

h(n)=h(N-1-n)(n=0,1,。..,(N-1)/2)(3)

這樣就可以把FIR濾波器設計成具有線性相位。利用這一情況,可以得到的乘法結構,需要(N+1)/2次乘法,僅是級聯或并聯結構所需次數的一半,因此,實際應用中多采用此方法。

我們選用17點的FIR濾波算法,這樣實現 FIR卷積運算需要執行9次乘法和16次加法。為了實現數據的實時處理,需要在20ms內完成這個卷積運算,如果選用單片機89C51(12M晶振)則無法實現。所以我們選用了Altera公司的FLEX10K20。FLEX10K系列是工業界 個嵌入式的PLD,采用重復可構造的CMOSSRAM工藝,把連續的快速通道互連與獨特的嵌入式陣列結構相結合,同時也結合了眾多可編程器件的優點來完成普通門陣列的宏功能。具有高密度、低成本、低功率等特點。

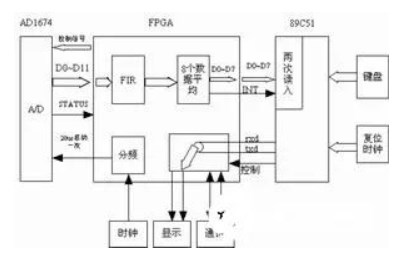

圖1硬件結構框圖硬件設計

由于我們選用的AD1674芯片轉換時間為10ms,而所設計的電路每隔20ms啟動轉換 ,所以有足夠的時間完成模數轉換。軸重臺的寬度為40cm,汽車通過軸重臺的 速度為15km/h,通過計算可知在這段時間里系統可采集4800個數據。由于前30ms是傳感器的反應時間,將剩下的數據進行FIR數字濾波后,噪聲會被有效的抑制。為了進一步平滑波形,對每8個數據做 平均,這樣就消弱了由于汽車高速通過軸重臺時由于顛簸產生的尖峰信號。FPGA的每次濾波包含有FIR運算和8個數據的平均值運算,完成 濾波就會向單片機發一個中斷請求,此時單片機讀取濾波后的數據。由于我們選用的A/D轉換器是12位,而單片機89C51是8位的,所以經過處理后的數據必須分兩次讀入。 次讀入低8位,第二次讀入高4位,然后對數據處理。此時我們可以認為單片機接收的數據為濾波后不含有噪聲的數據。根據軸重稱量的波形圖可以知道,只要求出此時的 值就是汽車的真實重量。

在此儀表中,串行口即用來顯示也用來通訊,我們可以通過FPGA很容易實現切換。如圖1所示,當控制信號為1的時候RXD、TXD用于顯示,而當控制信號為0的時候用于和上位機通訊。

我們選用加海明窗的理想低通濾波器,其歸一化截至頻率為0.25,如圖2所示。汽車稱重信號為含有多種成分噪聲的直流信號如圖3所示,這1000個數據經過FPGA的FIR濾波和8點數據平均后,提供給單片機125個數據

濾波之前的噪聲的峰峰值在0.1V左右,而此時的軸重信號為1,這將嚴重影響測量 。濾波后我們看到情況得到了明顯的改善,噪聲信號的峰峰值被抑制在0.02V的范圍內,大大改善了信噪比,從而提高了測量 。

結語

本設計不但實現了硬件數字濾波電路,而且減少了許多門電路和組合邏輯電路。用比較少的器件實現了比較復雜的功能,減少了故障率。用此方法設計的汽車動態稱重儀表具有良好的實時性和較高的 ,現已投入批量生產。

審核編輯:劉清

-

FPGA

+關注

關注

1635文章

21837瀏覽量

608330 -

濾波電路

+關注

關注

47文章

639瀏覽量

69968 -

數字濾波電路

+關注

關注

0文章

2瀏覽量

5655 -

FIR濾波

+關注

關注

0文章

6瀏覽量

9878 -

AD1674

+關注

關注

0文章

12瀏覽量

20665

原文標題:基于FPGA實現FIR數字濾波電路的設計及應用

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

使用FPGA構建的數字濾波器設計方案

基于FPGA實現FIR數字濾波電路的設計及應用

基于DSP的FIR 數字濾波器設計

基于FPGA的FIR濾波器設計與實現

基于FPGA的FIR數字濾波器該怎么設計?

基于FPGA的FIR數字濾波器的優化設計

FPGA是如何設計并實現了32階FIR數字濾波器的硬件電路?

FIR數字濾波器設計

基于FPGA實現FIR數字濾波器

基于FPGA實現FIR數字濾波電路的設計及應用

基于FPGA實現FIR數字濾波電路的設計及應用

評論