當談到模擬信號鏈時,每個人都明白輸入信號路徑的重要性。我們設計自己的系統,以獲取值得關注的信號并保持其完整性,同時竭盡全力來避免或減少干擾。我們特別留意沿途所置各組件的選擇。。.。。.然后我們就給其供電。

曾聽人把電源形容成“電路的鞋帶。”像電路一樣,人們常為鞋子的設計和款式做大量艱苦的工作,卻直到最后才會想起鞋帶。雖然電源往往是后添加的東西,但它們的設計可能正如信號鏈本身一樣重要。

在本系列的第一部分,將介紹電源抑制(PSR)的概念,并說明電源如何能影響Δ-Σ型模數轉換器(ADC)的性能。

直流(DC)電源“固如磐石”,對嗎?

您的電源也許并不如您想象的那樣堅固耐用,信不信由您。從DC的角度來看,組件容差和溫度漂移都可能導致您的電源輸出因電路板不同和溫度變化而發生變化。輕微的變化似乎無關緊要(如果它仍在您ADC的工作條件范圍內),但這可能會在ADC傳輸函數中產生額外的偏移和增益誤差。

電源也可能噪聲很大。根據它們的來源或周圍環境,DC電源還可支持交流(AC)組件。

我們都熟悉由50Hz/60Hz電源線引起的令人頭痛的頑疾(比喻)。電源線噪聲往往能找到一種途徑,可通過照明或附近設備耦合而入,即便是電池供電型應用也難幸免。對某些應用而言,這種噪聲可直接進入到您值得關注的信號帶寬范圍內。

此外,較復雜的系統還可用開關DC/DC轉換器來讓自己的電源“降壓”或“升壓”,從而變成另一種電壓,這樣就能由單個電源產生多個電源。這些開關電源的頻率存在范圍也許遠遠超出了值得關注的信號帶寬范圍,但這些頻率有可能混疊回通帶中。這會直接影響重要的AC技術參數,如信噪比(SNR)和無雜散動態范圍(SFDR)。

ADC需要穩定的純DC電源,因此該電源中的任何變化均有可能改變ADC的性能。像大多數有源組件一樣,ADC經設計具備一些固有的抗電源變化能力,但有一點至關重要 —— 那就是要對該能力進行量化,看它是否足以讓您的應用正常運行。

ADC對其電源的易感程度如何?

ADC PSR描述了ADC輸出變化與其電源變化的相關性。有時它被指定為一個比值,稱為電源抑制比(PSRR),用分貝(dB)來表示。TI的Δ-Σ型ADC通常采用兩種方式來指定PSRR:PSRRDC和PSRRAC。

PSRRDC可衡量ADC對電源中DC位移的抑制能力。為了測定PSRRDC,您要將ADC輸入短接在一起并把它們偏置到中間電源,如圖1所示。然后,您通過一個干凈的DC電源為模擬ADC電源(AVDD)供電,并記錄輸出端的偏移電壓。當您將電源電壓增加或減少100mV時,記錄您在ADC輸出端觀察到的任何變化。圖2展示了電源電壓中100mV的變化如何讓ADS1220中的初始偏移電壓發生了562nV的變化。

PSRRAC可衡量ADC的電源噪聲或紋波抑制能力。為了測定PSRRAC,您要讓ADC輸入短接在一起并偏置到中間電源,同時將一個100mVpp的正弦波(VIN)添加到DC電源。偏移電壓等于所需電源電壓的AC信號發生器正可一用。對于值得關注的頻率,您可記錄用快速傅立葉變換(FFT)算法計算輸出數據得出的基調振幅,并用方程式2算出PSRRAC。對ADS1278而言,要憑借2.5V的參考電壓和24位的分辨率將一個振幅為100mV的紋波從滿量程轉變到-28dB。如果該電源紋波具有60Hz的頻率,那么ADS1278將使該紋波再衰減-80dB,從而讓60Hz頻率下的輸出量值降至-108dB。產品說明書通常為電氣特性表中50Hz和60Hz的頻率以及典型特性圖中的所有其它頻率(高達100kHz或1MHz)提供PSRRAC規格。

正如前面所提,大多數ADC均有一定的PSR水平(基于它們的設計方式)。對于需要更強PSR能力的應用,本系列的下一篇文章將討論在您的系統中提高PSR水平的方法。

審核編輯:郭婷

-

電源

+關注

關注

184文章

17704瀏覽量

249965 -

電路板

+關注

關注

140文章

4951瀏覽量

97694 -

adc

+關注

關注

98文章

6495瀏覽量

544469

發布評論請先 登錄

相關推薦

5962-9581501HXA高端AD模數轉換器

為什么我們需要模數轉換器?哪個ADC轉換器更好?

溫度測量系統對模數轉換器的要求

溫度測量系統對模數轉換器的要求

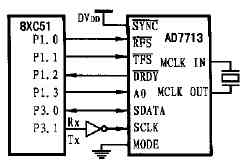

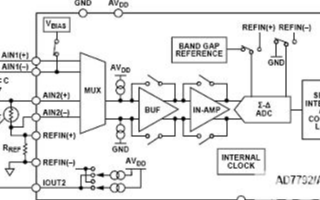

24位模數轉換器AD7713及其應用

電流積分模數轉換器(ADC),什么是電流積分模數轉換器(AD

注意!您的模數轉換器是好是壞可能只取決于它的電源

如何利用模數轉換器接地技術提高系統性能的詳細概述

您的模數轉換器是好是壞可能只取決于它的電源

您的模數轉換器是好是壞可能只取決于它的電源

評論