在Verilog中,IC設計工程師使用RTL構造和描述硬件行為。但是RTL代碼中的一些語義,并不能夠準確地為硬件行為建模。Verilog中定義了4種不同的邏輯值:1、0、X和Z,1和0是真實存在的邏輯電平,Z表示高阻態,X表示未知態。

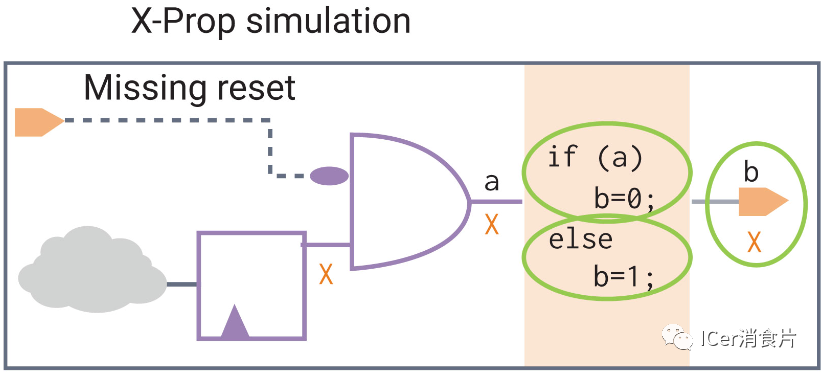

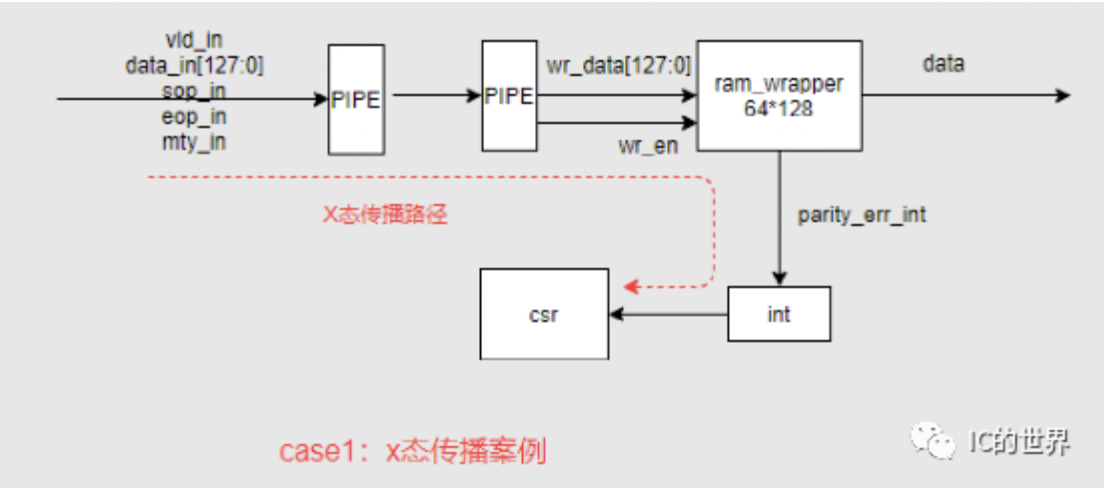

X態的存在使得仿真結果要么太過于樂觀,要么太過于悲觀。因此X態如何通過RTL級和門級仿真模型中的邏輯進行傳播的,是需要特別關注的。為此,還產生了兩種觀念,X-optimism和X-pessimism。前者將X值轉換為0或1,后者將X值一直傳播出去。

X態產生的原因主要分為以下幾種情況:

四值變量、寄存器和鎖存器未初始化

模塊輸入端口未連接

總線爭用

超出范圍的位選擇和數組索引

setup/holdtiming violation

testbench中注入X態

VCS對于RTL仿真提供了支持X-Propagation的選項,因為RTL仿真偏向于樂觀,導致一些X態傳播的bug,無法在正常的RTL仿真階段發現。但是在Gate-level仿真時會暴露出來,因為Gate-level仿真也更接近實際硬件行為。

我們知道越早的發現bug,所消耗的成本也越低的,故VCS的X-Propagation功能可以更接近Gate-level的X態傳播行為,是一種在后仿之前debug的低成本仿真策略。

通常使用帶xprop的仿真選項為:

vcs -xprop[=tmerge|xmerge|xprop_config_file]

[-xprop=flowctrl]

[-xprop=nestLimit=

other_vcs_options

這里就不深入介紹各個選項了,而是介紹三種merge mode:

vmerge mode: 就是Verilog協議規定的X態處理行為;

tmerge mode: 更接近Gate-level仿真,也就是實際硬件行為;

xmerge mode: 相比tmerge mode,對于X態的處理更悲觀;

下面舉幾個實例來看看這三種mode的具體區別

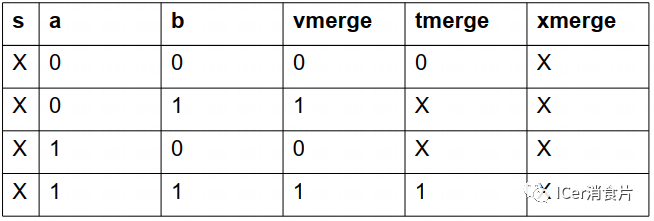

if語句

always @* if(s) r=a; else r=b;

在vmerge模式下,使用標準的HDL模擬語義。當控制信號s未知時,輸出信號r總是被賦給else語句的值。此時r的值與信號b相同。

在tmerge模式下,當控制信號s未知時,如果輸入信號a和b 同,則r的值與a(或b)相同。如果a和b不相同,則r的值為X。

在xmerge模式下,當控制信號s未知時,輸出信號r的值始終為X。

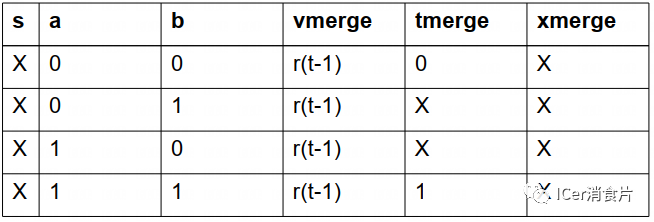

case語句

case (s) 1'b0:r=a; 1'b1:r=b; endcase

在vmerge模式中,使用標準的HDL模擬語義。當控制信號s未知時,輸出信號r的值與執行case語句之前保持一致。

在tmerge模式中,當控制信號s未知時,如果a和b相同,r的合并和最終值與a和b 相同。如果a和b不相同,r的合并和最終值為X。

在xmerge模式下,當控制信號s未知時,輸出信號r的值始終為X。

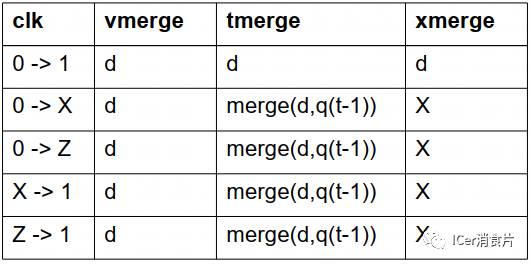

邊沿敏感表達式

在標準的 Verilog 中,對于時鐘信號中以下值的變化會觸發上升沿轉換:

0->1 0->X 0->Z X->1 Z->1

如果X被認為是0或1值,那么在 0 -> X 轉換中,X可能表示0值,這表示沒有轉換。X可以表示1值,此時表示上升沿。Xprop仿真考慮了這兩種行為并合并了結果。

以下為一個低有效復位的D觸發器示例:

在三種模式中,如果時鐘信號clk從0變成1,即一個上升沿觸發,D觸發器的輸出信號q被賦值為輸入信號d。

對于其余四種時鐘信號的變化,vmerge模式中,輸出信號q被賦值為輸入信號d;xmerge模式中,輸出信號q被賦值為X;tmerge模式中,q端的結果是當前拍d端和上一拍q端值得merge的結果,如果兩者不同,則當前拍鎖存X。

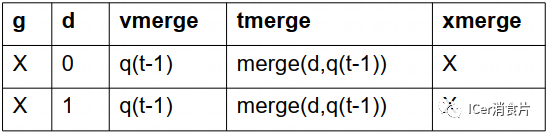

latch

always@(*) if(g) q <= d;

在vmerge模式下,當控制信號g未知時,輸出信號q的值不變。

在tmerge模式下,當控制信號g未知時,分配給q的合并值取決于q和d的值。

在xmerge模式下,當控制信號g未知時,輸出信號q的值始終為X。

當xprop仿真過程中出現X態報錯時,需要看波形以具體分析是寄存器沒有初始化值,存在X態導致的,還是代碼邏輯中存在問題導致的。

審核編輯:劉清

-

IC設計

+關注

關注

38文章

1306瀏覽量

104555 -

Verilog

+關注

關注

28文章

1355瀏覽量

110864 -

RTL

+關注

關注

1文章

386瀏覽量

60183 -

VCS

+關注

關注

0文章

80瀏覽量

9698

原文標題:什么是X態傳播?

文章出處:【微信號:處芯積律,微信公眾號:處芯積律】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

RTL級設計的基本要素和步驟是什么

X態如何通過RTL級和門級仿真模型中的邏輯進行傳播呢?

X態如何通過RTL級和門級仿真模型中的邏輯進行傳播呢?

評論