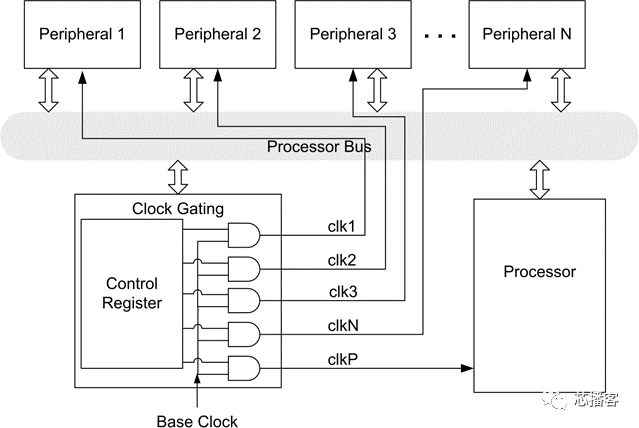

門控時(shí)鐘是一種在系統(tǒng)不需要?jiǎng)幼鲿r(shí),關(guān)閉特定塊的時(shí)鐘的方法,目前很多低功耗SoC設(shè)計(jì)都將其用作節(jié)省動(dòng)態(tài)功率的有效技術(shù)。在SoC設(shè)計(jì)中,時(shí)鐘門控可以在兩個(gè)級(jí)別完成:

1. 門控時(shí)鐘被設(shè)計(jì)到SoC架構(gòu)中,并被編碼為RTL功能的一部分。當(dāng)這些相關(guān)的模塊處于非激活狀態(tài)時(shí),它會(huì)停止各個(gè)模塊的時(shí)鐘,從而有效地禁用這些塊的所有功能。由于大的邏輯塊在這些非激活的時(shí)鐘周期內(nèi)都不進(jìn)行切換和運(yùn)算操作,因此節(jié)省了大量的動(dòng)態(tài)功率。時(shí)鐘門控的最簡(jiǎn)單和最常見的形式是使用邏輯“與”功能通過控制信號(hào)enable選擇性地禁用各個(gè)塊的時(shí)鐘。 ? ? ?

? ? ?

2. 在綜合期間,相關(guān)工具自動(dòng)識(shí)別共享公共使能控制信號(hào)的觸發(fā)器組,并使用它們選擇性地關(guān)閉這些觸發(fā)器組的時(shí)鐘。

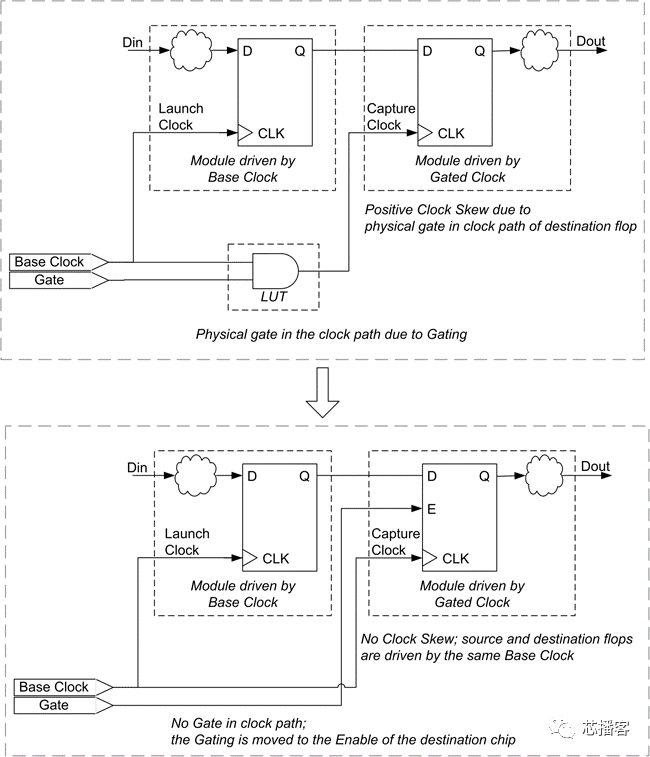

這兩種時(shí)鐘門控方法最終都將在控制其下游時(shí)鐘的時(shí)鐘路徑中引入具體物理邏輯門。即使映射到SoC中,這些邏輯門也可能會(huì)引入額外的時(shí)鐘偏差,并導(dǎo)致設(shè)置和保持時(shí)間沖突,然而,這可以通過SoC后端STA流程或者其他手段的時(shí)鐘樹綜合和布局工具來補(bǔ)償。SoC設(shè)計(jì)的時(shí)鐘樹綜合平衡了源和目的地之間的時(shí)鐘緩沖、分段和布線,以確保定時(shí)關(guān)閉,使這些路徑包括時(shí)鐘門控。這在FPGA技術(shù)中是不可能的,因此如果SoC設(shè)計(jì)包含大量門控時(shí)鐘或復(fù)雜的時(shí)鐘網(wǎng)絡(luò),則需要其他一些方法來映射SoC設(shè)計(jì)。

所有FPGA設(shè)備都有專用的低偏斜時(shí)鐘樹網(wǎng)絡(luò),稱為全局時(shí)鐘。它們的數(shù)量有限,但它們可以計(jì)時(shí)FPGA中的順序資源,頻率為數(shù)百兆赫。由于FPGA供應(yīng)商的精湛設(shè)計(jì)技術(shù),時(shí)鐘網(wǎng)絡(luò)在FPGA中的任意兩個(gè)目的地之間也只有幾十皮秒的偏差。因此,當(dāng)我們將設(shè)計(jì)目標(biāo)定為FPGA時(shí),始終建議使用這些全局時(shí)鐘。然而,F(xiàn)PGA時(shí)鐘資源不適合創(chuàng)建大量相對(duì)較小的時(shí)鐘域,如我們通常在SoC中發(fā)現(xiàn)的那樣。相反,F(xiàn)PGA更適合于實(shí)現(xiàn)少量的大型同步時(shí)鐘網(wǎng)絡(luò),這些網(wǎng)絡(luò)可以被認(rèn)為是整個(gè)設(shè)備的全局網(wǎng)絡(luò)。

全局時(shí)鐘網(wǎng)絡(luò)非常有用,但可能不夠靈活,無法滿足復(fù)雜SoC設(shè)計(jì)的時(shí)鐘需求,尤其是在RTL中執(zhí)行時(shí)鐘門控時(shí)。這是因?yàn)槲锢黹T被時(shí)鐘門控過程引入時(shí)鐘路徑,并且全局時(shí)鐘線不能自然地容納這些物理門。因此,布局布線工具將被迫為具有插入門的時(shí)鐘網(wǎng)絡(luò)使用其他片上路由資源,通常導(dǎo)致到目標(biāo)寄存器的不同路徑之間的大的時(shí)鐘偏移。

當(dāng)在SoC中采用架構(gòu)級(jí)時(shí)鐘門控時(shí),例如當(dāng)為時(shí)鐘使用粗粒度開關(guān)控制以減少動(dòng)態(tài)功耗時(shí),可能會(huì)出現(xiàn)這種情況。在這些情況下,可以將門控時(shí)鐘的所有負(fù)載劃分到同一FPGA中,并從同一時(shí)鐘驅(qū)動(dòng)器塊驅(qū)動(dòng)它們。在一些SoC設(shè)計(jì)中,設(shè)計(jì)中也可能存在跨時(shí)鐘域的設(shè)計(jì),即源和目標(biāo)觸發(fā)器由不同相關(guān)時(shí)鐘驅(qū)動(dòng)的路徑,例如,時(shí)鐘和由時(shí)鐘路徑中的物理門創(chuàng)建的導(dǎo)出門控時(shí)鐘,如圖所示。來自源觸發(fā)器的數(shù)據(jù)很可能比門控時(shí)鐘更快/更晚到達(dá)目的地觸發(fā)器,并且這種競(jìng)爭(zhēng)條件可能導(dǎo)致定時(shí)沖突。 ? ? ?

? ? ?

上述競(jìng)爭(zhēng)條件的解決方案是將基準(zhǔn)時(shí)鐘和選通與選通時(shí)鐘分開。然后將分離的基本時(shí)鐘路由到時(shí)鐘,并選通到時(shí)鐘使能所有順序元件。當(dāng)時(shí)鐘“打開”時(shí),順序元件將被啟用,當(dāng)時(shí)鐘“關(guān)閉”時(shí),序列元件將被禁用。通常,許多門控時(shí)鐘來自同一基準(zhǔn)時(shí)鐘,因此將門控與時(shí)鐘分離允許單個(gè)全局時(shí)鐘線用于許多門控時(shí)鐘。這樣,功能時(shí)鐘路徑中存在的邏輯門被移動(dòng)到數(shù)據(jù)路徑中,這消除了時(shí)鐘偏移。

這個(gè)過程稱為門控時(shí)鐘轉(zhuǎn)換。FPGA中的所有順序元件都有專用的時(shí)鐘使能輸入,因此在大多數(shù)情況下,門控時(shí)鐘轉(zhuǎn)換可以使用這一點(diǎn),而不需要任何額外的FPGA資源。然而,手動(dòng)將門控時(shí)鐘轉(zhuǎn)換為等效啟用是一個(gè)困難且容易出錯(cuò)的過程,盡管如果SoC設(shè)計(jì)中的時(shí)鐘門控都在設(shè)計(jì)層次結(jié)構(gòu)中的同一位置執(zhí)行,而不是分散在各個(gè)子功能中,則可能會(huì)稍微容易一些。

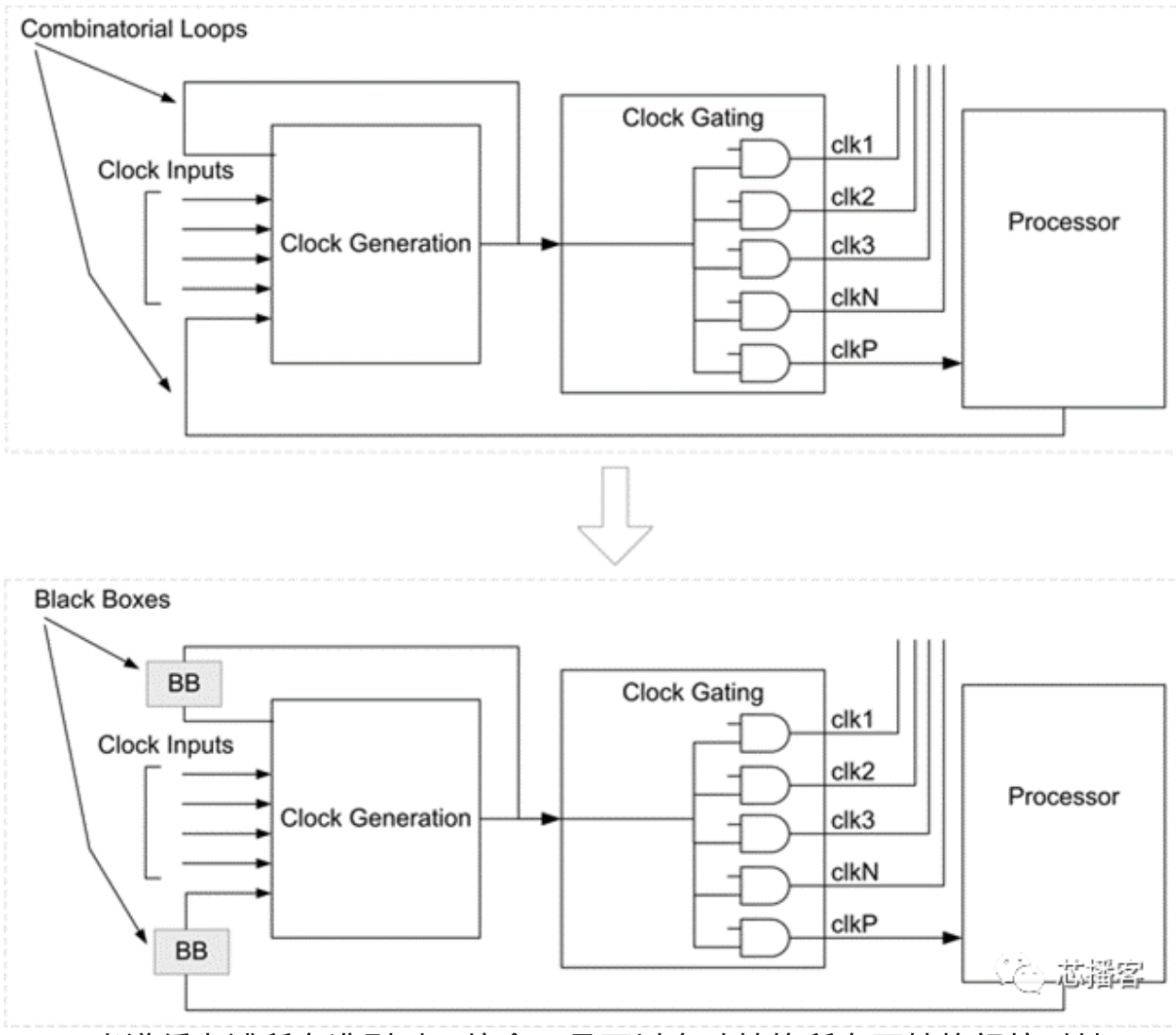

頂層的芯片支持塊可以包括驅(qū)動(dòng)整個(gè)SoC所需的所有時(shí)鐘生成和時(shí)鐘門控。然后,在原型設(shè)計(jì)期間,可以用其FPGA等效邏輯替換該Chip Support模塊。同時(shí),我們可以手動(dòng)將時(shí)鐘門替換為啟用信號(hào),該啟用信號(hào)可以在整個(gè)設(shè)備中路由。

然后,這將在原始門控時(shí)鐘每次上升時(shí)僅啟用全局時(shí)鐘的單個(gè)邊緣。在大多數(shù)情況下,由于復(fù)雜性,手動(dòng)操作是不可能的,例如,如果時(shí)鐘在RTL中的許多不同的始終或過程塊處被本地門控。在這種情況下,可能是大多數(shù)設(shè)計(jì)流程中的默認(rèn)情況,可以采用自動(dòng)門控時(shí)鐘轉(zhuǎn)換。

審核編輯:劉清

-

SoC設(shè)計(jì)

+關(guān)注

關(guān)注

1文章

148瀏覽量

18774 -

RTL

+關(guān)注

關(guān)注

1文章

385瀏覽量

59763 -

門控時(shí)鐘

+關(guān)注

關(guān)注

0文章

27瀏覽量

8948 -

FPGA系統(tǒng)

+關(guān)注

關(guān)注

0文章

10瀏覽量

7032

原文標(biāo)題:【芯知識(shí)】FPGA原型驗(yàn)證系統(tǒng)的時(shí)鐘門控

文章出處:【微信號(hào):于博士Jacky,微信公眾號(hào):于博士Jacky】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

驗(yàn)證中的FPGA原型驗(yàn)證 FPGA原型設(shè)計(jì)面臨的挑戰(zhàn)是什么?

FPGA的時(shí)鐘門控是好還是壞?

高頻RFID芯片的FPGA原型驗(yàn)證平臺(tái)設(shè)計(jì)及驗(yàn)證

基于FPGA原型的GPS基帶驗(yàn)證系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)

什么是門控時(shí)鐘 門控時(shí)鐘降低功耗的原理

門控時(shí)鐘實(shí)現(xiàn)低功耗的原理

如何建立適合團(tuán)隊(duì)的FPGA原型驗(yàn)證系統(tǒng)平臺(tái)與技術(shù)?

FPGA原型驗(yàn)證系統(tǒng)的時(shí)鐘資源設(shè)計(jì)

什么是FPGA原型驗(yàn)證?如何用FPGA對(duì)ASIC進(jìn)行原型驗(yàn)證

多臺(tái)FPGA原型驗(yàn)證平臺(tái)系統(tǒng)如何實(shí)現(xiàn)自由互連

淺析FPGA原型驗(yàn)證系統(tǒng)的時(shí)鐘資源

FPGA原型平臺(tái)門控時(shí)鐘自動(dòng)轉(zhuǎn)換

FPGA原型驗(yàn)證系統(tǒng)的時(shí)鐘門控

FPGA原型驗(yàn)證系統(tǒng)的時(shí)鐘門控

評(píng)論