現階段,電子系統正向高速化和高密度化飛躍發展。在電子系統的設計過程中, 系統的體積越來越小,IC引腳(integrated circuit,集成電路)卻越來越多,因此PCB (Printed Circuit Board,印制電路板)上的元件與布線越來越密集;與此同時,信號的 時鐘頻率越來越大,并且信號上升沿越來越陡峭。這些因素都導致了電磁環境的日益 復雜,設備之間以及設備內部因互感和互容引發的種種電磁兼容問題已不容忽視。

這一問題在現今的強輻射源與高功率微波系統中也顯得日益突出。如在某高功率微波系 統中,需要在限定的體積和尺寸下,采用FPGA芯片實現對多路電機的并行控制,就需要設計高速高密度的PCB。本文就研究該情況下PCB的板級電磁兼容問題,主要包括信號完整性(Signal Integrity, SI)和電源完整性(PowerIntegrity,PD問題。

二、信號完整性及電源完整性問題

信號完整性概括地說,是指信號在信號線上傳輸質量的好壞。在數字電路中,體 現在信號能在電路中能以正確的電壓、帶寬和時序做出響應。若在PCB中,信號可以以正確的電壓大小、帶寬和時序都到達接收端,就能說明該PCB具有較好的信號完整性。如果不能,則說明PCB中岀現了嚴重的信號完整性問題。

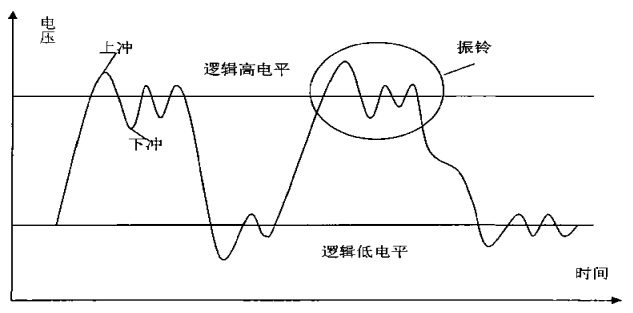

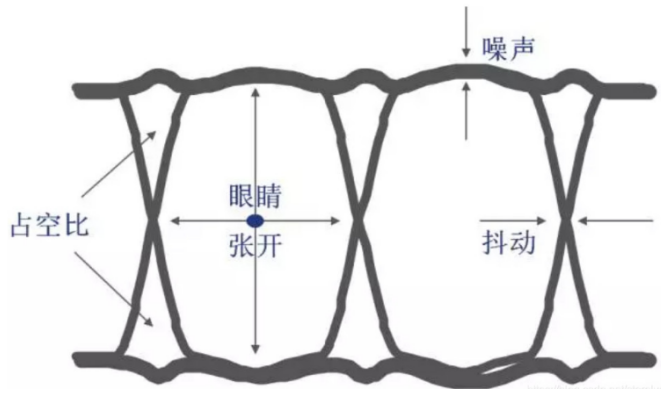

在高速高密度的數字電路中,信號完整性問題大致表現在一下幾個方面:振鈴、 過沖、欠沖和時延等。為了正確讀取數據并對數據進行處理,數據在集成電路中需要 在時鐘邊沿的前后處于穩定狀態。這個時間段內,如果信號不穩定或者發生狀態的改 變,集成電路就可能誤判甚至發生丟失部分數據的情況,影響信號的正常傳輸。如圖 1所示,若岀現振鈴、上沖或下沖等信號完整性問題,就會影響數據的正常傳輸,從 而影響PCB的正常工作,也可以從眼圖直觀判斷信號傳輸的好壞,如圖2

圖1PCB中信號完整性問題的表現

圖2 表征信號完整性問題的眼圖

信號完整性問題既會導致信號明顯的失真和時序混亂,也會造成數據的錯誤,從 而造成系統出錯甚至癱瘓。通常,在數字芯片中,高于VIH的電平被稱為邏輯“1”, 而低于VIL的電平被稱為邏輯“0”,在邏輯高電平與邏輯低電平之間的電平是不確定狀態。對于有振鈴的數字信號,當振蕩電平進入邏輯高電平與邏輯低電平之間的不確定區時,會引起邏輯錯誤。

為了保證電子系統的正常工作,數字信號要求了正確的時序。為了保證正確的邏輯時序,一般的數字芯片都要求信號需要在時鐘觸發邊緣到達前達到穩定。如果信號傳輸延時的部分太長,那么,在時鐘的上升沿或下降沿處就或許不能接收到正確的邏輯,將會引起錯誤的時序。引起信號完整性問題的因素有很多, 元器件的參數、PCB上元器件的布局、層疊結構、高速信號線在PCB±的如何布線等 都是影響信號完整性的關鍵因素。

電源完整性指的是信號傳播時電源的紋波質量。現階段電源完整性問題主要研究 的方面是同步開關噪聲(Simultaneous Switch Noise, SSN)。在數字電路中,工作過 程中的門電路會發生從高電平到低電平或者從低電平到高電平的轉換,從而造成瞬間 的變化電流A7o A/在流經返回路徑時會由于返回路徑的電感產生壓降,從而引起噪聲。如果在同一時刻有多個引腳發生狀態轉換,產生的壓降足以引起嚴重的電源完整性問 題。

電源完整性問題不僅僅關乎到PCB的饋電電壓,也影響了整個電子系統的設計。

電源分配網絡和各種互連結構構成了 PCB的主要噪聲耦合途徑。電源噪聲會在電源平 面/地平面腔體內產生諧振,并通過傳輸線、過孔等結構傳播,以電源平面/地平面上 返回路徑造成電壓壓降的形式破壞電源分配網絡或信號線的良好傳輸。主要的噪聲產 生源之一為高速數字元器件,高速數字元器件通過電源分配網絡與其它元件發生耦合, 這種耦合將會引起嚴重的PLL (Phase Locked Loop,鎖相環)抖動,繼而導致時序容 限和噪聲裕量的減小。

有些電壓噪聲發生在諧振頻點處,這還會在間接引起嚴重的電 磁干擾問題。由于超摩爾定律的不斷作用,在系統封裝尺寸減小的情況下,系統功率又逐步增大,復雜度越來越高,噪聲耦合也越來越強,因此在電子系統的設計中,設計要求更高。

在設計前期,仿真技術可以校核前期信號傳輸載體的合規性,通過前期仿真模擬可以有效減少后期樣品的電源信號完整性問題,一個集成電路,只要解決了信號電源完整性問題,EMC問題,從信號傳輸角度講,就解決了集成電路的高性能問題。

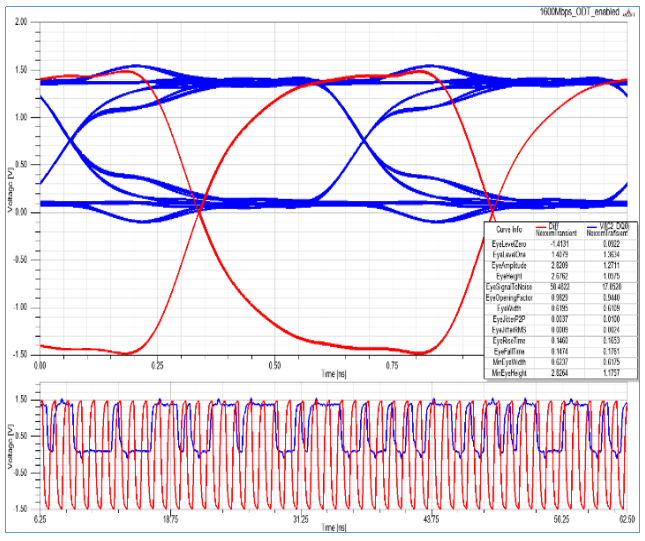

在前期集成電路預研階段,需要對已經設計的芯片封裝PCB做仿真模擬,信號完整性領域主要分析對象為高速/高頻信號、多負載信號網絡、復雜的信號通道結構。主要分析內容為反射、串擾、過沖/振鈴、通道阻抗、時序/抖動、損耗,對信號完整性影響要素繁多,包括:多負載拓撲、走線換層、參考層不連續、線間距過小、高密度連接器、差分線失配、走線過長、PCB板厚、材質選用、存在木樁、過孔大小、BGA出線、芯片封裝等等,在前期仿真模擬階段有大量的工作需要仿真模擬并校核。

時域眼圖

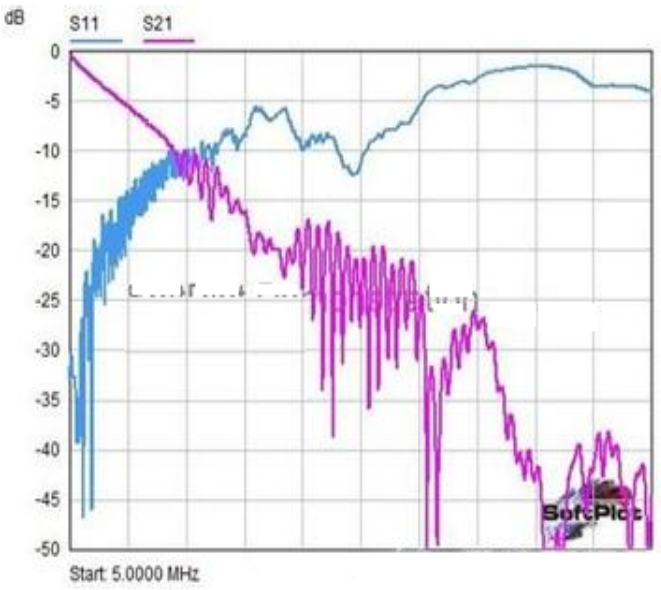

頻域S參數及插損

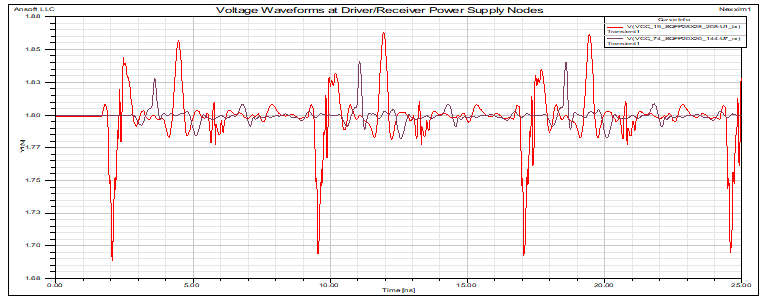

電源完整性領域主要分析對象有高速/高頻數字芯片的供電網絡、大電流低電壓電源網絡、數/模電路隔離,主要分析內容為:諧振分析、電源平面阻抗曲線、直流壓降/電流密度、頻域噪聲隔離度、電源地噪聲/SSN,影響電源完整性的要素主要有退耦電容容值、電容擺放位置、電容布線方式、芯片擺放位置、疊層設計情況、電源地層分配、電源地線寬度、換層過孔數量、數模隔離方式等等,往往對于一個復雜的PCB封裝系統,需要做多要素研究,研究不同要素對電源完整性影響大小。

電壓密度電壓跌落

電源紋波圖

審核編輯:劉清

-

集成電路

+關注

關注

5387文章

11534瀏覽量

361647 -

pcb

+關注

關注

4319文章

23081瀏覽量

397525 -

信號完整性

+關注

關注

68文章

1405瀏覽量

95458 -

emc

+關注

關注

170文章

3915瀏覽量

183128 -

電磁仿真

+關注

關注

2文章

76瀏覽量

19802

原文標題:我理解的ANSYS芯片-單板-整機SIPI、EMC電磁仿真解決方案

文章出處:【微信號:sim_ol,微信公眾號:模擬在線】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

PCB的板級電磁兼容問題

PCB的板級電磁兼容問題

評論