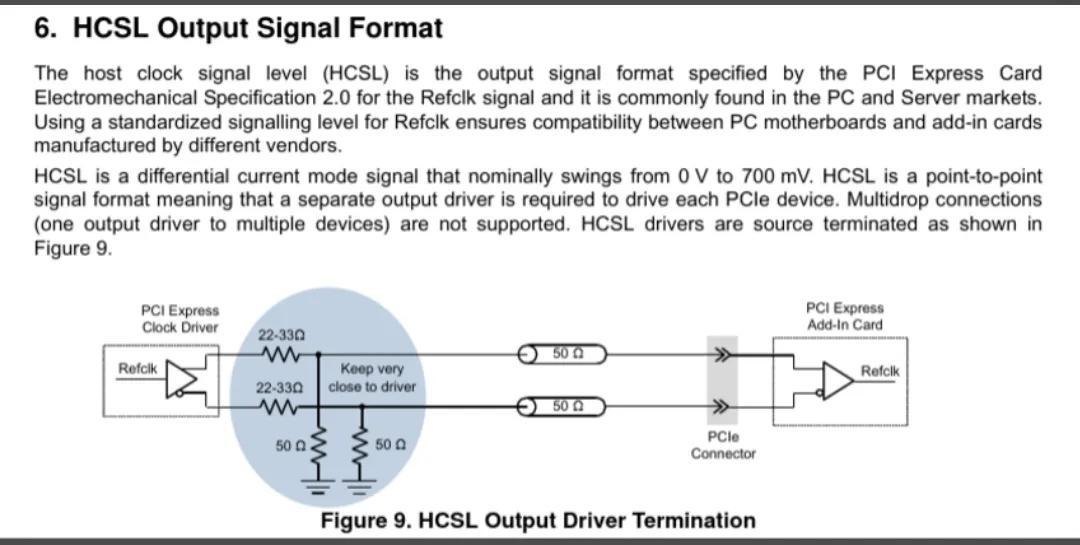

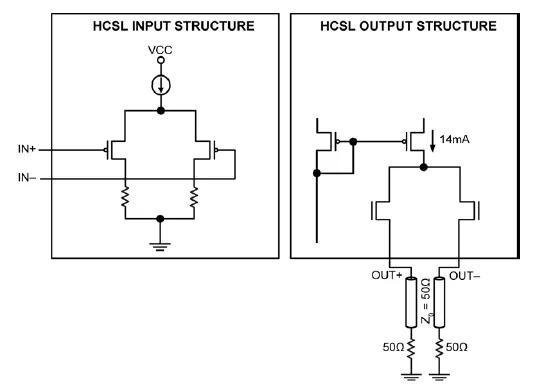

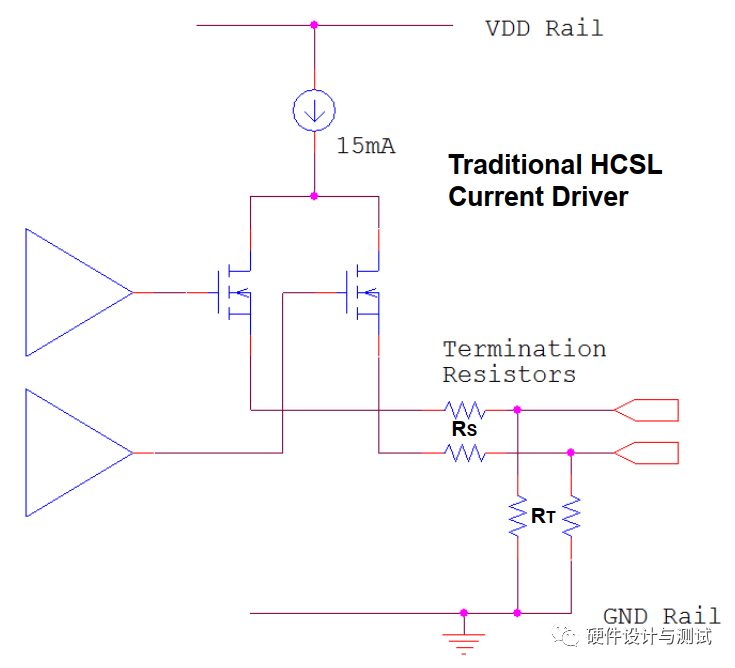

HCSL(HCSL--High?speed Current Steering Logic)一般用于PCIE參考時鐘的電平類型,根據(jù)規(guī)范需要下拉電路,如下圖HCSL之間的DC耦合。HCSL為電流輸出驅(qū)動,輸出結(jié)構(gòu)由通常通過50Ω電阻器接地的15 mA開關(guān)電流源驅(qū)動。 標(biāo)稱信號擺幅為750 mV。

HCSL規(guī)范

HCSL輸入輸出拓?fù)?/p>

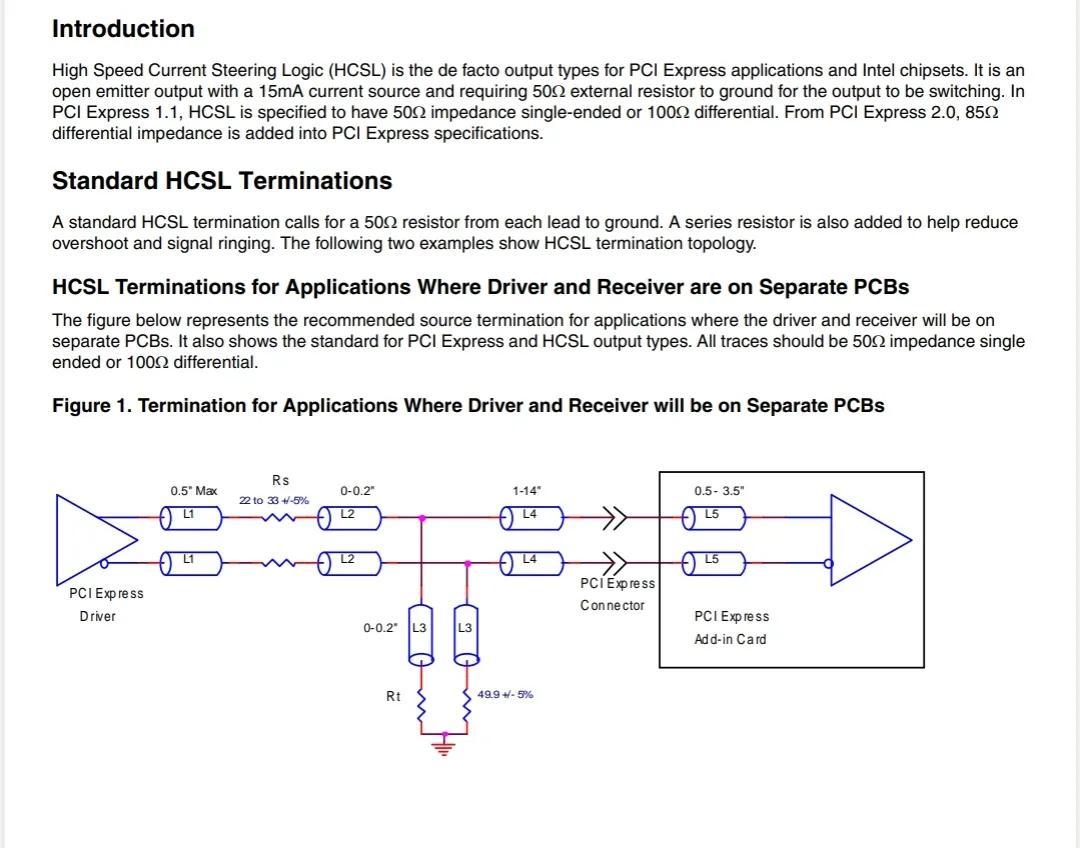

1-HCSL端接匹配

HCSL接口通常以50Ω負(fù)載源極端接,其中Rs大小一般為33Ω,匹配50Ω阻抗。 一般在輸出端位置。驅(qū)動器本身具有17歐姆的輸出阻抗,所以,需要串聯(lián)一個33歐姆的電阻,以獲得與50歐姆傳輸線的匹配。對于傳統(tǒng)的HCSL,為了避免出現(xiàn)過度的振鈴,串聯(lián)電阻RS是必須要的。

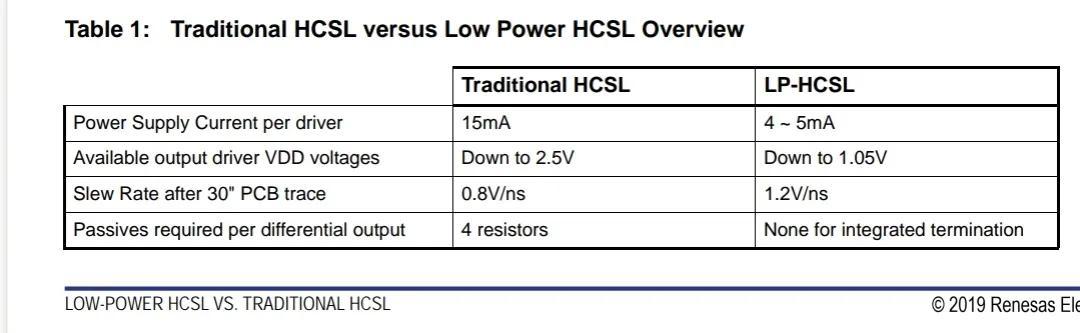

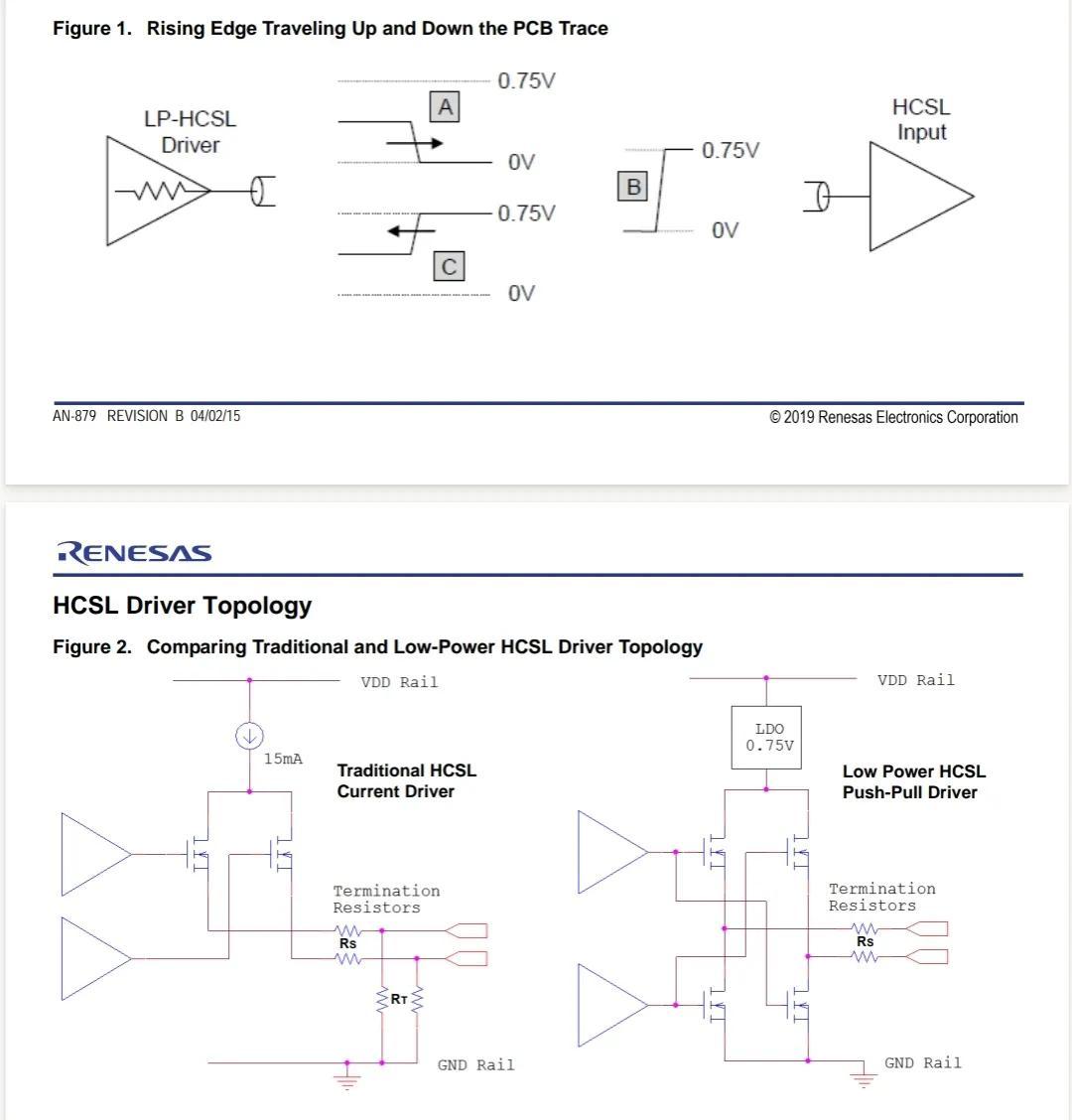

2-LP-HCSL比較

LPHCSL(Low-Power HCSL)是為了降低傳統(tǒng)的HCSL驅(qū)動器的功耗而開發(fā)的。采用推-拉(push-pull)電壓驅(qū)動,電流消耗大約4到5mA。

LP-HCSL輸出功能與幅值對比

HCSL與LP-HCSL端接方式:

LP-HCSL直連即可,少了四個電阻效率高,速度快,支持AC耦合。

-

驅(qū)動器

+關(guān)注

關(guān)注

54文章

8374瀏覽量

147714 -

電阻器

+關(guān)注

關(guān)注

21文章

3836瀏覽量

62612 -

耦合

+關(guān)注

關(guān)注

13文章

591瀏覽量

101136 -

接口

+關(guān)注

關(guān)注

33文章

8777瀏覽量

152417 -

時鐘

+關(guān)注

關(guān)注

11文章

1759瀏覽量

132200

發(fā)布評論請先 登錄

相關(guān)推薦

SiTime差分晶振的LVDS、LVPECL、HCSL、CML模式相互轉(zhuǎn)換過程介紹

替代PI6C557-05B,RS2CG5705B支持PCIe3.0之4HCSL輸出的時鐘生成器

LMK03328使用Code Loader 4,輸入25M晶振請問如何配置輸出HCSL電平?

CDCDB400 HCSL時鐘作為輸入是否支持?緩沖器的輸出是否支持HCSL的設(shè)備?

差分邏輯電平,LVDS、xECL、CML、HCSL/LPHCSL、TMDS等

求助LVDS電平轉(zhuǎn)HCSL的轉(zhuǎn)換電路

求分享符合LS1028A要求的任何HCSL部件

I/O接口標(biāo)準(zhǔn)解析系列教程(3):HCSL和LPHCSL

核芯互聯(lián)推出符合DB2000QL及PCIe Gen5和Gen 6標(biāo)準(zhǔn)的低抖動時鐘緩沖器CLB2000

核芯互聯(lián)推出全新20路LP-HCSL差分時鐘緩沖器CLB2000

HCSL基本電路結(jié)構(gòu)及其相互轉(zhuǎn)換

矽力杰高性能20路PCIe時鐘緩沖器

MG7050HAN 基于聲表的差分多輸出 晶體振蕩器(HCSL)

愛普生6G路由器晶振MG7050HAN,HCSL輸出有源晶振,X1M0004310007

LMKDB1120和LMKDB1108超低抖動PCIe第1代到第6代LP-HCSL時鐘緩沖器數(shù)據(jù)表

HCSL與LP-HCSL的比較分析

HCSL與LP-HCSL的比較分析

評論