CML(Current Mode Logic)電流模式邏輯電路主要靠電流驅動,它的輸入與輸出的匹配集成在芯片內部,基本不需要外部端接,從而使單板硬件設計更簡單、更簡潔。被廣泛應用于網絡物理層的傳輸和高速Serdes器件。

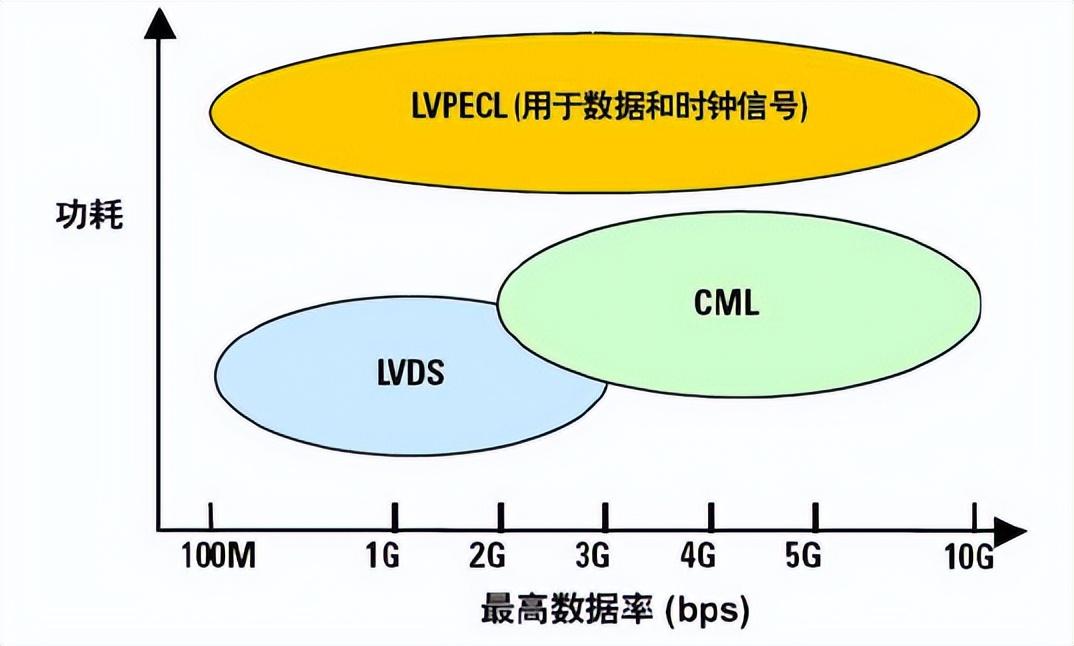

速度更高,CML理論極限速度可達10Gbit/s;

功率更低,

外圍更簡單,幾乎不需要外圍器件

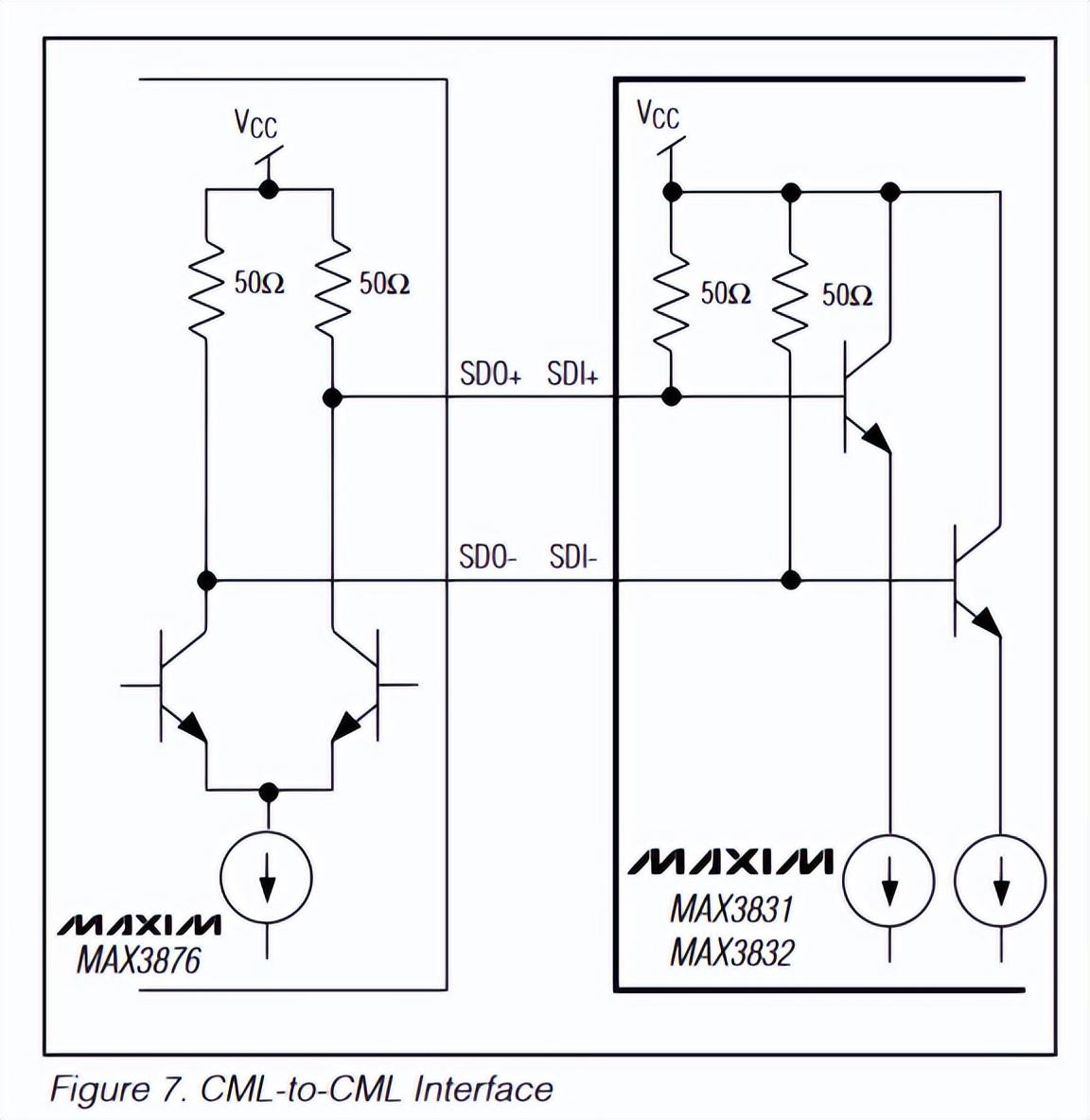

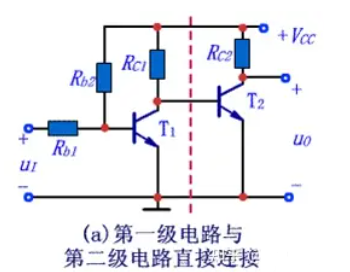

1、CML輸入輸出結構

CML 接口的輸出電路形式是一個差分對,該差分對的集電極電阻為50Ω,恒流源典型值為16mA。

CML輸入與輸出接口拓撲

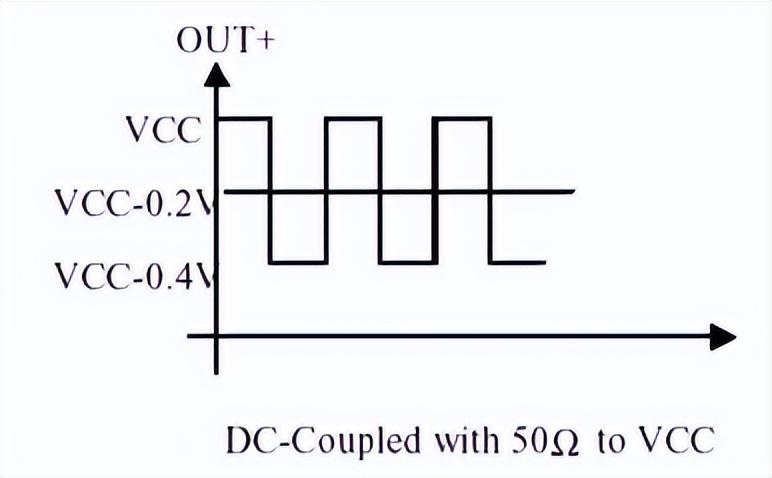

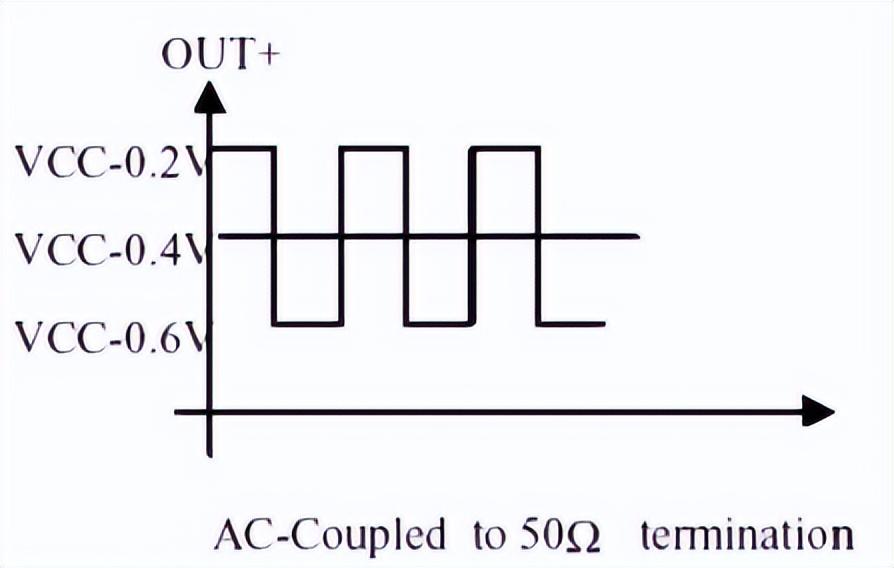

2、CML輸出波形

DC耦合時,CML 輸出負載為一50Ω上拉電阻,單端CML 輸出信號的擺幅為Vcc~Vcc-0.4V。

AC耦合時,CML 輸出負載經過電容后經過50Ω上拉電阻,單端CML 輸出信號的擺幅為Vcc-0.2~Vcc-0.6V。

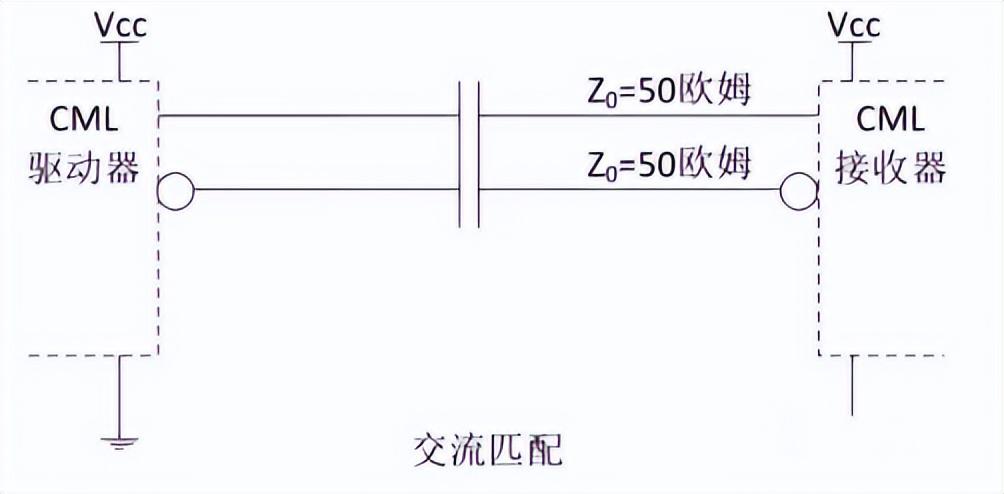

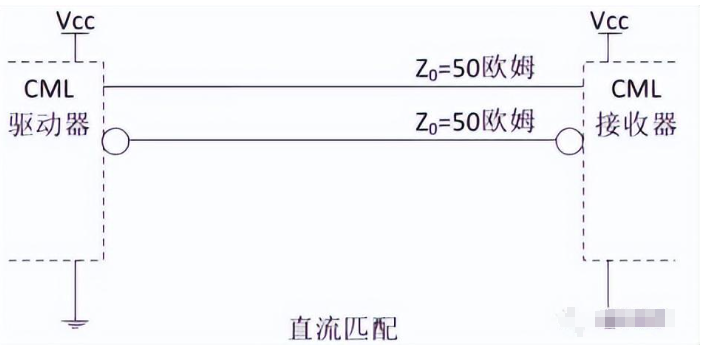

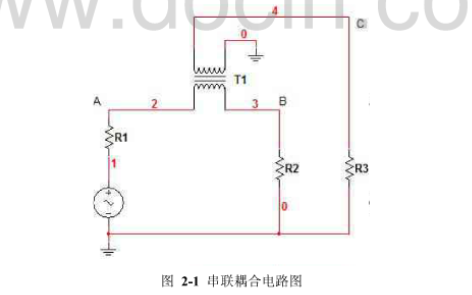

3、CML耦合方式

如果接收器有內置匹配(上拉50Ω電阻)與發送器采用不同的電源用交流耦合方式。

如果接收器有內置匹配(上拉50Ω電阻)與發送器采用相同的電源用直流耦合方式。

-

邏輯電路

+關注

關注

13文章

494瀏覽量

42647 -

接收器

+關注

關注

14文章

2473瀏覽量

71961 -

耦合

+關注

關注

13文章

583瀏覽量

100897 -

接口

+關注

關注

33文章

8620瀏覽量

151321 -

CML

+關注

關注

0文章

32瀏覽量

19344

發布評論請先 登錄

相關推薦

LVDS、CML、LVPECL不同邏輯電平之間的互連(二)

淺談LVDS、CML、LVPECL三種差分邏輯電平之間的互連

LVPECL、VML、CML、LVDS 與LVDS之間的接口連接轉換

請問如何在Kintex-7 HP輸入端終止交流耦合CML信號?

如何在LVPECL、VML、CML、LVDS和子LVDS接口之間轉換

如果ad9680的clk和sysref信號采用lvpecl格式輸入,交流耦合的話前端網絡如何設計?

示波器觸發耦合方式的選擇方法介紹

SN65CML100 1.5Gbps LVDS/LVPECL/CML 至 CML 轉換器/中繼器

CML耦合方式介紹

CML耦合方式介紹

評論