當采用buffer 驅動容性負載或者整個回路中存在較多的RC 延時環節,當輸入信號為瞬變信號,容易導致輸出震蕩。接下來我們了解輸出震蕩的原因以及防止震蕩的方法。

一、為什么輸出會震蕩?

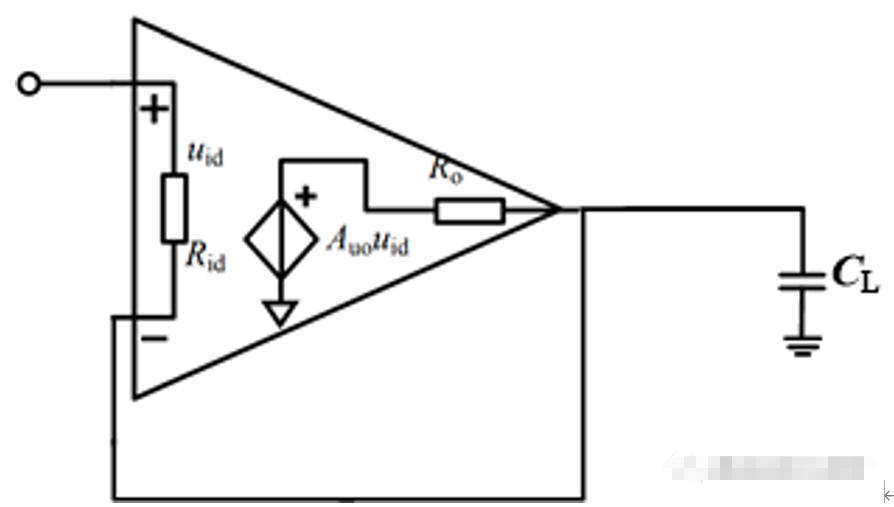

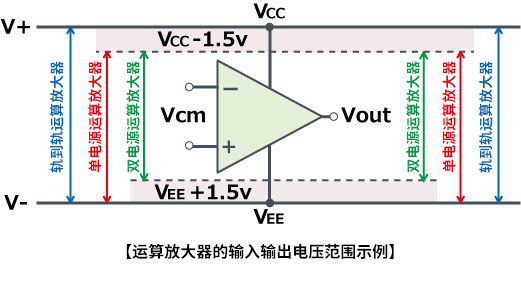

實際運算放大器芯片的輸出端會存在輸出阻抗,如下圖中Ro,當運放帶容性負載,如驅動線圈;驅動MOS管等。運放芯片內部Ro會與輸出電容CL形成極點:fp =1/2pi*CL*Ro極點造成系統相位裕度下降 (當相位裕度為20°時,輸出的超調量高達55%)從而造成輸出震蕩。

時域上當CL較大(nF~uF級別)時,時域上運放輸出到反饋之間由RoCL造成的延遲過大導致輸出震蕩。(只有輸入信號為瞬變信號時才會由于其包含的高頻分量信號無法及時被反饋而震蕩)

二、防震方法 1 ——輸出加電阻:

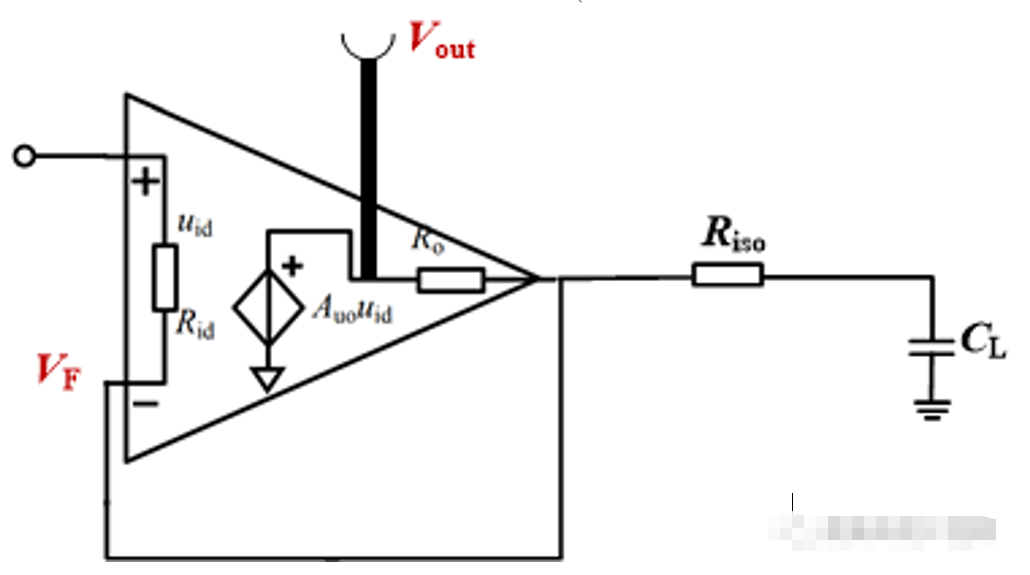

在輸出加電阻是借由Riso引入新的零極點fz1、發fp1,當Riso>>Ro時,fp1 ≈ fz1 零極點近似相互抵消,達到補償系統相位裕度的目的。

fz1 =1/2pi*CL*Riso,fp1=1/2pi* CL* ( Ro +Riso)

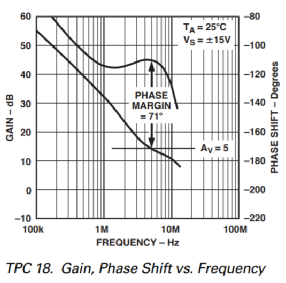

fz1零點補償在穿越頻率10倍頻,開環增益等于20dB處(可從datasheet的幅值相位曲線中得到對應頻率),即可得到 。

此辦法雖然解決了穩定性的問題,但會在Riso上產生壓降,使輸出直流精度下降。不在意精度的時候可以采用此辦法。

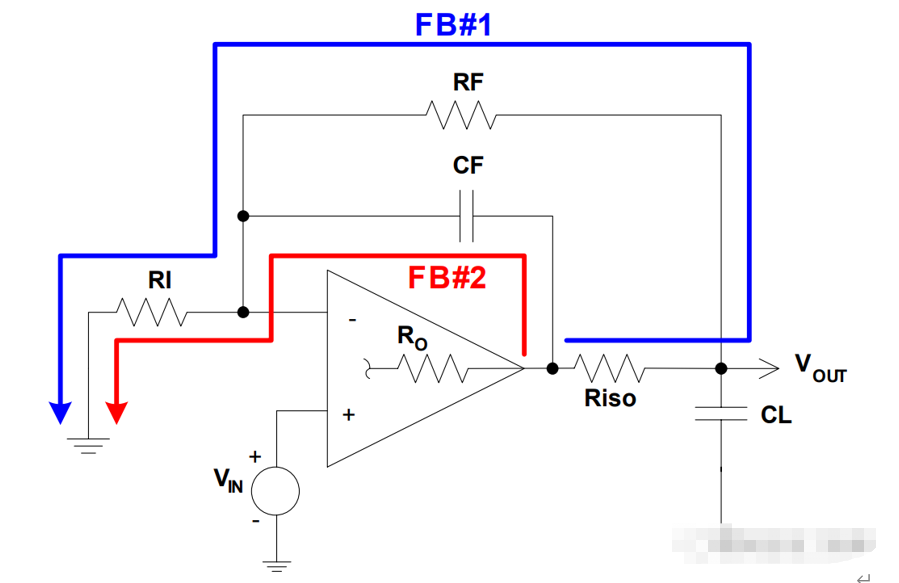

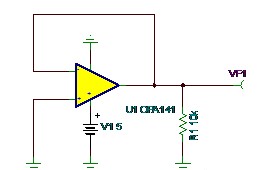

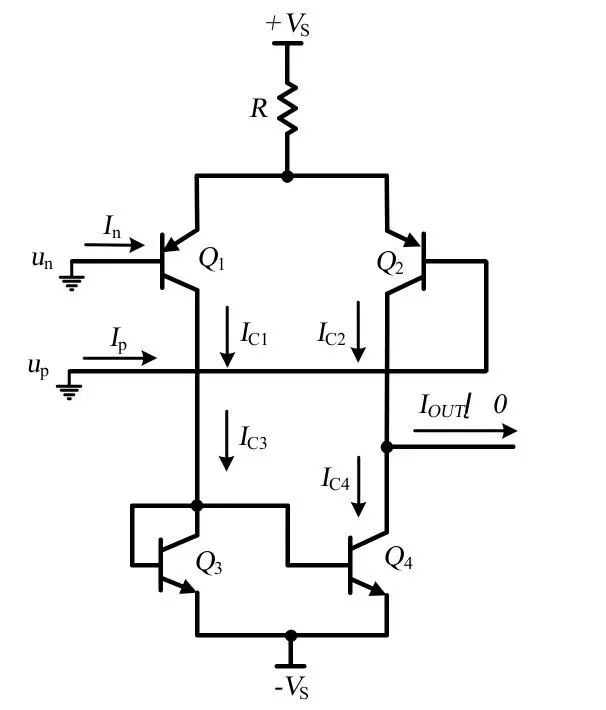

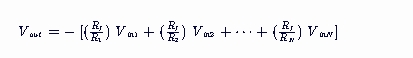

三、解決直流精度問題的防震方法2 ——雙反饋回路

從上圖看到在原有方法1 的基礎上新增加CF,RF,從輸出到反饋端引入了兩條路徑。RF 把信號的低頻分量(CF: Open,RF: Closes the feedback around Riso)由正向輸入端跟隨到輸出端; CF則把回路通過的高頻分量(CF: Short, RF is effectively open)經Riso引入整個回路,實現相位補償的目的。

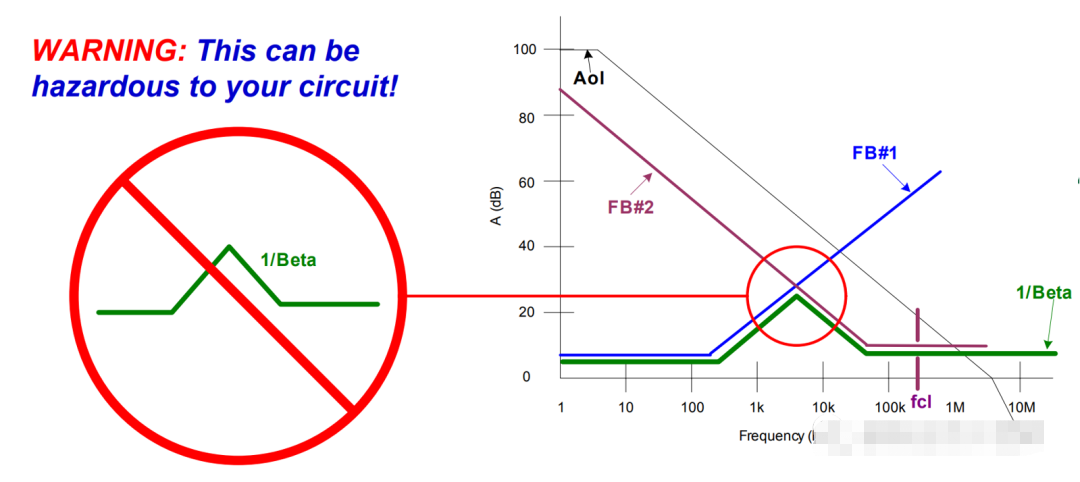

上圖為兩個反饋路徑以及兩者疊加的幅值裕度隨頻率變化曲線。當圍繞一個運放使用雙反饋路徑時,兩個反饋路徑交疊處疊加出來的反饋效果會使1/β 斜率從+20db/decade 突然 變成了-20dB/decade。這意味著1/β曲線存在一個復共軛極點,這樣相應地在環路增益曲線上即有 一個復共軛零點。復零點與極點在其對應的頻率上引起一個 +/-90 度的相移。此外,復零點/復極點的相位斜率, 在其出現頻率位置附近的一個狹窄頻帶內可從+/-90 度變化至+/-180 度。復零點/復極點的產生在閉環運放響應中可能會引起嚴重的增益尖峰,這是很不希望看到的情況,尤其在功率運放電路中。因此,對于CF的取值我們不希望太小,導致相位裕度變化頻帶過窄,同時也不能太大,使整體帶寬變小。

對于的具體取值:

1. Riso>> Ro

2. RF ≥100×Riso

3.6*Riso*CL≤RF*CF≤18*Riso*CL ,CF在此范圍內取值可保證兩個路徑相對穩定。

分享具體案例:

實驗驗證:以一顆常用運放器件(phase margin 75°)為例。

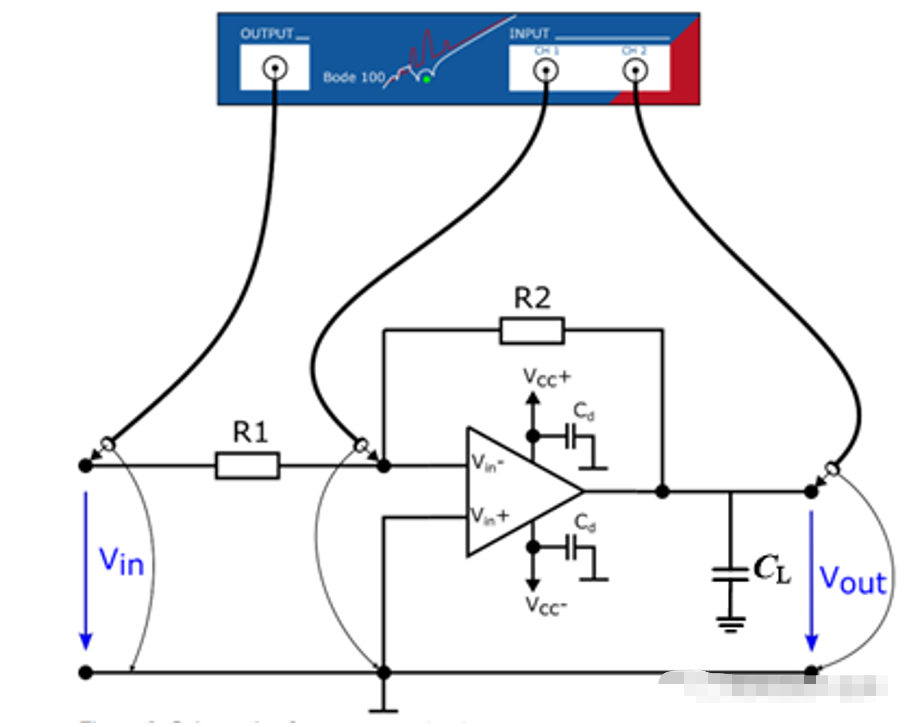

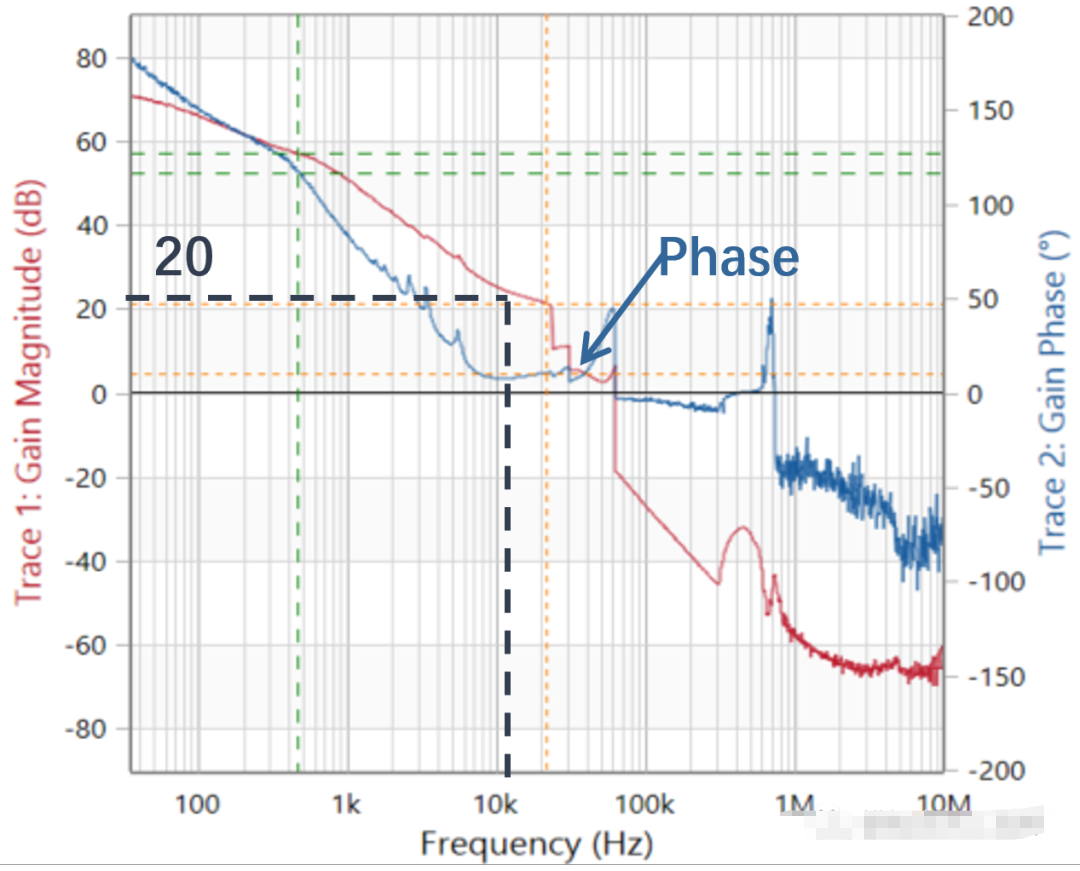

當其帶容性負載為1uF時,通過Bode 100對以下電路進行掃頻得到其開環特性的幅頻和相頻曲線。

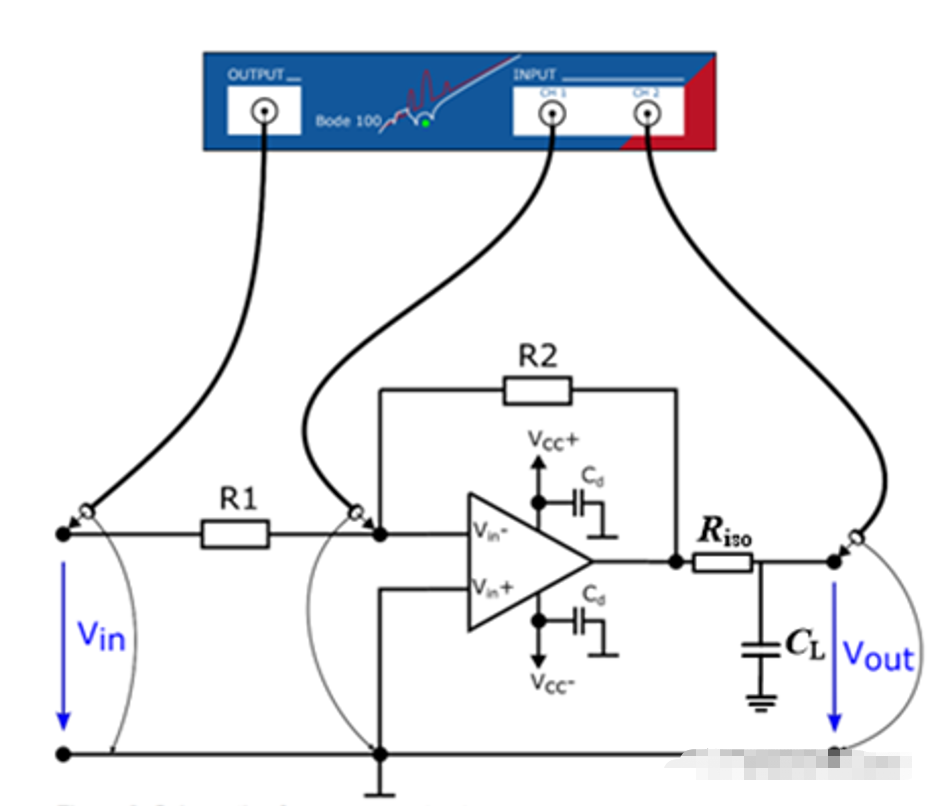

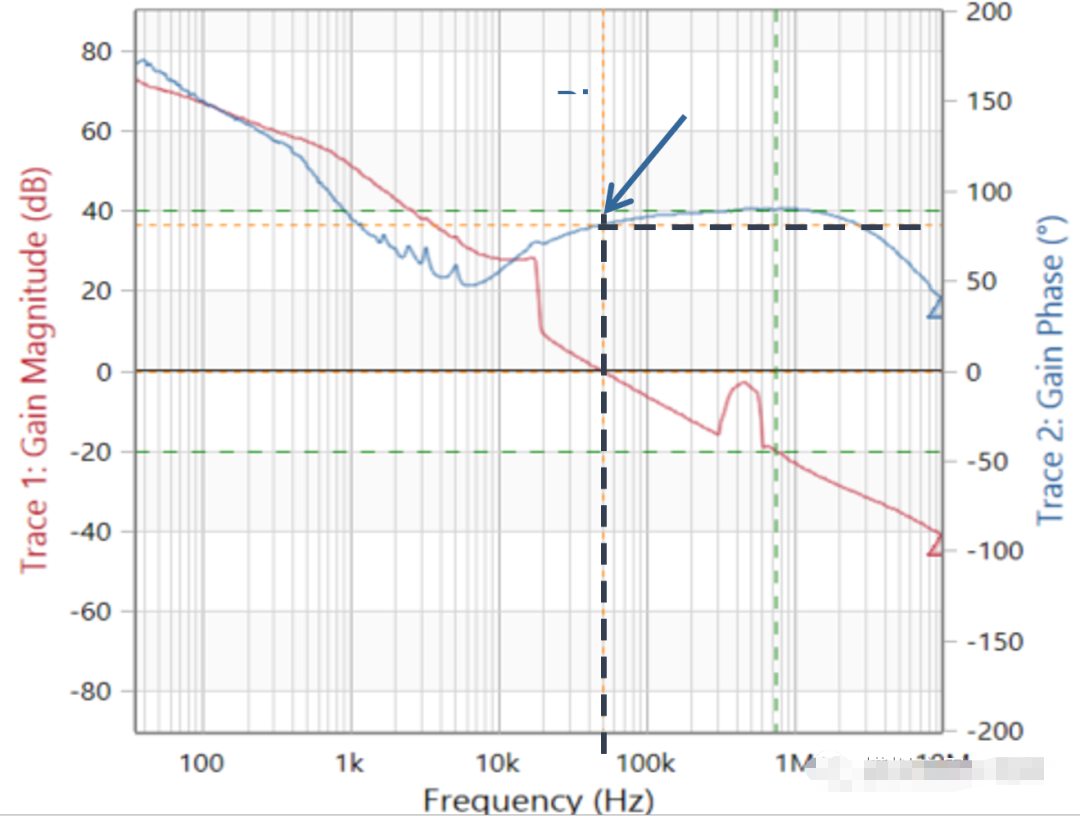

取Riso=18Ω進行相位補償,再對增加Riso的電路進行掃頻,得到的開環特性的幅頻和相頻曲線如下所示。

如上圖,加入Riso后系統相位裕度變成81°,添加Rf=22kΩ,

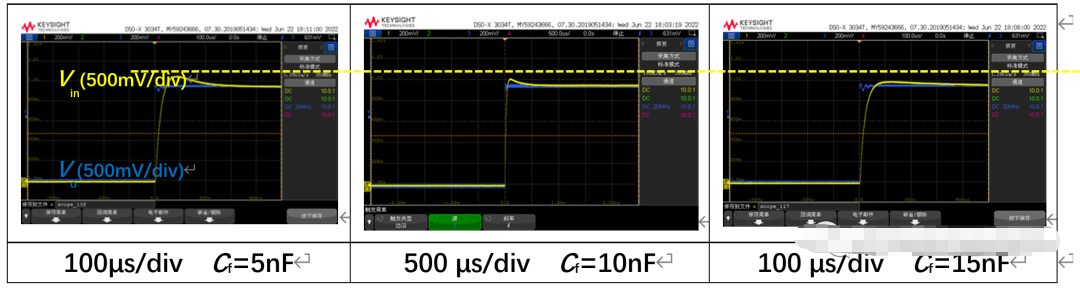

取Rf>1000Riso,Cf分別取5/10/15nF,輸入1V階躍信號(黃色),輸出電壓波形(藍色)如下圖所示,Cf越大阻尼越大, 超調量越小。實際Rf>100Riso即可,這樣Cf更大系統響應速度更快,超調量會減小。

通過以上實驗,我們知道當運放跟隨電路帶容性負載輸出震蕩時,可以通過添加Riso與雙反饋回路進行相位與精度補償,在用戶端我們也推薦工程師預留Riso、Rf、Cf的位置。如若已經設計好電路來不及修改,也可嘗試選用相位裕度較大的運放進行替代。

-

線圈

+關注

關注

14文章

1832瀏覽量

44521 -

運算放大器

+關注

關注

215文章

4952瀏覽量

173153 -

MOS管

+關注

關注

108文章

2426瀏覽量

67104 -

運放

+關注

關注

47文章

1166瀏覽量

53146 -

RC

+關注

關注

0文章

227瀏覽量

48873

發布評論請先 登錄

相關推薦

運算放大器的自激震蕩

什么是運算放大器

高精度運算放大器,高精度運算放大器是什么意思

運算放大器的應用及種類介紹

運算放大器的輸出限制

運算放大器輸出震蕩的原因和防震方法

運算放大器輸出震蕩的原因和防震方法

評論