什么是 ECO?

ECO 指的是Engineering Change Order,即工程變更指令。目的是為 了在設計的后期,快速靈活地做小范圍修改,從而盡可能的保持已經驗證 的功能和時序。ECO 的叫法算是從 IC 設計領域繼承而來,其應用在 FPGA 設計上尚屬首次,但這種做法其實在以往的 FPGA 設計上已被廣泛采用。簡單來說,ECO 便相當于 ISE 上的 FPGA Editor。

但與 FPGA Editor 不同,Vivado 中的 ECO 并不是一個獨立的界面或是一些特定的命令,要實現不同的 ECO 功能需要使用不同的方式。

ECO 的應用場景和實現流程

ECO 的應用場景主要包含:修改cell 屬性、增減或移動 cell、手動局部布線。還有一些需要多種操作配合的復雜場景,例如把 RAM(或 DSP)的輸出寄存器放入/拉出 RAMB(或 DSP48)內部,或是把設計內部信號接到 I/O 上作調試 probe 用等等。

針對不同的應用場景,Vivado 中支持的 ECO 實現方式也略有區別。 有些可以用圖形界面實現,有些則只能使用 Tcl 命令。但通常可以在圖形化界面上實現的操作,都可以改用一條或數條 Tcl 命令來實現。

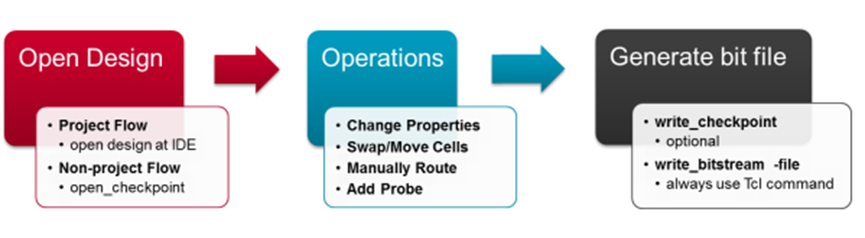

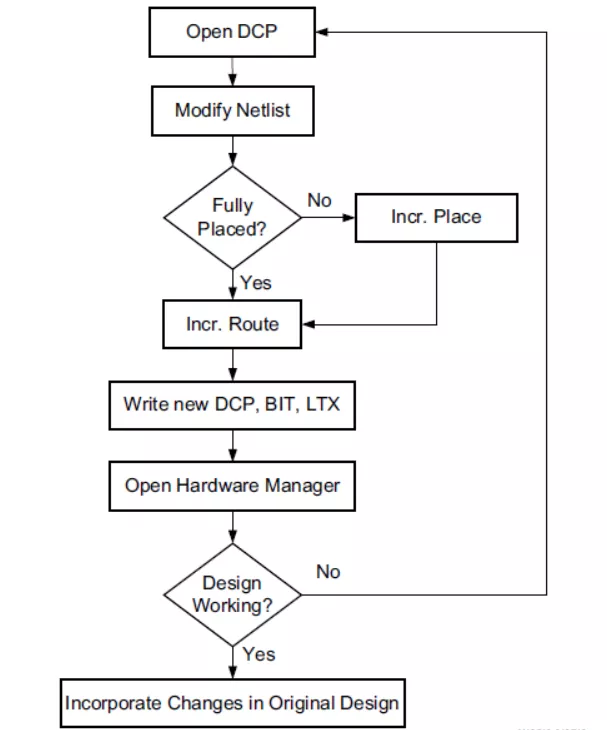

ECO 的實現流程如下圖所示:

第一步所指的 Design 通常是完全布局布線后的設計,如果是在工程模式下,可以直接在 IDE 中打開實現 后的設計,若是僅有 DCP 文件,不論是工程模式或是非工程模式產生的 DCP,都可以用 open_checkpoint 命 令打開。

第二步就是 ECO 的意義所在,我們在布局布線后的設計上進行各種操作,然后僅對改動的部分進行局部布局/布線而無需整體重跑設計,節約大量時間的同時也不會破壞已經收斂的時序。

第三步就是產生可供下載的 bit 文件了,此時必須在 Tcl Console 中或是 Tcl 模式下直接輸入命令產生 bit 文件,而不能使用 IDE 上的“Generate Bitstream”按鈕。原因是后者讀到的還是 ECO 前已經完成布局布線的原 始設計,生成的 bit 文件自然也無法使用。

修改屬性

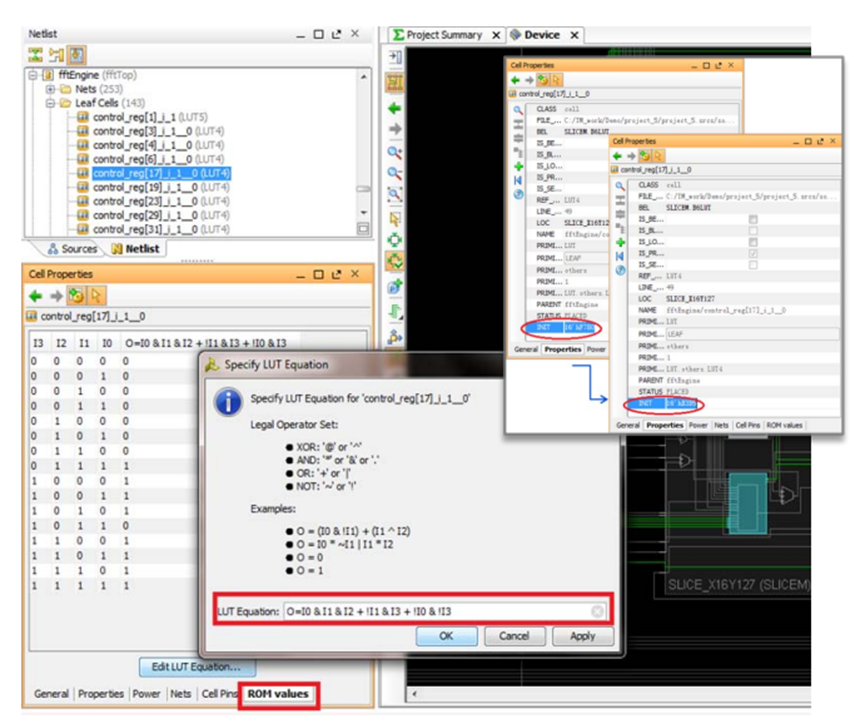

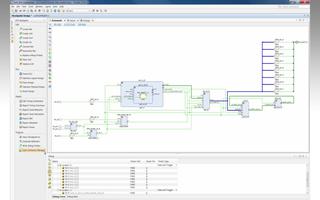

絕大部分的屬性修改都能通過 IDE 界面完成,如下圖所示。

比如要修改寄存器的初值 INIT 或是 LUT 的真值表,用戶只需在 Vivado IDE 中打開布局布線后的設計 (Implemented Design),在 Device View 中找到并選中這個 FF/LUT,接著在其左側的 Cell Properties 視圖中 選擇需要修改的屬性,直接修改即可。

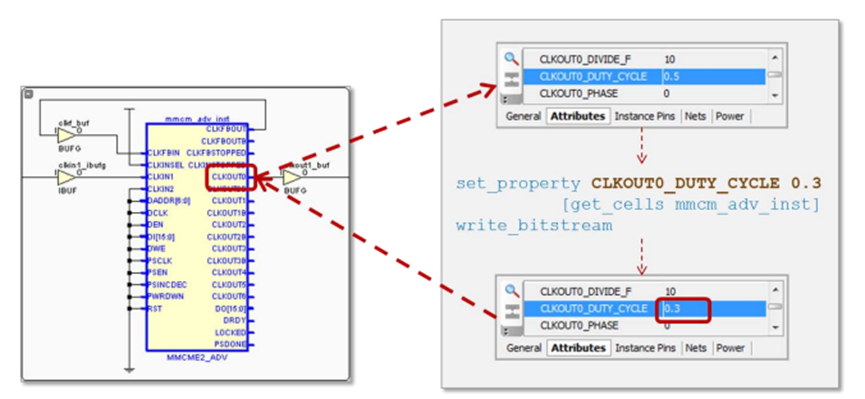

除了對 FF/LUT 的操作外,很多時候我們需要對 MMCM/PLL 輸出時鐘的相移進行修改。對于這種應用,用戶也無需重新產生 MMCM/PLL,與上述方法類似,可以在布局布線后的 Device View 上直接修改。

移動/交換 cells

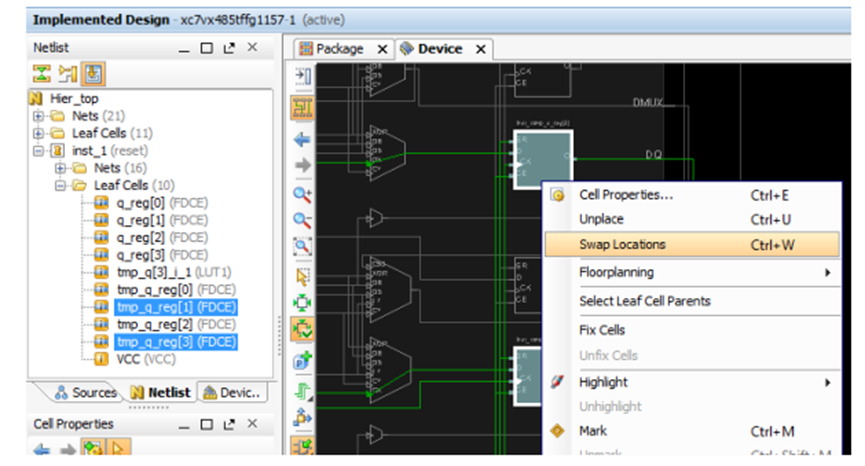

移動/交換 cells 是對 FF/LUT 進行的 ECO 操作中最基本的一個場景,目前也只有這種情況可以通過圖形化實現。如要刪減 cells 等則只能通過 Tcl 命令來進行。

具體操作方法也相當簡便,要互換 cells 位置的情況下,只要在 Device View 上選中需要的那兩個 cells,如上圖所示的兩個 FFs,然后右鍵調出菜單,選擇 Swap Locations 即可。若要移動 cells 則更簡單,直接在圖 中選中 FF 拖移到新的位置即可。

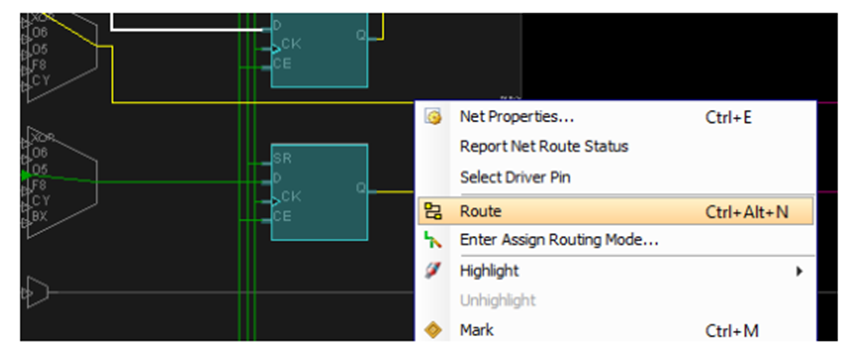

當用戶移動或改變了 cells 的位置后會發現與其連接的 nets 變成了黃色高亮顯示,表示這些 nets 需要重新布線。這時候需要做的就是在圖中選中這些 nets 然后右鍵調出菜單,選擇 Route 進行局部布線。

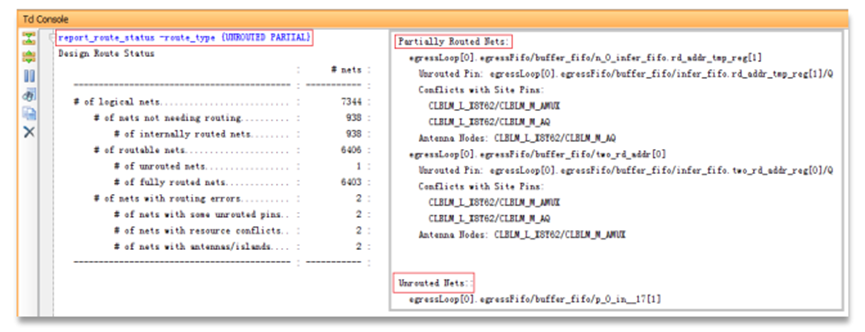

局部布線后一定要記得在 Tcl Console 中使用 report_route_status 命令檢查布線情況,確保沒有未完成布線(unrouted)或是部分未完成布線(partial routed)的 nets 存在。給這個命令加上選項則可以報告出更細致的結果,如下圖所示。

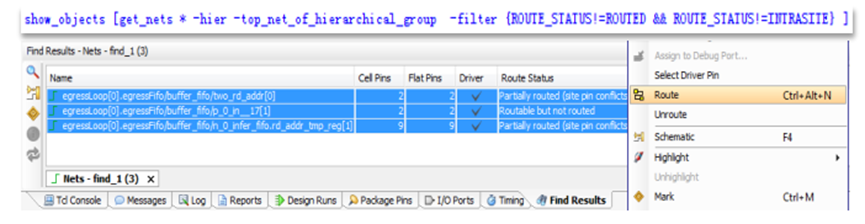

如果換個稍復雜些的 Tcl 命令配合圖形化顯示,更加直觀的同時,也可以方便右鍵調出命令進行針對性的局部布線。

手動布線

手動布線是一種非常規的布線方式,一次只能針對一根 net 在圖形化界面下進行。所謂手動布線,除了完全手動一個節點一個節點的選擇外,也支持工具自動選擇資源來布線。通常我們并不建議全手動的方式, Vivado 是時序驅動的工具,所以其自動選擇的布線結果已經是遵循了時序約束下的最佳選擇。

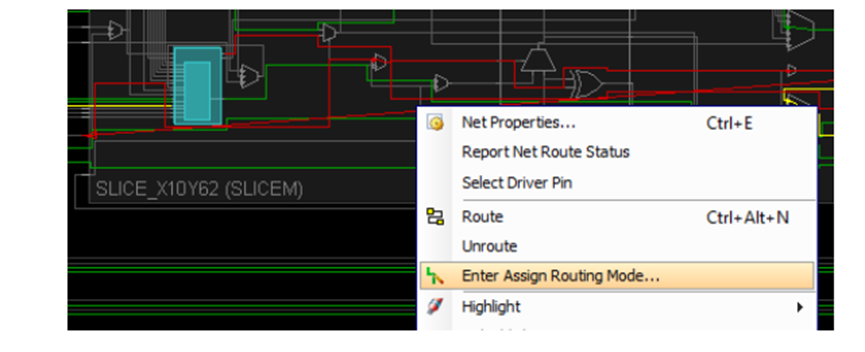

在 Device View 中選擇一根沒有布線或是預先 Unroute 過的 net(顯示為紅色高亮),右鍵調出菜單并選擇 Enter Assign Routing Mode… 便可進入手動布線模式。

復雜的 ECO場景

篇幅過半,一直在鋪墊,其實最有實踐意義的 ECO 還沒提到。相信大部分用戶最懷念 FPGA Editor 中的 一個功能就是 probe 了,如何快速地把一根內部信號連接到 FPGA 管腳上,無需重新布局布線,直接更新 bit 文件后下載調試。曾經數次被客戶問及,很多人還為 Vivado 中不支持這樣的做法而深表遺憾。

其實這樣類似的功能在 Vivado 中一直支持,唯一的問題是暫時還沒有圖形化界面可以一鍵操作(相關開 發工作已經在進行中)。但受益于 Tcl 的靈活多變,我們可以更有針對性地實現 probe 功能,效率也更高。

Tcl 操作命令

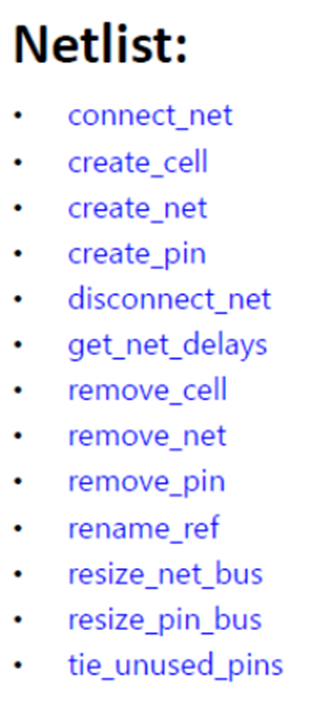

在 UG835 中把 Vivado 支持的 Tcl 命令按照 Category 分類,這些列于 Netlist 目錄下的命令就是實現 ECO 需要用到的那些。

通常涉及到增減 cells 的 ECO 基本分為三步實現:首先用create_cell / create_net 等創建相關 cell 和/或 net,然后用 disconnect_net / connect_net 等命令修正因為 cell 和 net 的改動而影響到的連接關系,最后用 route_design 加選項完成局部布線。

不同的 Vivado 版本對此類 ECO 修改有稍許不同的限制,例如在 2014.1 之后的版本上,需要在改變 cell 的連接關系前先用 unplace_cell 將 cell 從當前的布局位置上釋放,在完成新的連接關系后,再用 place_cell 放到新的布局位 置上。

具體操作上可以根據 Vivado 的提示或報錯信息來改動具體的 Tcl 命令,但 操作思路和可用的命令相差無幾。

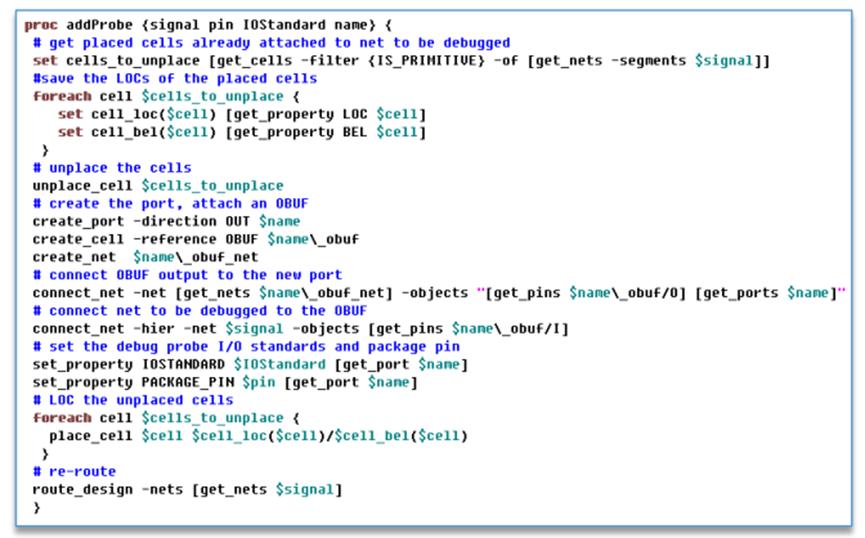

Add Probe

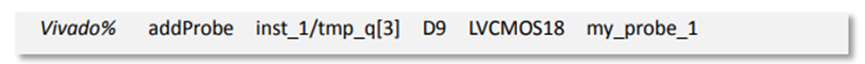

這是一個在 Vivaod 上實現 probe 功能的 Tcl 腳本,已經寫成了 proc 子程序,簡單易懂。可以直接調用,也可以做成 Vivado 的嵌入式擴展命令。調用其生成 probe 只需先 source 這個腳本,然后按照如下所示在 Tcl Console 中輸入命令即可。

該腳本已經在 Vivado2014.3 和 2014.4 上測試過,一次只能完成一個 probe 的添加,而且必須按照上述順 序輸入信號名,管腳位置,電平標準和 probe 名。因為不具備預檢功能,可能會碰到一些報錯信息而導致無法繼續。例如選擇的信號是只存在于 SLICE 內部的 INTRASITE 時,則無法拉出到管腳。再比如輸入命令時拼錯了電平標準等,也會造成 Tcl 已經部分修改 Vivado 數據庫而無法繼續的問題。此時只能關閉已經打開的 DCP 并選擇不保存而重新來過。

ECO 在 Vivado 上的發展

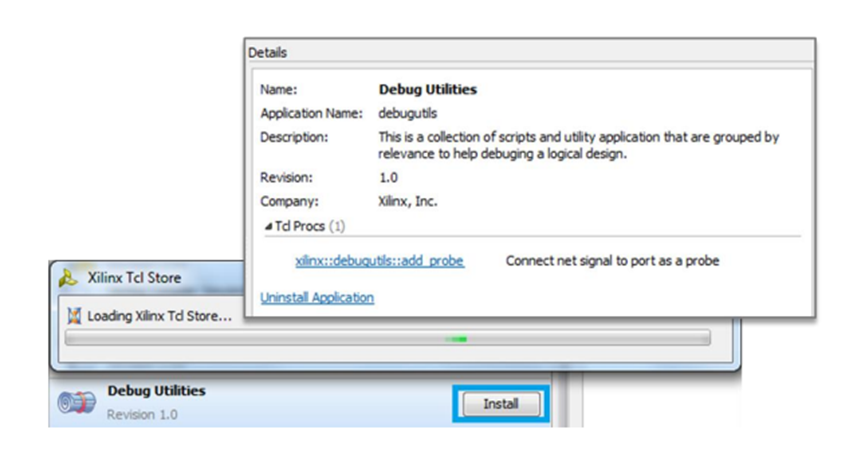

經過了兩年多的發展,在 Vivado 上實現 ECO 已經有了多種方式,除了前面提到的圖形化上那些可用的技巧,還有用戶自定義的 Tcl 命令和腳本等。隨著 Xilinx Tcl Store 的推出,用戶可以像在 App Store 中下載使用 app 一樣下載使用 Tcl 腳本,簡化了 Tcl 在 Vivado 上應用的同時,進一步擴展了 Tcl 的深入、精細化使用,其 中就包括 Tcl 在 ECO 上的應用。

目前 Vivado 2014.4 版本上新增了很多有用的腳本。安裝好 Vivado 后,只需打開 Tcl Store,找到 Debug Utilities,點擊 Install 稍等片刻,即可看到一個 add_probe 的 Tcl proc 被安裝到了你的 Vivado 中。

這個 add_probe 是在上述 addProbe 例子的基礎上擴展而來,不僅可以新增 probe,而且可以改變現有 probe 連接的信號。此外,這個腳本采用了 argument 寫法,點擊程序可以看 help,所以不一定要按照順序輸入信號、電平標準等選項,輸錯也沒有問題。另外增加了預檢和糾錯功能,碰到問題會報錯退出而不會改變 Vivado 數據庫,效率更高。

此外,Tcl Store 上還有很多其它好用的腳本,歡迎大家試用并反饋給我們寶貴意見。雖然里面關于ECO 的腳本還很少,但我們一直在補充。此外 Tcl Store 是一個基于 GitHub 的完全開源的環境,當然也歡迎大家上傳自己手中有用的 Tcl 腳本,對其進行補充。

總體來說,ECO 是一個比較大的命題,因為牽扯到的改動需求太多,其實也很難限制在一個 GUI 界面中實現。這篇文章的目的就是為了讓大家對在 FPGA 上實現 ECO 有個基本的認識,梳理看似復雜無序的流程,所謂觀一葉而知秋,窺一斑而見全豹,希望能帶給更多用戶信心,用好 Vivado 其實一點都不難。

審核編輯:劉清

-

dsp

+關注

關注

556文章

8161瀏覽量

358017 -

FPGA設計

+關注

關注

9文章

428瀏覽量

27392 -

IC設計

+關注

關注

38文章

1360瀏覽量

105844 -

RAM

+關注

關注

8文章

1392瀏覽量

117630

原文標題:在Vivado中實現ECO功能

文章出處:【微信號:FPGA算法工程師,微信公眾號:FPGA算法工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

Vivado使用誤區與進階——在Vivado中實現ECO功能

汽車eco模式使用技巧_eco模式真能省油嗎

eco模式的好處以及壞處_eco模式會引起積碳是真的嗎

Uber聯合創始人發行加密貨幣Eco 希望Eco能夠復蘇虛擬貨幣

ECO技術在SoC芯片設計中的應用

自動ECO參考網表來自動修改實現網表

一場關于自動化ECO解決方案的在線研討會

空調遙控器上的eco是什么意思

詳解Xilinx FPGA的ECO功能

詳細描述和解釋GOF ECO每一個步驟的實現方法和注意事項

什么是DFT友好的功能ECO呢?

解析什么是DFT友好的功能ECO?

評論