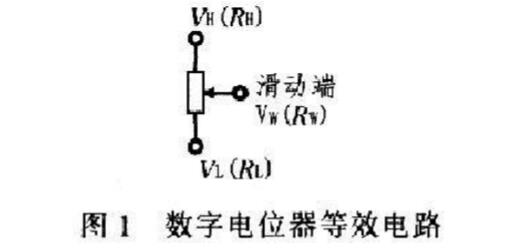

一、數字電位器簡介

數字電位器是一種可由數字信號控制的電位器,當前使用范圍十分廣泛,區別于滑動、機械調節的電位器,而是屬于集成電路,優點主要有:可以進行細調,調節精度高,無機械磨損,壽命高; 缺點:不能對阻值連續調整,只能按芯片位數的最小間隔調整。

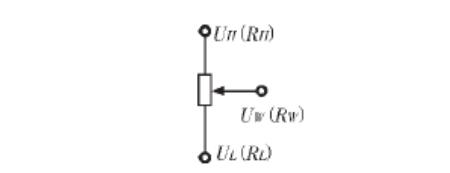

數字電位器最終控制的是阻值的變化,依據此性能可以在不同的原理下,實現分壓、電流控制、增益控制、信號控制、偏移調整等應用。

2.1 以AD5174BRMZ-10為例

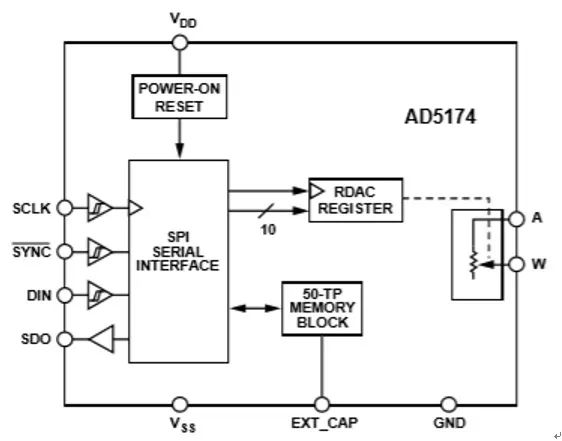

AD5174BRMZ-10是一款1024位的,10K數字電位器,SPI接口。 功能框圖如下:

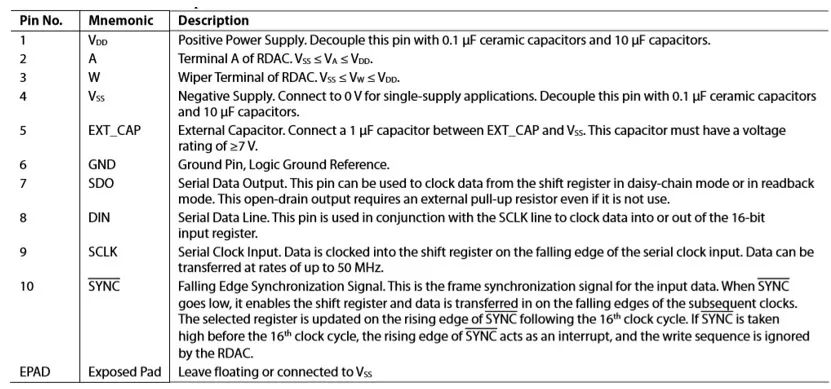

芯片各引腳功能介紹如下:

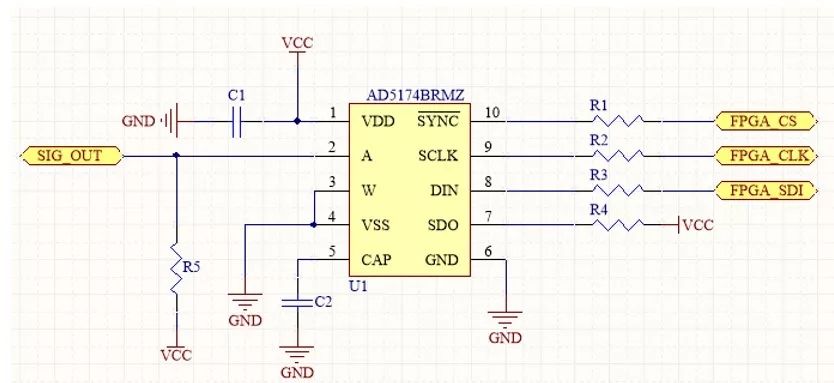

2.2 原理連接

右端3個信號連入到FPGA引腳,左端SIG_OUT是數字電位器電阻輸出端。

三、FPGA代碼設計

3.1 芯片手冊代碼使用信息匯總

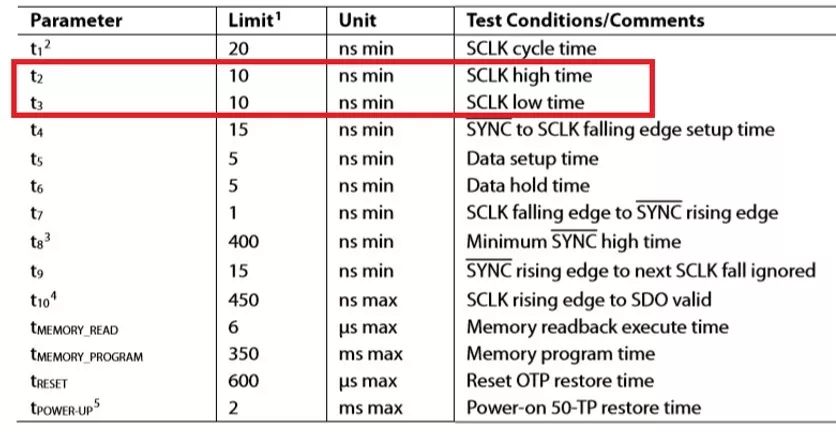

由數字電位器芯片時序要求中下圖紅框內需求,可得FPGA的PLL最小時鐘需要在100MHz。

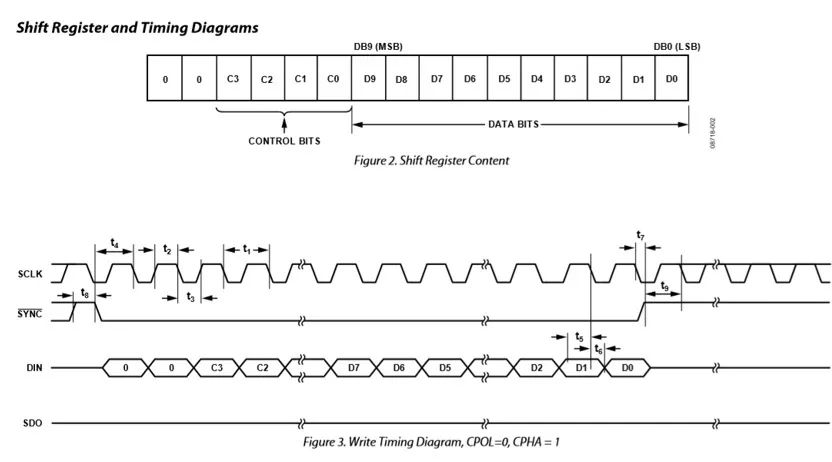

由芯片寄存器內容要求,可知每次需要在SPI中寫入16位數據,分別是:00+控制位(4bits)+數據位(10bits)

由芯片寫時序框圖中,可知,SPI數據在時鐘下降沿寫入。

芯片SPI讀的功能與實現,本文未涉及。

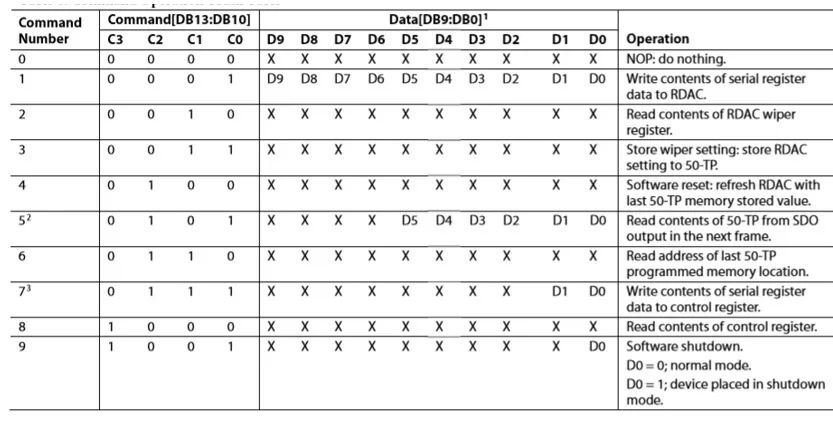

由命令真值表,可得各功能對命令的操作,本文主要介紹對數字電位器的寫入操作,所以使用以下兩條命令:

第1條:串行數據寫入到RDAC寄存器,用于控制芯片電阻值輸出。

第7條:串行數據寫入到控制寄存器,對芯片進行設置。

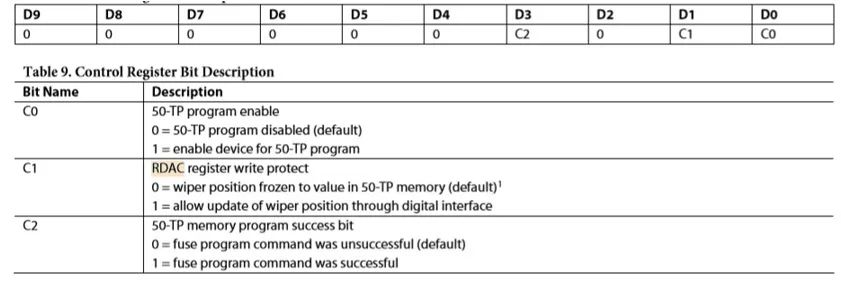

由控制寄存器位映射,可得相應位的設置功能。

3.2 FPGA的SPI數據設計

先進行BLOCK的設計,輸入部分根據實際應用的平臺工程而定,輸出則是與數字電位器連接的SPI口。

時鐘的輸入各位可以定義constant,std_logic_vector(71 downto 0),共72位,其中包括:

起始00(2bits)+控制字時鐘(32bits)+分隔位(4bits)+設置數據時鐘(32bits)+結束00(2bits)

例:001010101010101010101010101010101000001010101010101010101010101010101000

片選相應各位同時鐘定義,在起始、分隔、結束時為高,其它數據傳輸為有效低電平

例:100000000000000000000000000000000011100000000000000000000000000000000011

數據輸入定義同時鐘定義,詳細如下:

控制字輸入36位:

起始00(2bits)+ 補充兩位0(4bits)+控制字0111(8bits)+ 10位數據(20bits)+結束00(2bits)

此處注意,之所以每位數據,在代碼中用了2個bits,是為滿足FPGA模擬出的時鐘高低電平對應的數據都有保持。

例:000000001111110000000000000000111100

數據輸入36位:

分隔無效位(6bits)+控制字0001(8bits)+10位數據(20bits)+結束00(2bits)

例:00000000000011“R9R9R8R8R7R7R6R5R5R4R4R3R3R2R1R1R0R0”&“00”

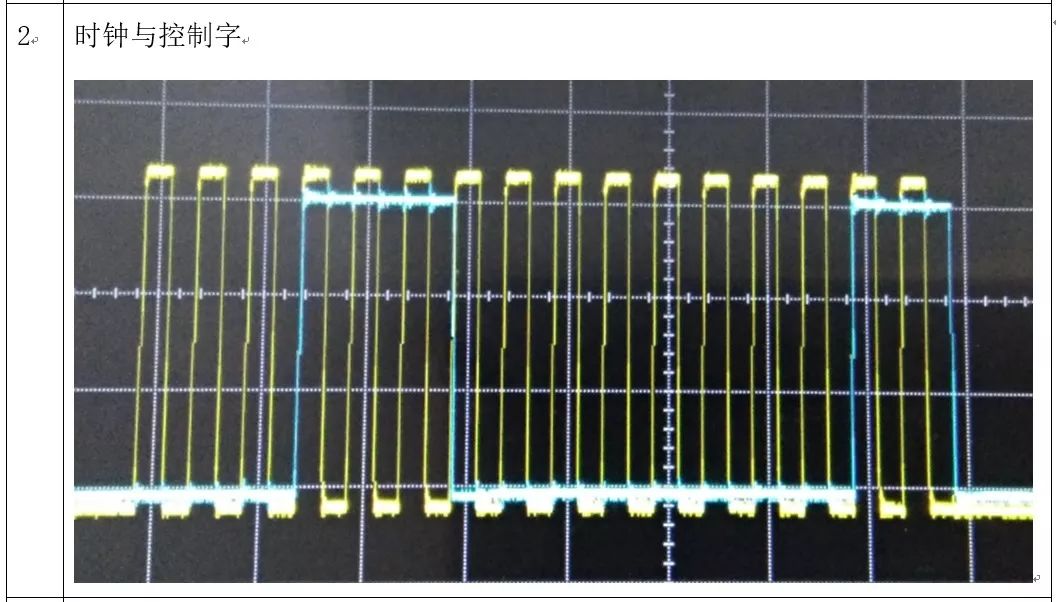

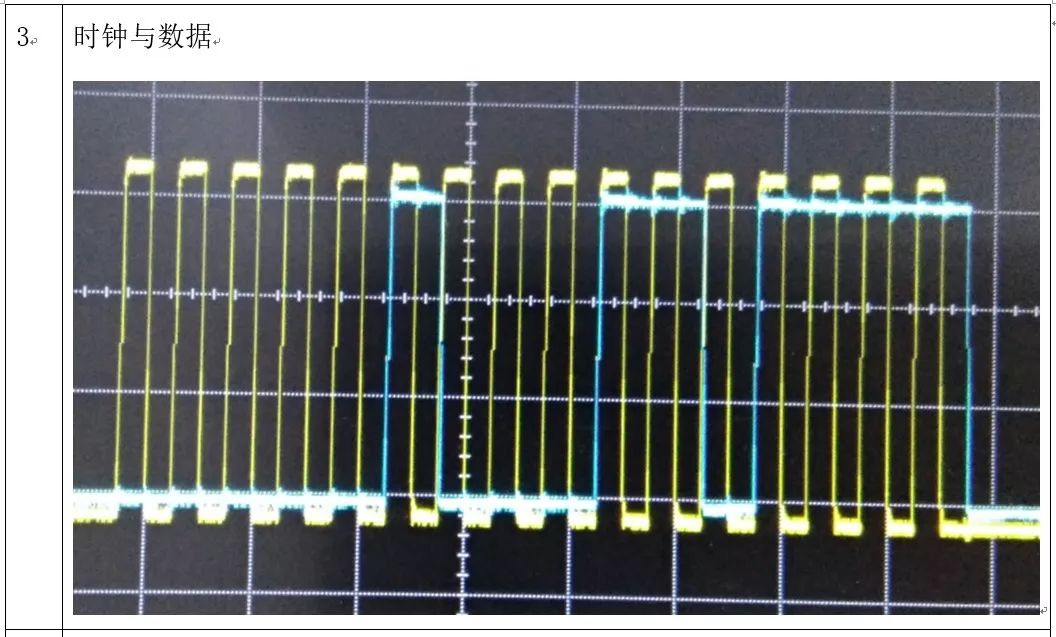

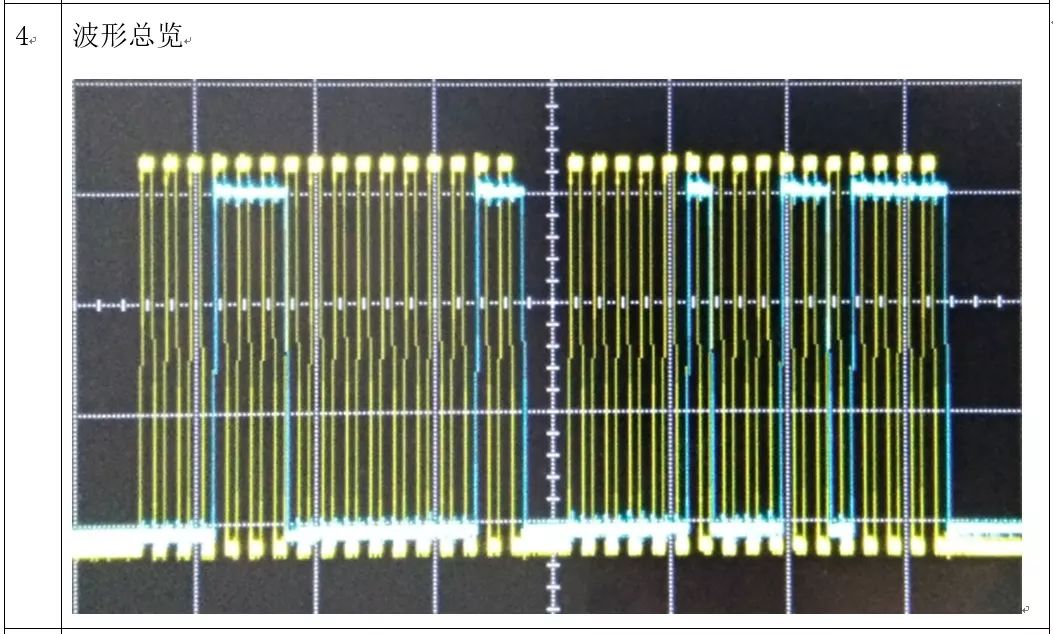

3.3 波形測量

3.4 驗證

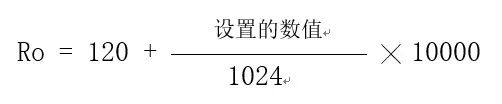

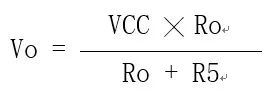

根據數字輸入數據,結合原理分壓情況,可得理論值,與實際測量比較可以進行確認。 需要注意的事,在0標度情況下,數字電位器AD5174BRMZ-10有120Ω的電阻限制。

數字電位器輸出電阻Ro計算公式如下:

輸出電壓Vo的計算公式如下:

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603010 -

寄存器

+關注

關注

31文章

5336瀏覽量

120232 -

電位器

+關注

關注

14文章

1012瀏覽量

66766 -

數字電位器

+關注

關注

4文章

267瀏覽量

83209 -

SPI

+關注

關注

17文章

1706瀏覽量

91508

發布評論請先 登錄

相關推薦

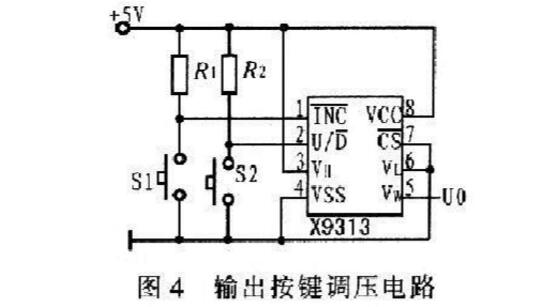

用數字電位器替代機械電位器

基于FPGA的數字電位器設計

基于FPGA的數字電位器設計

評論