1 集成運放和通用集成邏輯電路放置方法

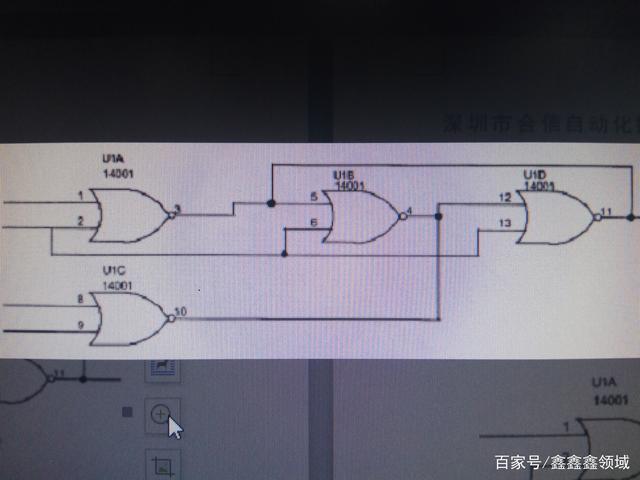

在原理圖中,對于多個單元運放IC和邏輯電路IC一般要按照電路功能將每個單元分開放置,便于對電路的理解和視圖,也符合電路功能單元集中布局的規則。如圖所示:

2 去耦電容的放置

在原理圖中,如果多個IC單元的去耦電容不應集中放置,這樣不利于PCB布局和讀圖人正確理解去耦電容的附屬關系。如下圖不符合的畫法:

為了清晰表達去耦電容對待定IC單元的重要性,去耦電容應該盡量靠近歸屬器件。以保證在PCB設計的時候,不管去耦電容和IC單元的個數是否一一對應去耦電容都能放置到對應的IC上。如圖所示:

如果大規模集成電路芯片往往電源和地的管腳數量眾多,要求的去耦電容數量也比較多,這時可以集中放置,并增加注釋說明。

3 總線的使用

對于數字電路中的總線應用總線方式連接電路關系,能用線連接的就盡量用線連接,而不要依靠網絡標號;當連線跨度太大時,應用網絡標號來連接。這樣所繪制的原理圖信號流向清晰明了,便于視圖。

4 未用管腳的處理

對于IC,在原理圖中未用或者懸空的管腳,應用未連接符號加以標注。邏輯單元中,未使用但在實際中位確保電路性能的穩定性和抗干擾性而管腳接地或電源的標準邏輯單元需在原理圖中體現出來。

-

邏輯電路

+關注

關注

13文章

494瀏覽量

42609 -

IC設計

+關注

關注

38文章

1295瀏覽量

103918 -

PCB布線

+關注

關注

20文章

463瀏覽量

42051 -

去耦電容

+關注

關注

11文章

315瀏覽量

22325

發布評論請先 登錄

相關推薦

硬件原理圖設計規范

【設計規范】orcad原理圖

如何設計電路原理圖詳細設計規范說明

原理圖設計規范

硬件設計案例分析之原理圖設計規范(二)

硬件設計案例分析之原理圖設計規范(二)

評論