1、為什么要用DDS

優點:切換速度快、頻率分辨率高、相位連續等優點,易于集成,功耗較低。輸出信號的相對帶寬較寬,一般為參考信號的三分之一以上。小步進捷變頻的頻率源的實現,一般采用DDS方案實現頻率源的小步進。

缺點:DDS輸出頻率的限制導致其不能實現較為寬帶的頻率源。輸出頻率較低,一般為MHz數量級。DDS在部分頻段雜散大,從而影響頻率源的性能。DDS的最大劣勢也就在于其輸出較多雜散。

DDS基本原理

2、DDS基本原理

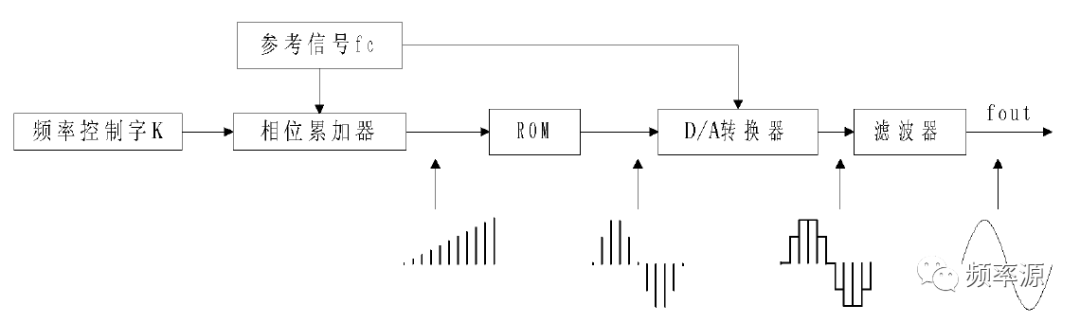

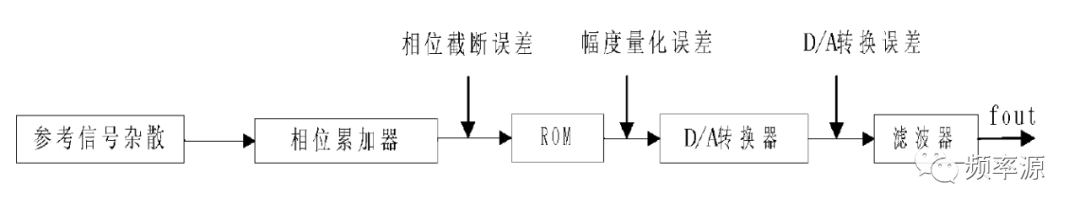

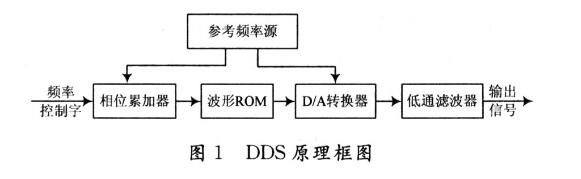

DDS是通過數字的方式構建幅值相位之間的關系,通過查表讀取對應離散的相位幅值數據,后經過數模轉換輸出需要的模擬正弦信號。常規的DDS是由相位累加器、波形存儲器、D/A轉換器以及濾波器組成。

一個周期內正弦波的幅度隨時間的變化并不是線性的,但它的相位隨時間是線性變化的。在一個周期內相位與幅度是一一對應的,所以將原有數字正弦信號進行重新組合產生新的正弦信號。

相位累加器是系統的核心,它控制了系統的最終輸出頻率,它由一個加法器和一個寄存器組成。波形存儲器以相位碼為地址存儲了正弦波形的幅值碼,相當于正弦函數的相位幅值對照表,根據相位碼ROM讀取相應地幅值碼。

相位累加器的輸出的相位碼作為地址信息不斷對ROM進行尋址,ROM將相位信息轉化為對應的幅值給到A/D轉換器。A/D轉化器將傳輸的二進制數字信號轉化為模擬信號,經濾波器濾波后,形成所需頻率的正弦信號。

2.1 相位累加器

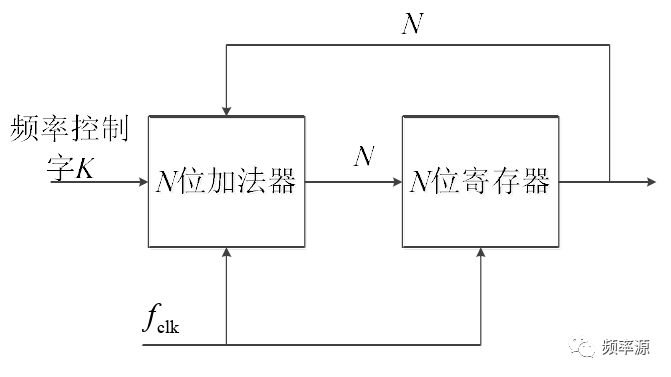

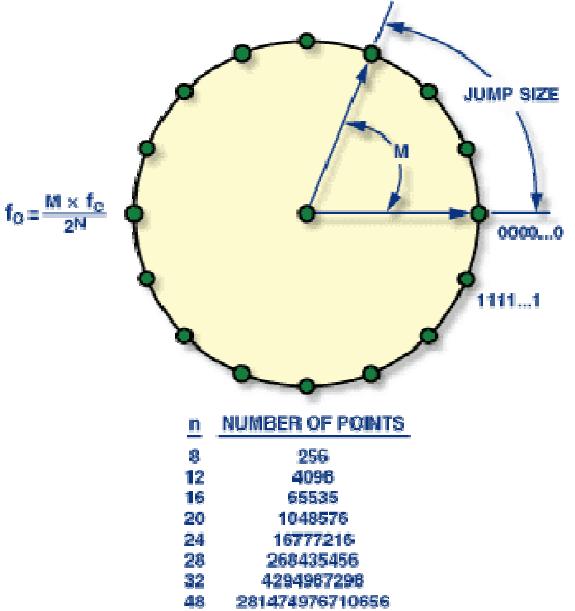

結構中包含一個N位加法器和一個N位寄存器。每當一個參考時鐘脈沖觸發,加法器就會將輸入頻率控制字與寄存器輸出的尋址數據相加,并把相加后的結果送入寄存器進行數據更新。一個N位的相位累加器就可以存儲2^N^個相位點。相位累加器的溢出頻率就是DDS輸出信號的信號頻率。

2.2、波形存儲器

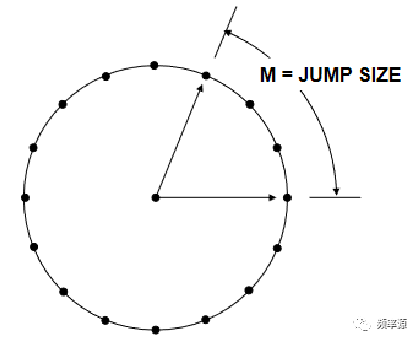

頻率控制字K則是這個尋址序列的“步進”,其決定了在DDS輸出波形的一個周期中包含存儲器中幅值數據的個數。頻率控制字K越高,一個周期中包含的幅值數據越少,DDS輸出波形的頻率越高,波形的質量越差。圖中M=K

2.3、數模轉換器D/A

數模轉換器就是將數字信號轉化為模擬信號。D/A轉換器輸出的階梯波,由于不是標準的正弦波,除開產生所需要的主頻外,還會包含諧波,為了抑制這些諧波和使階梯波更平滑,需要在輸出前加濾波器。

2.4、輸出頻率

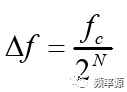

其中N為頻率控制字的長度,K為頻率控制字,fc為參考時鐘的頻率,f0為輸出時鐘的頻率。DDS實際上完成了對參考信號fc的分頻過程,分頻值為2 ^N^ /K。

DDS的性能分析

3.1、頻率分辨率

理想的DDS系統,所以默認頻率控制字長度與波形存儲器、D/A轉換器位寬相同,均取值為N。而在現實設計中,由于波形存儲器存儲位數有限、DAC分辨率有限等原因使得這些位寬并不相同,引起截斷誤差,這也是DDS雜散的來源。目前的頻率控制字長度可達48位,其頻率分辨力可以輕松地達到Hz數量級。

3.2、頻率切換速度

DDS是一個開環系統,與鎖相環系統相比的頻率切換時間極短,與頻譜純度和頻率分辨率互不相干,其頻率切換時間可以達到納秒級別。

3.3、輸出頻率范圍

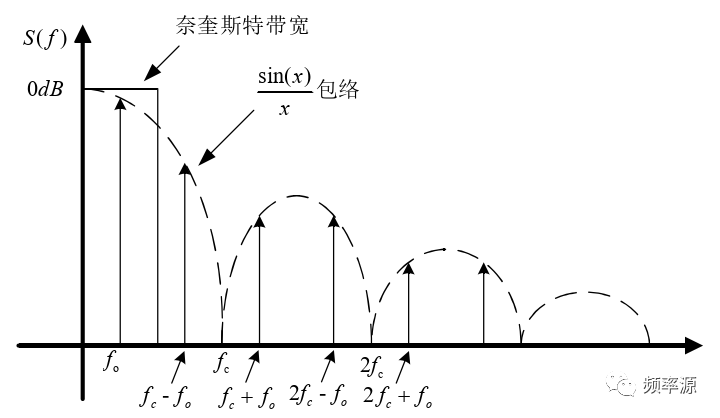

根據奈奎斯特抽樣定理,在DDS中,直接合成的離散信號的抽樣頻率為參考時鐘頻率,要想無失真的將數字離散信號轉換為所需頻率的模擬信號,則DDS的參考時鐘頻率應大于等于輸出頻率的兩倍。為了保證輸出信號的質量,DDS的輸出信號一般要小于參考時鐘頻率的五分之二。

雖然DDS的相對輸出帶寬較寬,能夠達到參考頻率的40%,但同時參考頻率值也限制了的輸出上限。目前,較長使用的芯片的最高參考頻率可達1GHz,輸出頻率最高可為400MHz。

3.4、雜散分析

獨立于輸出信號存在的無用譜稱為雜散。它們一般對稱的出現在頻譜上,其幅度與噪聲相比較高。下圖中理想離散信號的頻譜相比,實際中輸出的頻譜中存在更多的雜散。參考時鐘中存在的雜散,相位截斷誤差,幅度量化誤差以及轉換誤差,都會給的輸出信號帶來雜散。

除上述四種雜散外影響系統輸出雜散的因素還有電路板的布線有關。錯誤的布線會給系統帶來較多的雜散,使其輸出性能下降。

3.5相位噪聲分析

參考時鐘的相位噪聲對輸出信號的相位噪聲影響較大。通常選用相位噪聲很低的晶振作為的參考信號。

-

轉換器

+關注

關注

27文章

8694瀏覽量

147085 -

存儲器

+關注

關注

38文章

7484瀏覽量

163763 -

ROM

+關注

關注

4文章

563瀏覽量

85731 -

DDS

+關注

關注

21文章

633瀏覽量

152630 -

相位累加器

+關注

關注

0文章

10瀏覽量

9184

發布評論請先 登錄

相關推薦

DDS基本原理及性能特點

DDS工作原理是?用DDS芯片AD9858寬帶雷達信號源要設計最佳?

怎么實現基于FPGA+DDS的正弦信號發生器的設計?

DDS,什么是DDS,DDS的結構

DDS是什么意思,DDS結構,DDS原理是什么

基于FPGA的DDS雜散分析及抑制方法

STM32的AD9854 DDS模塊調試總結

DDS的基本原理是什么?DDS的性能分析

DDS的基本原理是什么?DDS的性能分析

評論