想不出來什么無敵炫酷的開頭。我們就直接來吧;

- 1對譯碼器的原理敘述;

- 2關于38譯碼器的撰寫、N位譯碼器的撰寫;

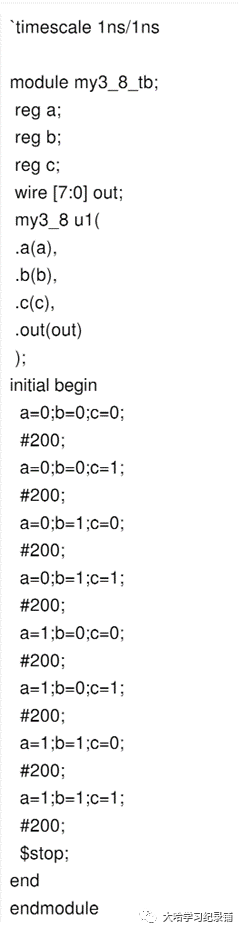

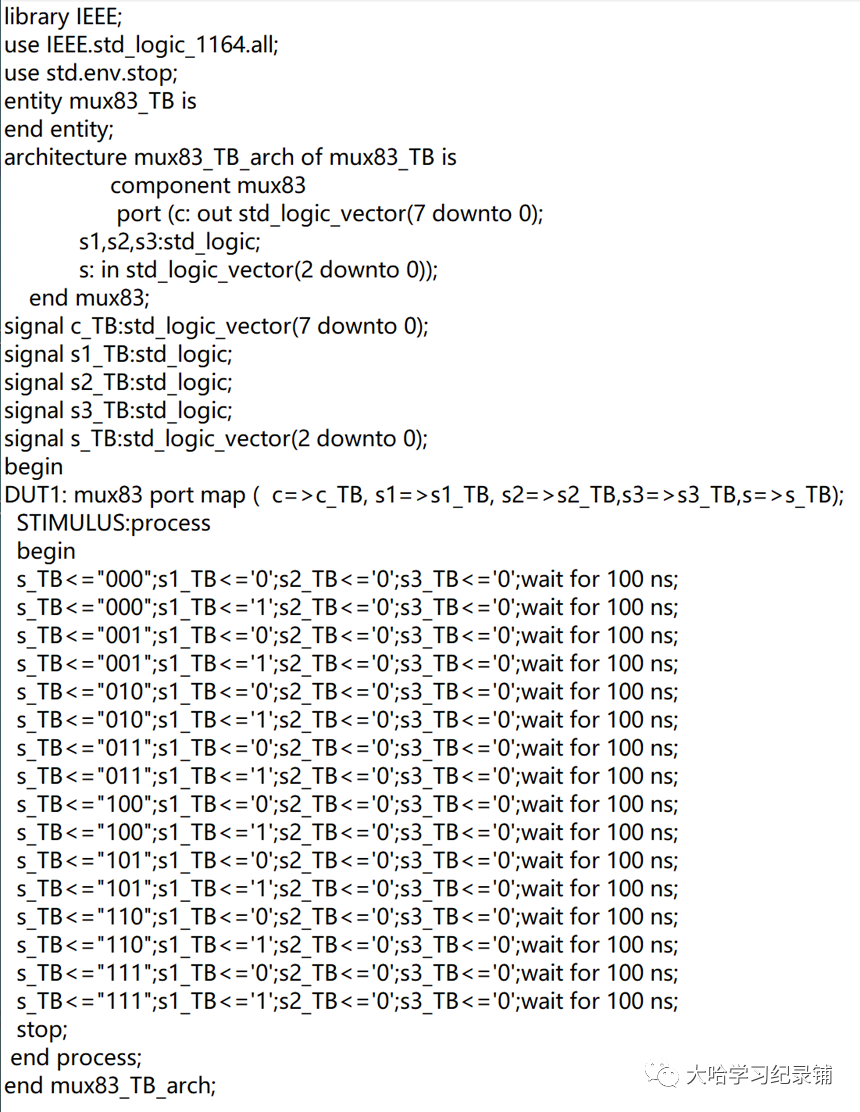

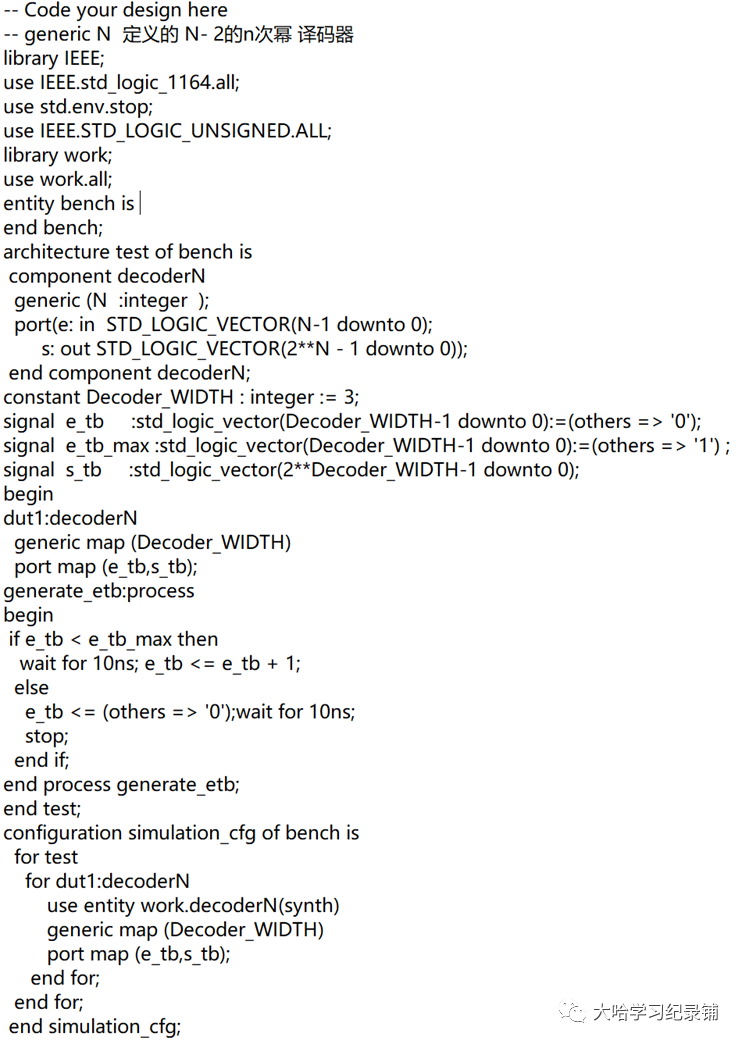

- 3對應測試文本的撰寫;

1.1譯碼器

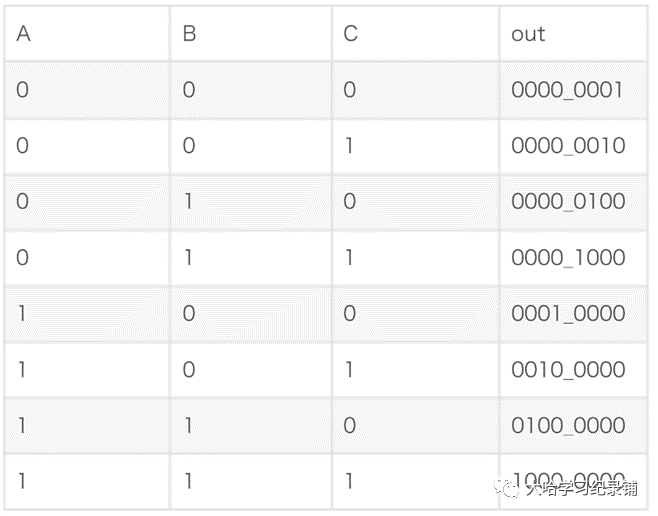

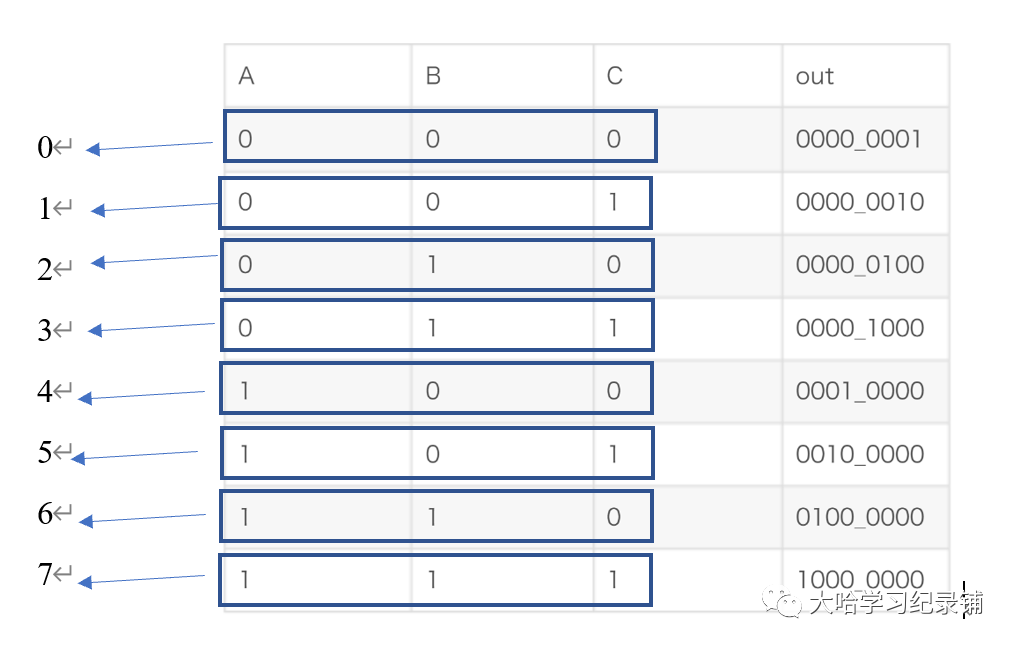

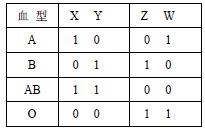

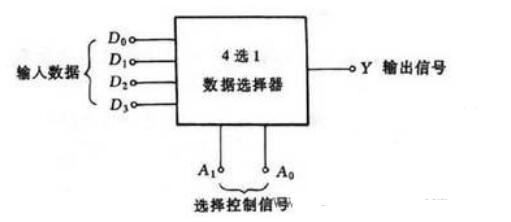

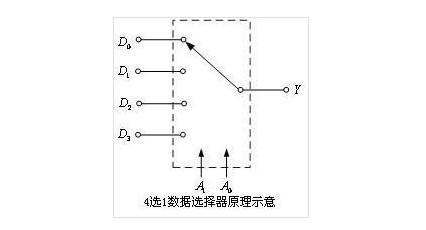

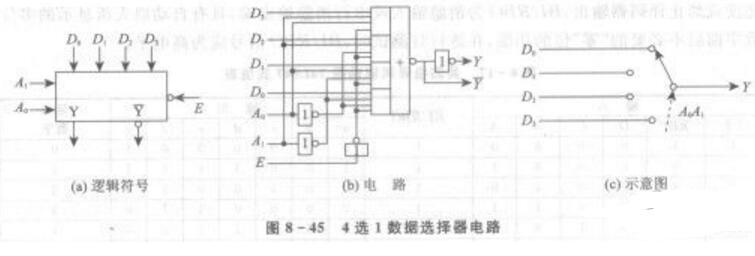

譯碼器就是將每種?進制的組合代碼譯成對應的輸出線上的?低電平信號。用如下表格可以直觀的了解:

其中ABC就是對應了我們的輸入端口;

三個端口組合起來就是三位二進制0-7;

當ABC的值為0時,我們將八位輸出的最低位置1;

當ABC的值為1時,我們將八位輸出的次低位置1;

如此便實現了譯碼器的功能,即輸入端邏輯值為多少,我們就置高輸入端哪一位為高電平(從低位到高位).同時輸出端的位數=2 ^n^ ;(設輸入端位數為n);

1.2譯碼器source文件撰寫

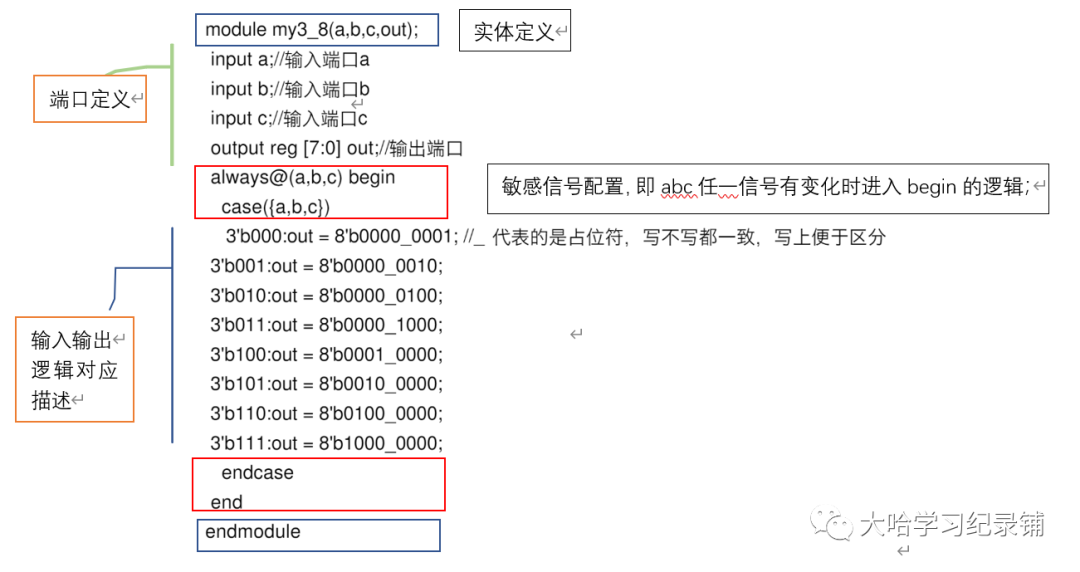

①Verilog以及VHDL如名字所示是一種硬件描述語言,接下來我們就要用verilog去描述出來上述的功能;

以3、8譯碼器為例:

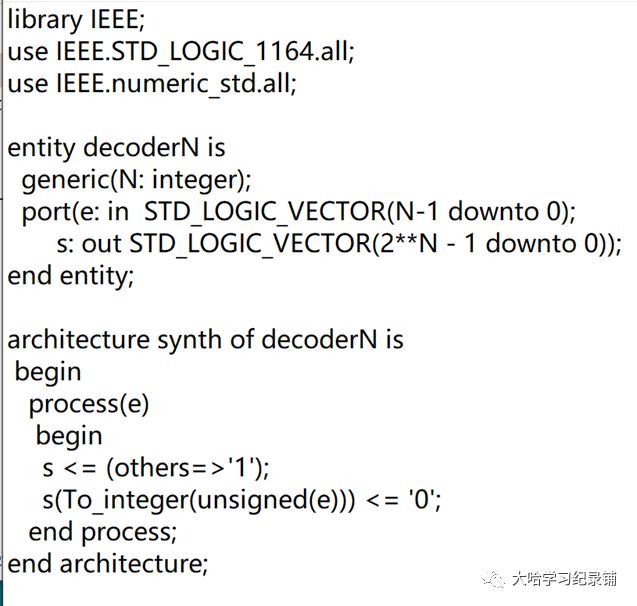

VDHL語言其實和verilog大致相同,大家可以嘗試閱讀一下,主要還是以verilog為主;

②

library IEEE;

use IEEE.std_logic_1164.all;

entity mux83 is

port (

c : out std_logic_vector(7downto 0);

s1,s2,s3:in std_logic;

s : in std_logic_vector(2downto 0));

end mux83;

architecture mux83_arch of mux83 is

begin

p1:process(s,s1,s2,s3)

begin

if(s1='0')then

c<="11111111";

elsif(s1='1' and s2='0' and s3='0')then

cases is

when"000"=> c<="01111111";

when"001"=> c<="10111111";

when"010"=> c<="11011111";

when"011"=> c<="11101111";

when"100"=> c<="11110111";

when"101"=> c<="11111011";

when"110"=> c<="11111101";

when"111"=> c<="11111110";

when others=>c<="11111111";

end case;

else c<="11111111";

end if;

end process p1;

end mux83_arch;

③以及VHDL版本的通用譯碼器:

1.3對應測試文本撰寫

①

②

③

源文件暫時還不知道如何上傳,目前僅供自己總結復習。有任何建議可以小窗私信我哦;

(表格用word畫的,直接截屏使用了,有點粗糙,下次好好整。

這周先這樣兒先這樣兒

-

譯碼器

+關注

關注

4文章

312瀏覽量

51229 -

高電平

+關注

關注

6文章

206瀏覽量

22140

發布評論請先 登錄

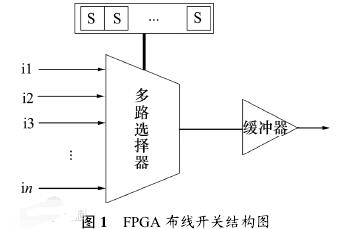

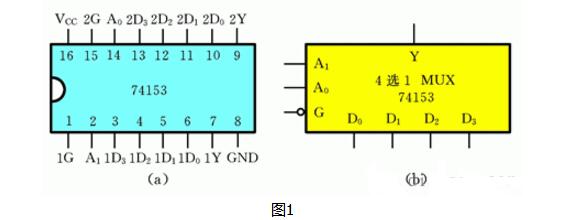

譯碼器及多路選擇器的使用( EDA 仿真) 實驗

數據選擇器作用_數據選擇器和譯碼器的區別

評論