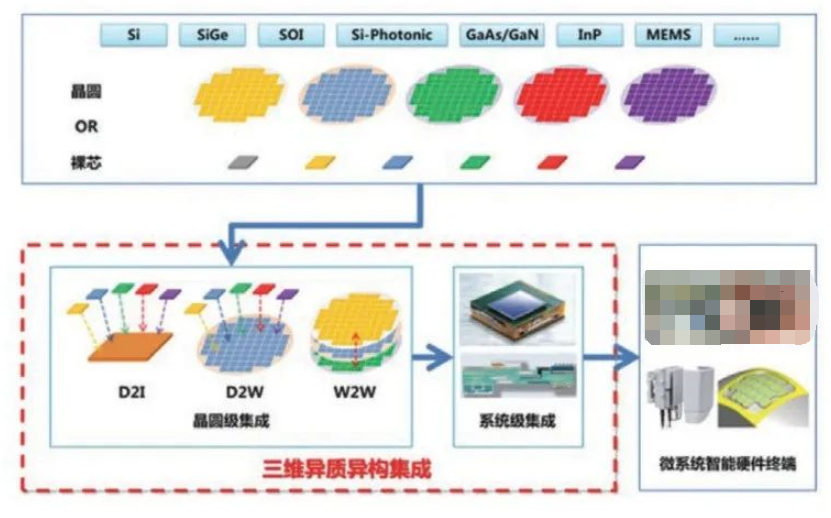

當前,傳統集成電路CMOS 工藝按照“摩爾定律”經過數十年的發展,已經開始邊際收益遞減,表現為引入下一代技術后單個晶體管成本不降反升,性能提升、面積縮小、功耗降低(PPA)放緩。而通過三維異質集成(3D Heterogeneous Integration,3DHI)等先進封裝技術實現系統層面的小型化、多功能化,已成為集成電路技術創新的重要方向之一。

中國工程院院士、浙江大學微納電子學院院長吳漢明曾提出了三條可以突破高算力發展瓶頸的創新途徑,其中就包括三維異質集成晶圓級集成技術(另外兩個創新路徑為存算一體范式、可重構計算架構)。上海科學技術情報研究所也將三維異質集成列為當前全球前沿科技發展的熱點。

總體來看,3DHI 技術具有以下優點:

一是將芯片封裝架構由平面拓展至2.5D 或3D,可實現更小更緊湊的芯片系統;二是可以融合不同的半導體材料、工藝、器件的優點,實現更復雜的功能和更優異的性能;

三是將單芯片系統(SOC)分拆成若干小芯片,簡化了芯片設計復雜度,單個小芯片功能可以單獨優化,提高了芯片設計效率;

四是使用3DHI技術還可以避免芯片(Die)尺寸增大而帶來良率的下降,各個Die可以使用不同的最佳工藝,實現制造成本的降低。

不過,要實現3DHI,集成工藝方面仍需要突破幾個關鍵技術,如:硅通孔(TSV)、晶圓/芯片鍵合技術、散熱等。

21 世紀以來,美國國國防部高級研究局(DARPA)、比利時微電子研究中心(IMEC)等機構支持開展了大量3DHI 的研究項目。DARPA 先后設立硅上化合物半導體材料(COSMOS)、多樣化易用異構集成(DAHI)、通用異構集成及IP復用策略(CHIPS)、下一代微電子制造(NGMM)等項目,持續、系統地支持3DHI 技術研發。

產業鏈各環節企業如日月光、臺積電、英特爾、三星、美光、AMD等均積極布局3DHI 技術,隨著先進封裝工藝與前道制程結合更加緊密,臺積電、英特爾和三星等上游芯片制造企業成為3DHI 技術創新的最重要參與者。

英特爾嘗試通過晶體管、封裝和芯片設計協同優化繼續摩爾定律演進。公司提供嵌入式多芯片互連橋接(EMIB)、Foveros 3D封裝等異質集成技術。EMIB通過一個橋接硅片,將不同芯片組合在一起,可實現50μm-40μm的凸點間距。Foveros 是英特爾開發的晶圓級3D 封裝技術,可以實現在邏輯芯片堆疊,其凸點間距可達50-36μm。此外,英特爾還在研發下一代Foveros Omni和FoverosDirect 技術。前者支持分拆芯片(die disaggregation)設計,為芯片到芯片的互連和模塊化設計提供更高的靈活性;后者實現了由傳統凸點焊接到銅對銅直接鍵合(Hybird bonding)的轉變,可以實現10微米以下的凸點間距,芯片互連密度提高一個數量級。兩項技術計劃在2023年實現量產。

臺積電推出3D Fabric 先進封裝平臺,提供扇入型晶圓級封裝(Fan-in WLP)、整合扇出型封裝(InFO),2.5D片上晶圓基板(CoWoS)封裝,以及3D集成片上系統(SoIC)等封裝技術。臺積電CoWoS 在芯片與基板中間加入硅中介層,實現重新布線及高密度互聯;SoIC采用無凸點(no Bump)直接鍵合技術,實現CoW(Chip on Wafer)、WoW(Wafer on Wafer)直接互連。2020年,臺積電投資100 億美元在中國臺灣地區竹南科學園建設全球首座全自動化3D Fabric先進封裝廠AP6,預計2022年下半年開始生產。2021年2月,臺積電投資186億日元,在日本茨城縣設立半導體材料研發中心,與日本企業合作開展3D IC封裝與散熱相關材料研發。三星的先進封裝平臺包括I-Cube、X-Cube、R-Cube 和H-Cube。I-Cube 是采用硅中介層的2.5D 封裝方案,能夠將一個或多個邏輯芯片(CPU、GPU 等)和多個高帶寬內存(HBM)芯片水平集成在硅中介層上。R-Cube 則是三星的低成本2.5D 封裝方案。H-Cube 是三星電子在2021 年11 月新推出的2.5D 封裝解決方案,專用于需要高性能和大面積封裝技術的高性能計算(HPC)、人工智能等領域。X-Cube 是三星的3D IC 封裝方案(表1)。

表1:主要芯片企業三維異質封裝技術發展概況

在“863計劃”“973計劃”等支持下,中國機構在3DHI方面也取得一系列成果。中國科學院物理研究所解決了硅上異質外延生長Ⅲ-Ⅴ族材料的難題;中科院上海微系統所研制了多種硅基異質材料集成襯底,如:絕緣體上碳化硅、絕緣體上鈮酸鋰、絕緣體上Ⅲ-Ⅴ族等。中芯國際、長電、通富微電、長江存儲、華為海思等企業也在3DHI技術開發、應用方面取得長足進步。長江存儲開發的Xtacking 堆棧技術,將CMOS外圍電路堆疊在NAND芯片下方,構建了高密度、高速存儲結構。而在上游支撐設備及工具軟件方面,也有一批企業實現技術突破。華海清科針對3D IC研制的12英寸晶圓減薄拋光一體機已進入生產驗證;中微半導體的深硅刻蝕機已經應用在歐洲客戶MEMs生產線;上海微電子裝備成功研制出2.5D3D先進封裝***,具有高分辨率、高套刻精度和超大曝光視場等特點,可滿足超大尺寸芯片異構集成的應用需求。芯和半導體是英特爾UCIe聯盟中為數不多的EDA工具企業,公司與新思科技合作開發3D IC封裝設計分析平臺。

審核編輯 :李倩

-

晶圓

+關注

關注

52文章

4956瀏覽量

128178 -

封裝技術

+關注

關注

12文章

551瀏覽量

68008 -

芯片封裝

+關注

關注

11文章

512瀏覽量

30674

原文標題:三維異構集成技術發展的競爭態勢分析

文章出處:【微信號:jbchip,微信公眾號:電子元器件超市】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

世界級專家為你解讀:晶圓級三維系統集成技術

三維觸控技術突破“二向箔”的束縛

廣西掃描服務三維檢測三維掃描儀

三維設計應用案例

三維可視化的應用和優勢

上海黃浦三維媒體動畫技術

基于LTCC技術的三維集成微波組件

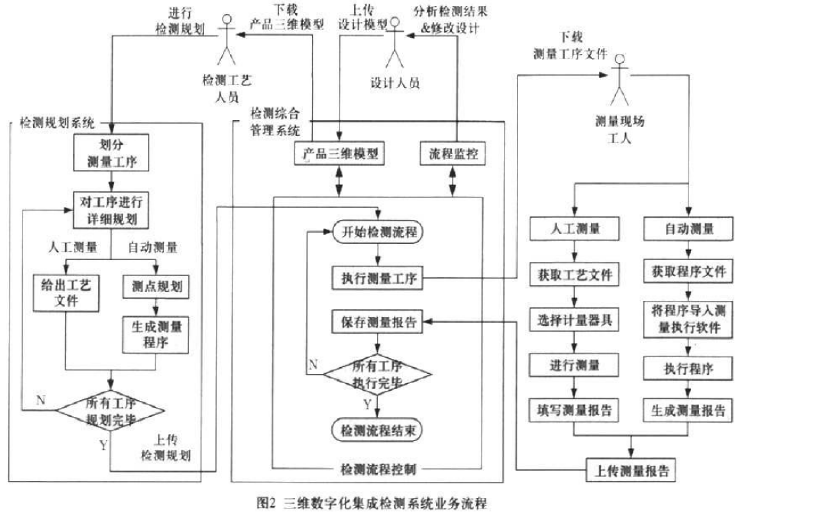

三維數字化集成檢測系統實現關鍵技術分析

三維異構集成技術發展的競爭態勢分析

三維異構集成技術發展的競爭態勢分析

評論