PCB設計四大妙招

據說,每個工程師對PCB設計都有不少有趣的經歷和自家獨特的技術心得。不知道各位小伙伴是怎么看待PCB設計的規則和經驗的呢?今天小編就專門為大家帶來了一份干貨,十分鐘就能教會你PCB設計中的四大竅門,快往下拉~

這份干貨,來自ADI工業與儀器儀表部門的高級系統應用工程師Rob Reeder對于“使用高速轉換器”的四個重要PCB布局布線規則。主要是為了確保設計性能能達到數據手冊的技術規格,因而設計師們必然要遵守一些基本的指導原則。

1

AGND和DGND接地層應當分離嗎?

首先,帶大家來解決一個常見的問題,那就是“AGND和DGND接地層應當的分離嗎?” 詳細的回答是“通常不分離”。因為在大多數情況下,分離接地層只會增加返回電流的電感,因而所帶來的壞處大于好處。從V=L(di/dt)就可以發現:電感增加,電壓噪聲會提高;而開關電流增大,電壓噪聲也同樣會提高。因此,接地層應連在一起。

在一些應用中,為了符合傳統設計要求,必須將臟亂的總線電源或數字電路放在某些區域;同時還受尺寸限制的影響,使得電路板無法實現良好的布局分割,在這種情況下,分離接地層是實現良好性能的關鍵。然而,為使整體設計有效,必須在電路板的某個地方通過一個電橋或連接點將這些接地層連在一起。因此,應將連接點均勻地分布在分離的接地層上。最終,PCB上往往會有一個連接點成為返回電流通過而不會導致性能降低的最佳位置。此連接點通常位于轉換器附近或下方。

設計電源層時,應使用這些層可以使用的所有銅線。如果可能,請勿讓這些層共用走線,因為額外的走線和過孔會將電源層分割成較小的碎塊,從而迅速損害電源層。 由此產生的稀疏電源層可以將電流路徑擠壓到最需要這些路徑的地方,即轉換器的電源引腳。擠壓過孔與走線之間的電流會提高電阻,導致轉換器的電源引腳發生輕微的壓降。

最后,電源層的放置至關重要,切勿將高噪聲的數字電源層疊放在模擬電源層上,否則二者雖然位于不同的層,但仍有可能耦合。為將系統性能下降的風險降至最低,設計中應盡可能將這些類型的層隔開而不是疊加在一起。

2

PCB的輸電系統設計(PDS)可以忽略嗎?

PDS的設計目標是將響應電源電流需求而產生的電壓紋波降至最低。所有電路都需要電流,有些電路需求量較大,有些電路則需要以較快的速率提供電流。采用充分去耦的低阻抗電源層或接地層以及良好的PCB層疊,可以將因電路的電流需求而產生的電壓紋波降至最低。例如,如果設計的開關電流為1A,PDS的阻抗為10mΩ,則最大電壓紋波為10mV。

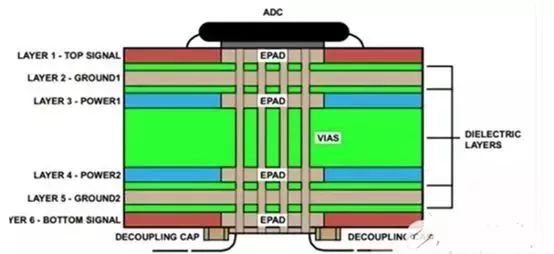

首先,應當設計一個支持較大層電容的PCB層疊結構。例如,六層堆疊可能包含頂部信號層、第一接地層、第一電源層、第二電源層、第二接地層和底部信號層。規定第一接地層和第一電源層在層疊結構中彼此靠近,這兩層間距為2到3密爾,形成一個固有層電容。此電容的最大優點是它是免費的,只需在PCB制造筆記中注明。如果必須分割電源層,同一層上有多個VDD電源軌,則應使用盡可能大的電源層。不要留下空洞,同時也應注意敏感電路。這將使該VDD層的電容最大。如果設計允許存在額外的層(本例中是從六層變為八層),則應將兩個額外的接地層放在第一和第二電源層之間。在核心間距同樣為2到3密爾的情況下,此時層疊結構的固有電容將加倍。

對于理想的PCB層疊,電源層起始入口點和DUT周圍均應使用去耦電容,這將確保PDS阻抗在整個頻率范圍內均較低。使用若干0.001μF至100μF的電容有助于覆蓋該范圍。沒有必要各處都配置電容;電容正對著DUT對接會破壞所有的制造規則。如果需要這種嚴厲的措施,則說明電路存在其它問題。

3

如何利用裸露焊盤實現PCB最佳連接?

1.裸露焊盤

裸露焊盤對充分發揮信號鏈的性能以及器件充分散熱非常重要。裸露焊盤,ADI公司稱之為引腳0,是目前大多數器件下方的焊盤。它是一個重要的連接,芯片的所有內部接地都是通過它連接到器件下方的中心點。不知您是否注意到,目前許多轉換器和放大器中缺少接地引腳,原因就在于裸露焊盤。

將此引腳妥善固定(即焊接)至PCB,可以實現牢靠的電氣和熱連接。如果此連接不牢固,就會發生混亂;換言之,此設計很可能成為設計師不愿看到的無效設計。

2.如何實現最佳連接

利用裸露焊盤實現最佳電氣和熱連接有三個步驟——

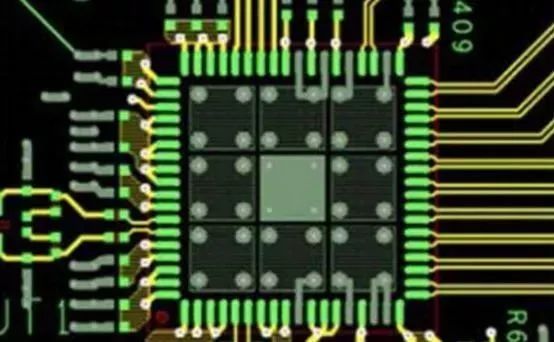

1、在可能的情況下,應在各PCB層上復制裸露焊盤。這樣做的 目的是為了與所有接地和接地層形成密集的熱連接,從而快速散熱。 此步驟與高功耗器件及具有高通道數的應用相關。在電氣方面,這將為所有接地層提供良好的等電位連接。甚至可以在底層復制裸露焊盤(見圖1),它可以用作去耦散熱接地點和安裝底側散熱器的地方。

裸露焊盤布局示例

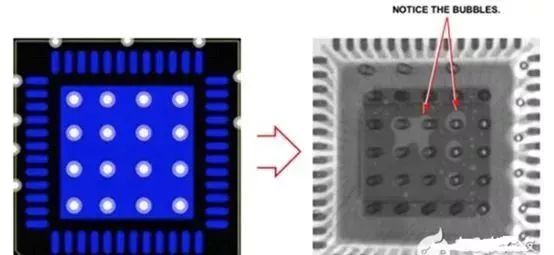

2、**將裸露焊盤分割成多個相同的部分,如同棋盤。**在打開的裸露焊盤上使用絲網交叉格柵,或使用阻焊層。此步驟可以確保器件與PCB之間的穩固連接。在回流焊組裝過程中,無法決定焊膏如何流動并最終連接器件與PCB。連接可能存在,但分布不均。可能只得到一個連接,并且連接很小,或者更糟糕,位于拐角處。將裸露焊盤分割為較小的部分可以確保各個區域都有一個連接點,實現更牢靠、均勻連接的裸露焊盤(見圖2和圖3)。

EPAD布局不當的示例

較佳EPAD布局示例

3、**應當確保各部分都有過孔連接到地。**區域通常都很大,足以放置多個過孔。組裝之前,務必用焊膏或環氧樹脂填充每個過孔,這一步非常重要,可以確保裸露焊盤焊膏不會回流到這些過孔空洞中,影響正確連接。

4

PCB各層面間的交叉耦合真的無關緊要嗎?

在PCB設計中,一些高速轉換器的布局布線不可避免地會出現一個電路層與另一個交疊的情況。某些情況下,敏感的模擬層(電源、接地或信號)可能就在高噪聲數字層的正上方。因為這些層面位于不同的層,所以無關緊要?我們來看一個簡單的測試。

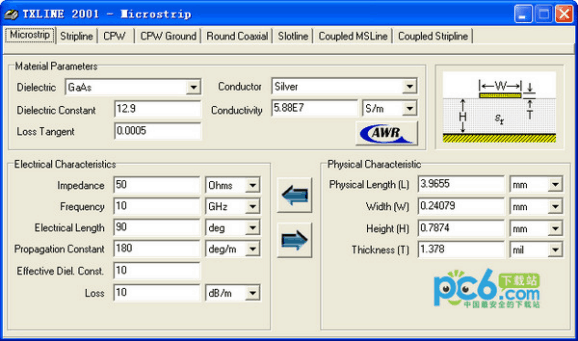

選擇相鄰層中的一層,并在該層面注入信號。然后,將交叉耦合層連接到一個頻譜 分析儀。可以看到,耦合到相鄰層的信號非常多。即使間距40密爾,某種意義上相鄰 層仍會形成一個電容,因此在某些頻率下,信號仍會從一個層耦合到另一個層。

假設某層上的高噪聲數字部分具有高速開關的1V信號,層間隔離為60dB時,非受驅層將看到從受驅層耦合而來的1mV信號。對于2Vp-p滿量程擺幅的12位模數轉換器 (ADC)而言,這意味著2LSB(最低有效位)的耦合。對于特定的系統,這可能不成問題, 但應注意,當分辨率從12位提高到14位時,靈敏度會提高四倍,因而誤差將增大到8LSB。

忽略交叉面/交叉層耦合可能不會導致系統設計失敗,或者削弱設計,但必須保持警惕,因為兩個層面之間的耦合可能比想象的要多。

在目標頻譜內發現噪聲雜散耦合時,應注意這一點。有時候,布局布線會導致非預期 信號或層交叉耦合至不同層。調試敏感系統時請記住這一點:問題可能出在下面一層。

-

開關電源

+關注

關注

6493文章

8514瀏覽量

487670 -

PCB設計

+關注

關注

396文章

4755瀏覽量

88704 -

PCB

+關注

關注

1文章

1953瀏覽量

13204

發布評論請先 登錄

高頻PCB設計需要注意的細節

PCB射頻電路四大基礎特性

PCB設計培訓

pcb設計基礎之穩壓原理簡述

高頻PCB設計中,工程師需考慮四個方面帶來的干擾問題并給解決方案

從四個方面解讀PCB射頻電路基礎特性及重要因素

PCB設計中應避免的四個技術問題

pcb設計四個步驟

ADC的PCB設計,告訴你四個關鍵技巧!

評論