如何提供高品質穩定的電源輸出以及豐富的數字調節監測功能,提升效率是多相電源芯片的關鍵技術。

普通單相 Buck變換器難以滿 足CPU大負荷瞬間的大電流需求,會有過大的應力導致器件發熱嚴重、使用壽命縮短、效率降低。且在發生大電流跳變時,單相Buck變換器受限于單電感的壓擺率,導致 瞬 態 響 應 較 慢。

而能將大電流分散的多相Buck變換器可有效解決上述問題。美國西屋制動和信號公司在1967年首次提出多相并聯直流變換器的概念。

研究人員對此展開了 相關研究。2005年,P.Hazucha等人提出了一種 應用于微處理器的全集成4相Buck變換器,工作頻率高達233MHz,在0.3A 的負載情況下,峰值效率 達到83.2%。2022年,J.H.Cho等 人提 出 了 一 種工作頻率高達400MHz的全集成6相Buck變換器,可實現高精度的電感電流間平衡和快速的動態電壓調整(DynamicVoltageScaling,DVS),在1.8A的負載情況下達到了83.7%的峰值效率。德州儀 器(TI)、英 特 爾 (Intel)及蘋 果的電源芯片供應商 Dialog等IC公司都有自己的多相Buck變換器方案,每年都會有相應的產品發布。

什么是多相Buck電源?

應用場景

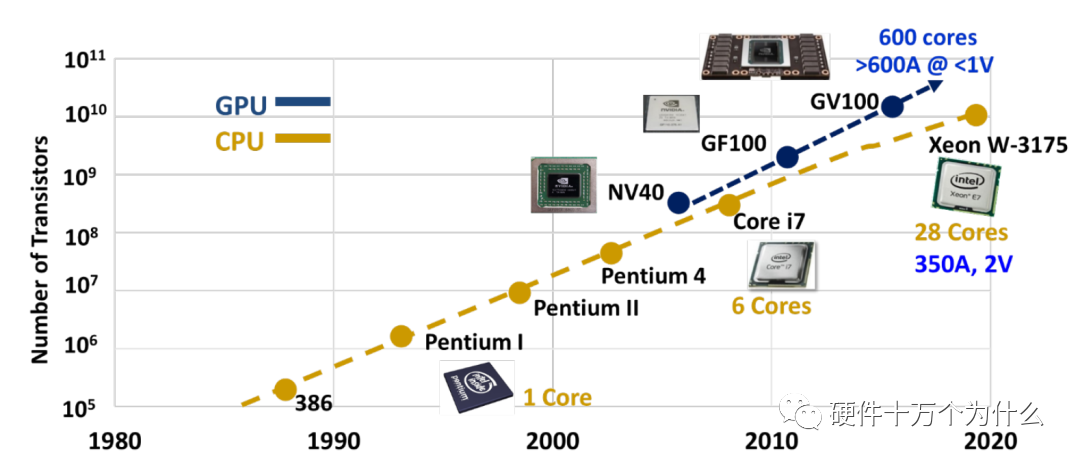

大數據,云計算,人工智能概念的興起,通信基站,數據中心等基建設施及汽車電動智能化催生出的自動駕駛等終端應用都需要耗電更大的CPU,GPU及ASIC來支持更為強勁的算力需求。這對供電電壓調節器模塊 (VRM/Vcore) 和負載點電源 (PoL) 提出了嚴峻挑戰,包括:更高的效率、更高的功率密度,同時滿足處理器di/dt>1000A/us瞬態響應要求。

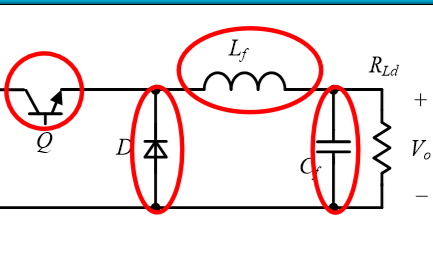

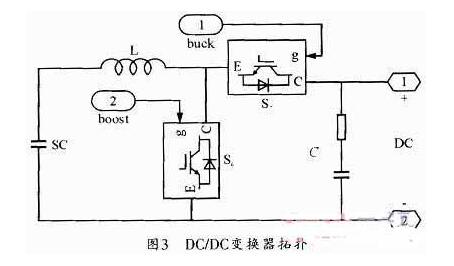

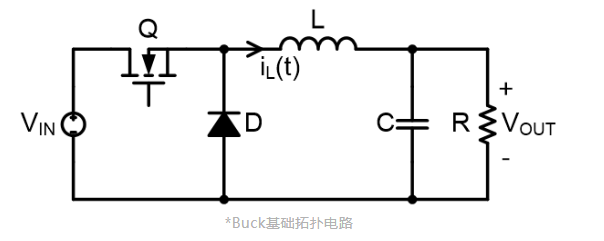

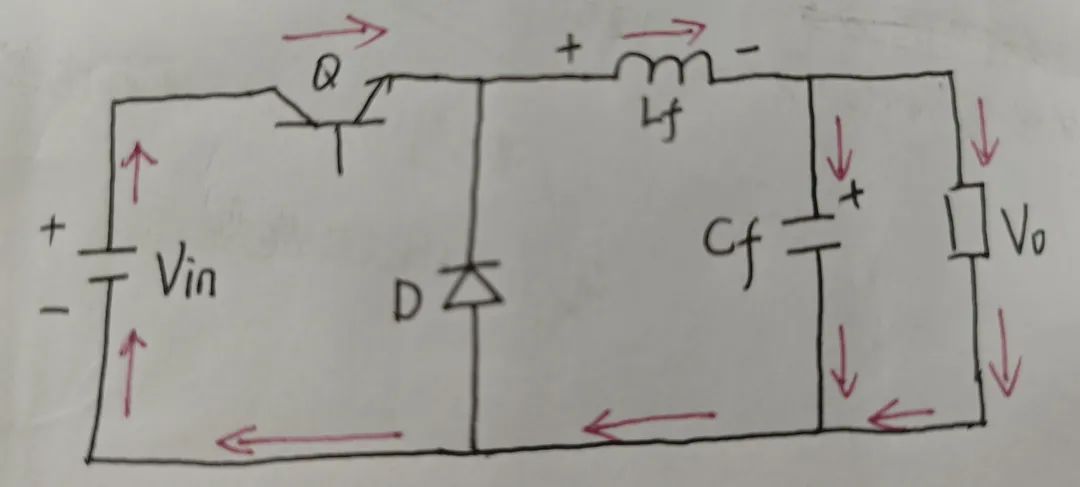

拓撲架構

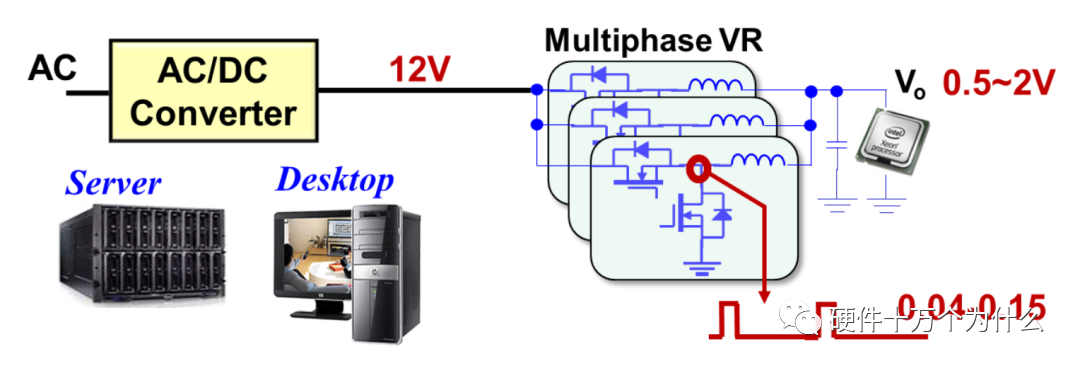

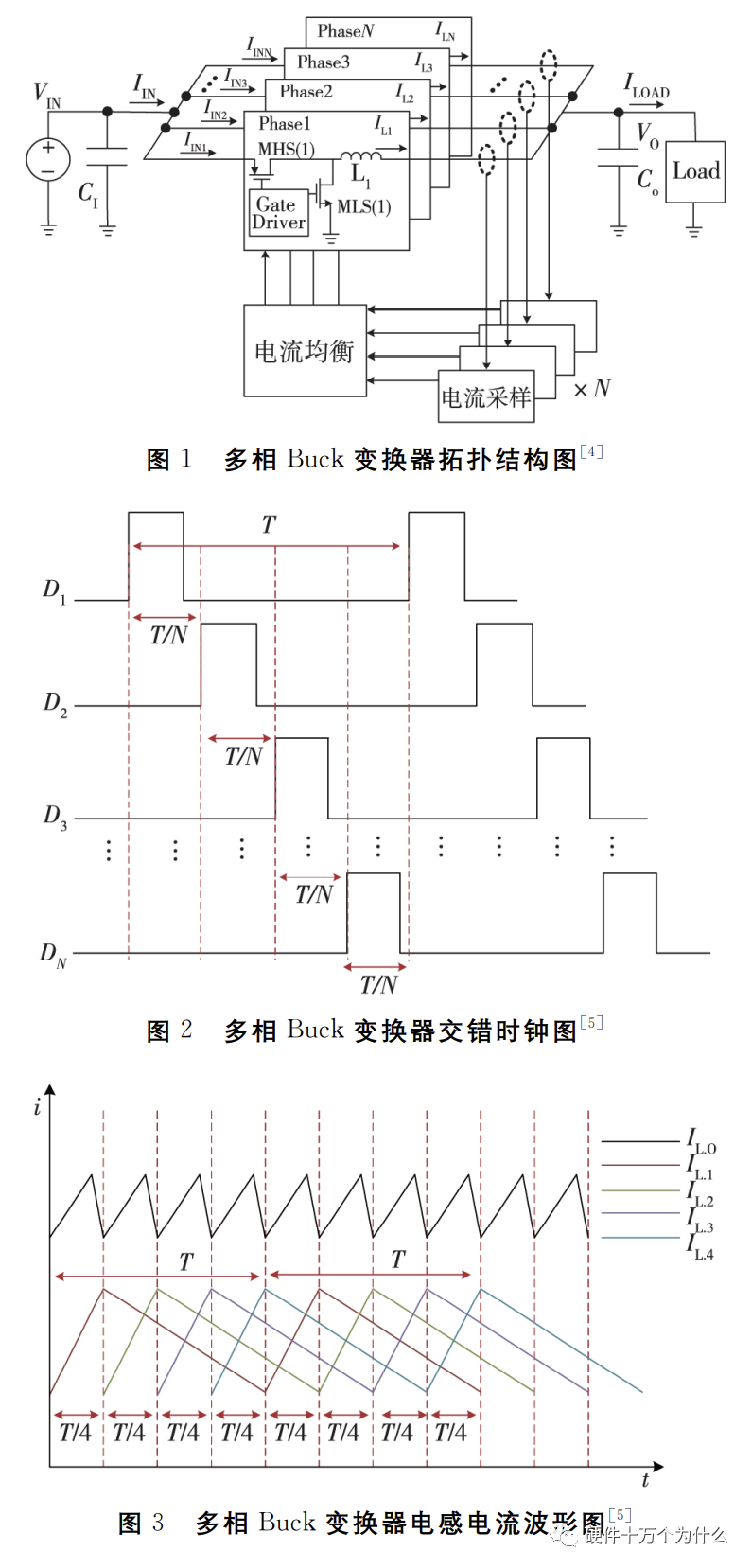

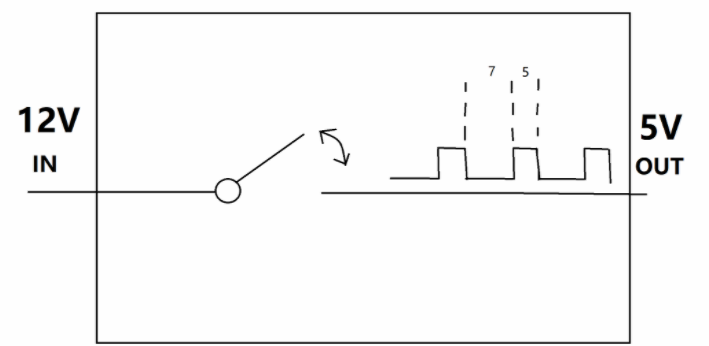

常說的多相Buck電源包含控制器和DrMOS,是一種多路交錯并聯的同步Buck拓撲,被公認為是此類應用場景的最佳解決方案。以廣泛應用的12V直流母線,轉換到核心類負載所需較低電壓 (0.5V~2V) 的場合為例,其基于多相Buck的小占空比供電架構方案如下。

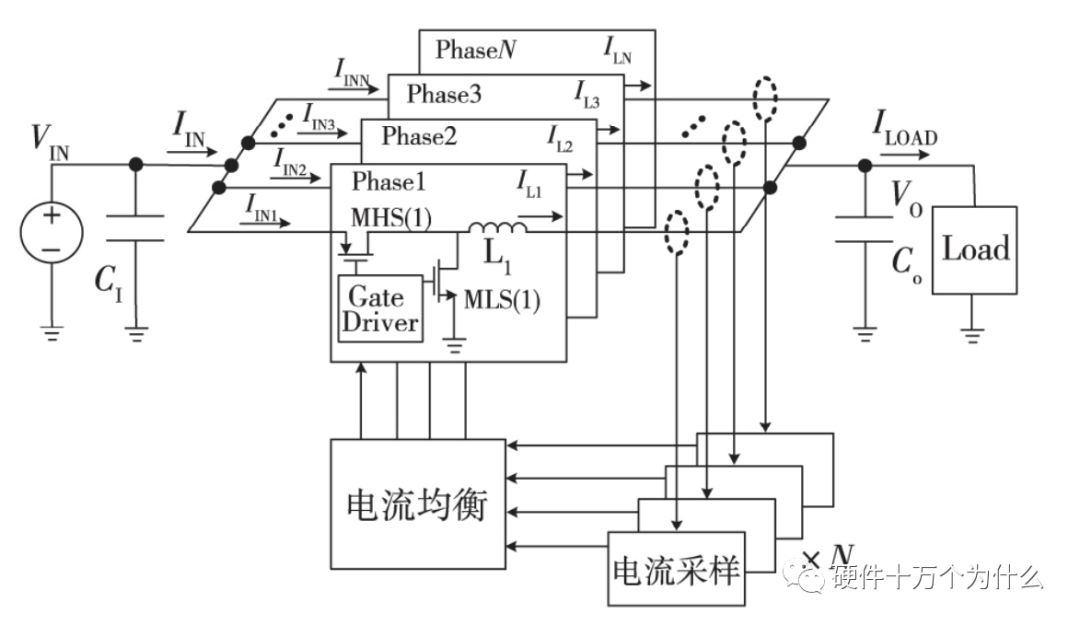

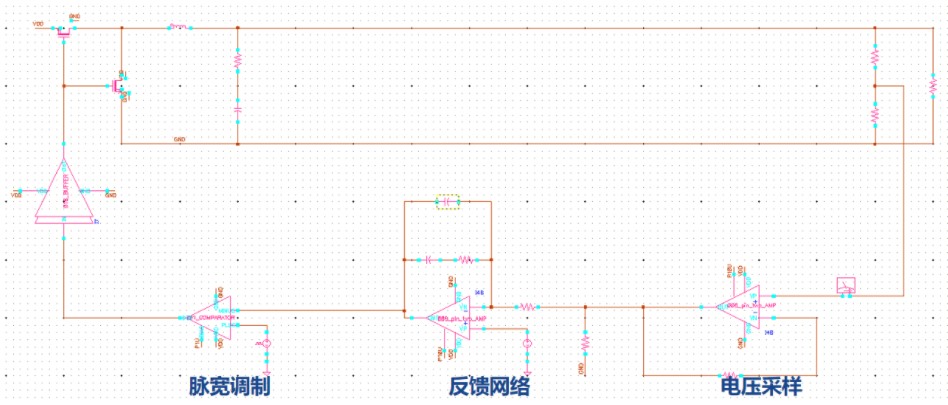

每相Buck對應的半橋MOSFET可由包含驅動和溫度/電流檢測的DrMOS代替,由一個控制器采集反饋的電壓、電流、溫度/錯誤等信號,并發出各PWM波實現功率的閉環控制。控制器可通過特定協議的通信接口 (如PMBus,AVSBus,SVID,SVI2/3,PWM-VID等) 和信號指示IO口,與系統上位機或負載處理器進行信號交互。

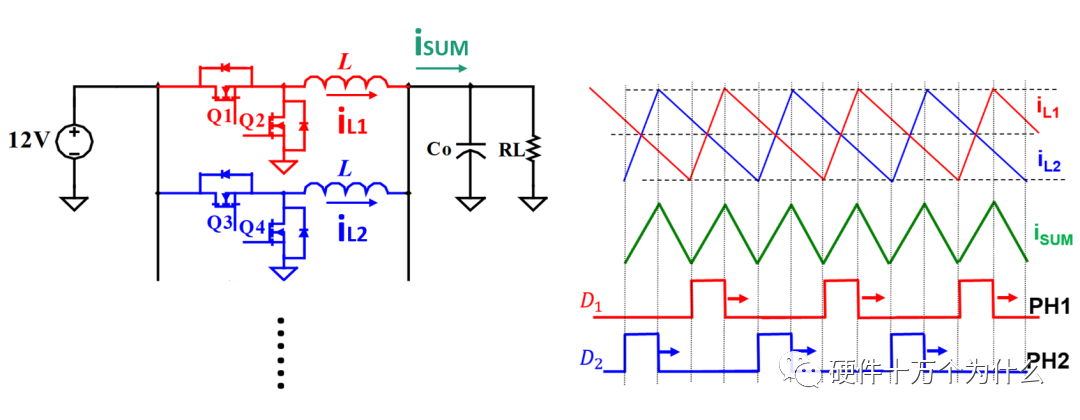

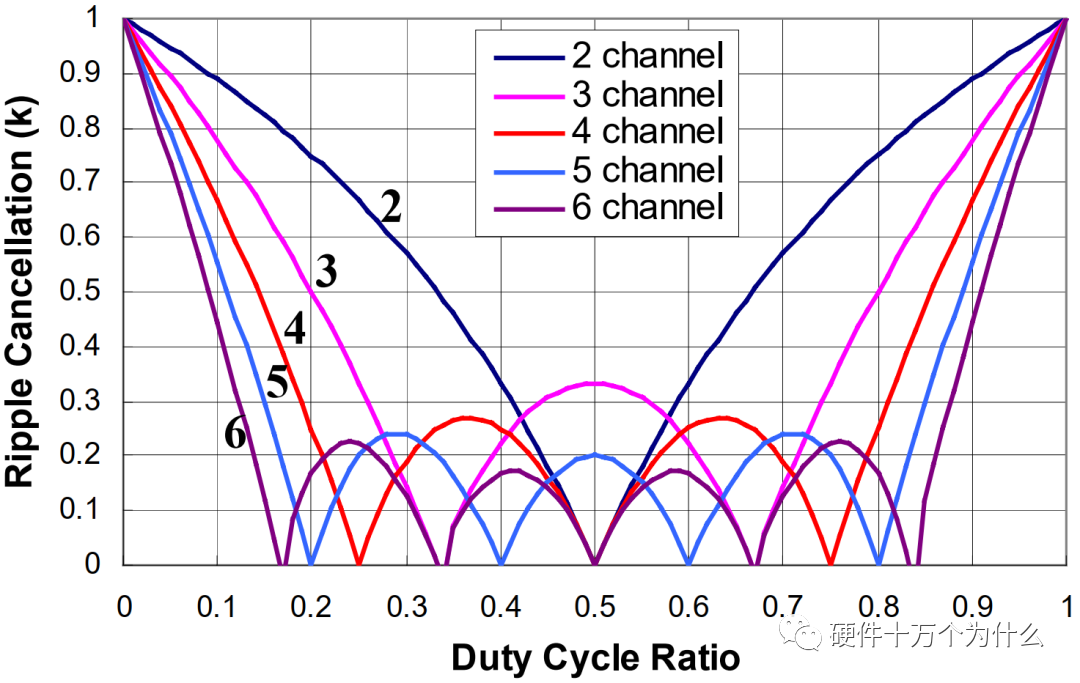

以兩相Buck交錯并聯運行為例,波形之間的關系如下所示。

當相數繼續增加時,隨著占空比變化會產生不一樣的紋波抵消效果。紋波抵消率k為isum的紋波峰峰值與iL的紋波峰峰值的比值,它隨著相數和占空比的變化關系如下。

動態響應及自適應電壓定位

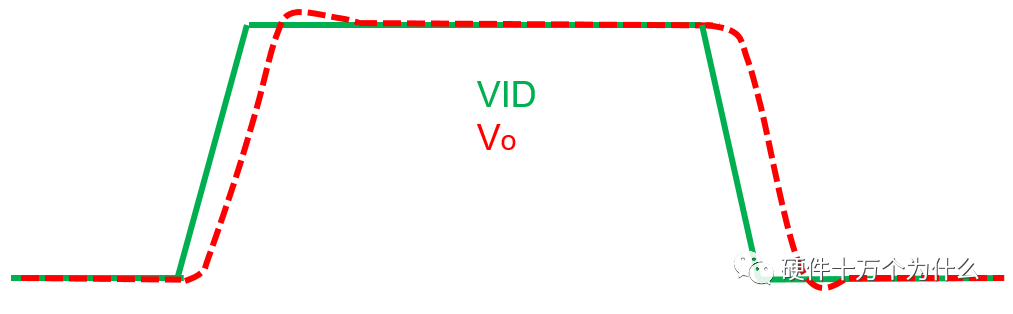

多相VRM/PoL應用中,動態響應包含動態電壓識別 (DVID) 和動態負載。

當VID目標參考電壓以設置的斜率動態變化時,控制器需要立即響應控制PWM發波,以使得輸出電壓有能力緊密跟蹤VID的變化。

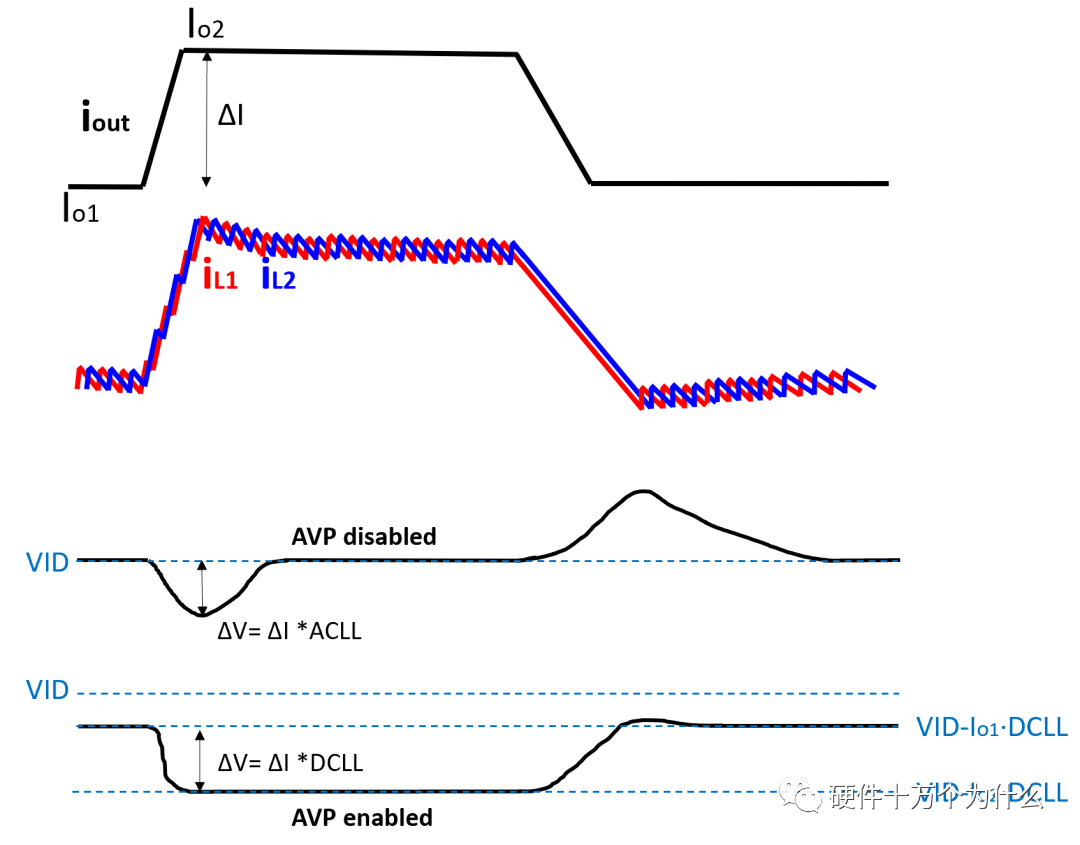

動態加減載時,負載電流從Io1跳變至Io2,持續一段時間后又恢復,輸出電壓會相應地出現波動。環路未飽和情況下,變化的電壓v,它與電流i之比,可定義為AC Load-Line (ACLL)。從幅值的角度去看,電壓波動ΔV與電流擺幅ΔI,近似滿足:

ΔV/ΔI≈ACLL

在CPU應用中,經常使用自適應電壓定位技術(Adaptative Voltage Positioning, AVP),優化動態響應中電壓波動的峰峰差值。AVP開啟的情況下,多相控制器可根據當前的輸出電流Iout大小,將VID目標參考電壓自適應下調,下調的電壓ΔVID與輸出電流Iout之比,定義為DC Load-Line (DCLL)。

ΔVID/Iout=DCLL

當DCLL=ACLL時,電壓波動的峰峰值可降低約一半,因此在保證同樣電壓波動的情況下,AVP功能可節省輸出濾波電容的用量。

架構優勢

綜上所述,多相Buck電源的架構優勢有:

? 每一相發波相位交錯,穩態電感電流的波形峰谷一定程度上相互抵消,提高等效開關頻率,減小了輸入和輸出的電流紋波和電壓紋波;

? 每一相可使用更小感值和體積的電感,并聯情況下通過占空比重疊,可實現更高的di/dt,和更快的動態響應;

? 采用耦合電感技術后可繼續放大上述優勢;

? 方便的輕載高效管理,可簡單通過關閉某幾相實現,即自動切相;

? 并聯更多相數可方便拓展輸出電流,且實現分散的熱源壓力,分布式散熱管理。

-

電源

+關注

關注

184文章

17704瀏覽量

249964 -

cpu

+關注

關注

68文章

10854瀏覽量

211587 -

電感

+關注

關注

54文章

6136瀏覽量

102298 -

Buck變換器

+關注

關注

3文章

78瀏覽量

18247

發布評論請先 登錄

相關推薦

BUCK電路的工作原理

Buck電路的工作原理

Buck電路的工作原理

介紹BUCK降壓電路的基本工作原理

Buck變換器的工作原理與設計的學習課件免費下載

buck電路的含義及工作原理

簡述多相Buck電路的工作原理

簡述多相Buck電路的工作原理

評論