一、MOSFET功耗

Buck電路的損耗,主要發生在功率路徑上,也就是較大電流通過的器件上:MOSFET、電感、二極管(非同步控制器)。

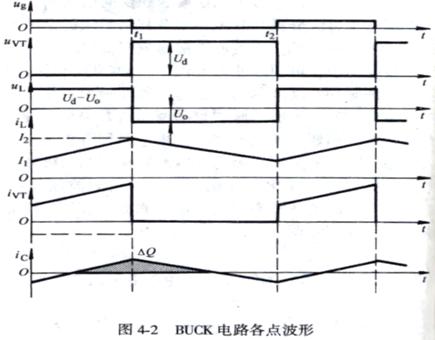

根據Buck電路的幾個工作階段,我們分別討論MOSFET的損耗

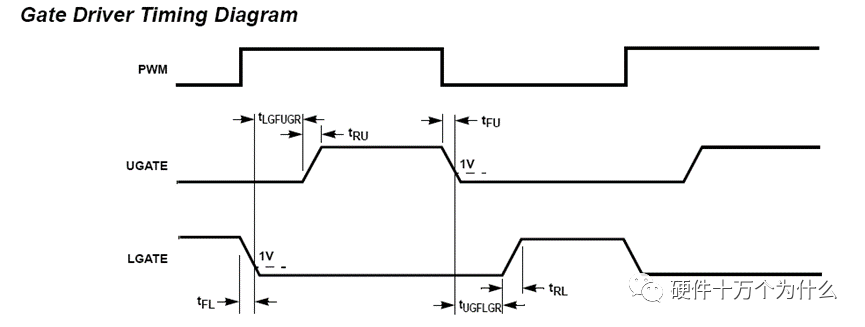

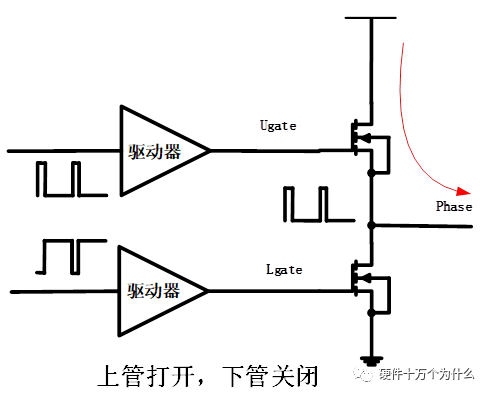

第一個階段:上管打開的過程:

在開關過程中產生的損耗,MOSFET處于放大區,下管關閉幾乎沒有電流。

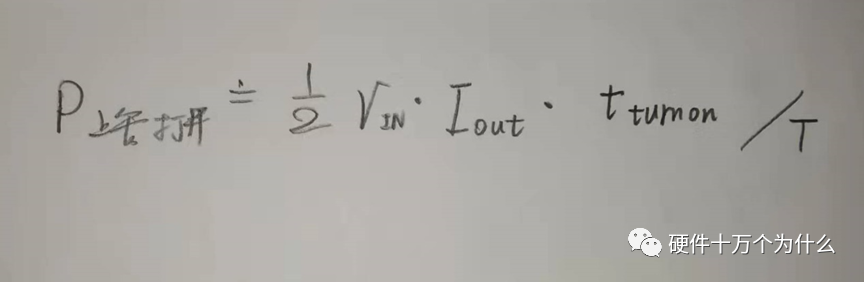

在上管打開過程中,上管的電壓Vds不斷減小,電流Ids不斷增加。我們簡單地可以認為是線性增減。此時輸出電流處于谷底,最小值。如果近似的看成是電流平均值即輸出電流值,則可以簡單計算如下:

如果需要考慮電流紋波,則計算公式如下:

第二個階段:上管完全導通、下管關閉。

上管MOSFET處于打開狀態,上MOSFET等效于一個電阻即為MOSFET的導通阻抗Rds(on),Rds(on)上面流經電流的損耗。此時,下管沒有電流,功耗全部集中在上管上。

打開的時間是由占空比決定的:上管打開的時間約等于T*D。

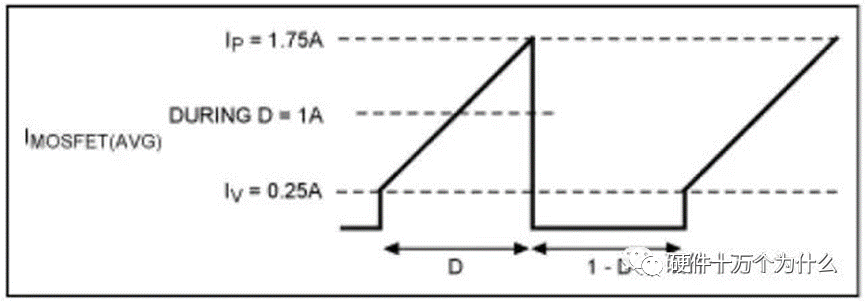

電流近似計算時,可以看作就是Buck電源的輸出電流。如果細算起來,就需要考慮在上管打開過程中,電流是逐步變大的,我們需要對這個電流增大的過程進行積分計算,考慮到電流逐步變大的過程。

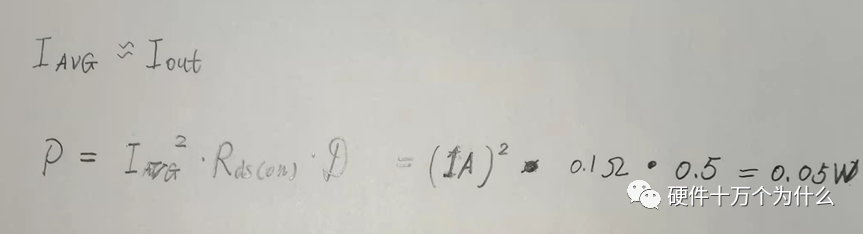

如果電流紋波足夠小,我們可以近似認為上管打開過程電流沒變化。則這個計算非常容易,就是直接計算,就可以:

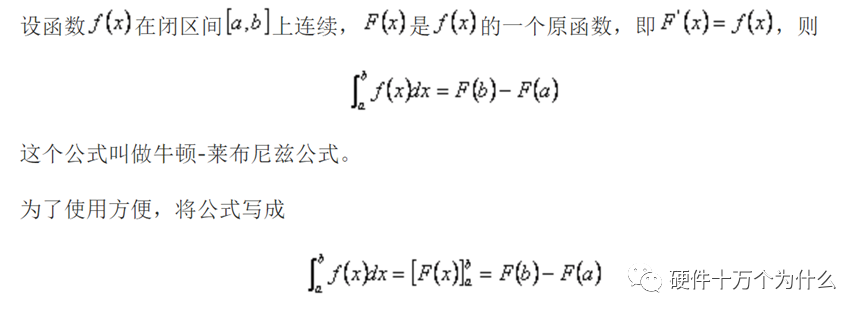

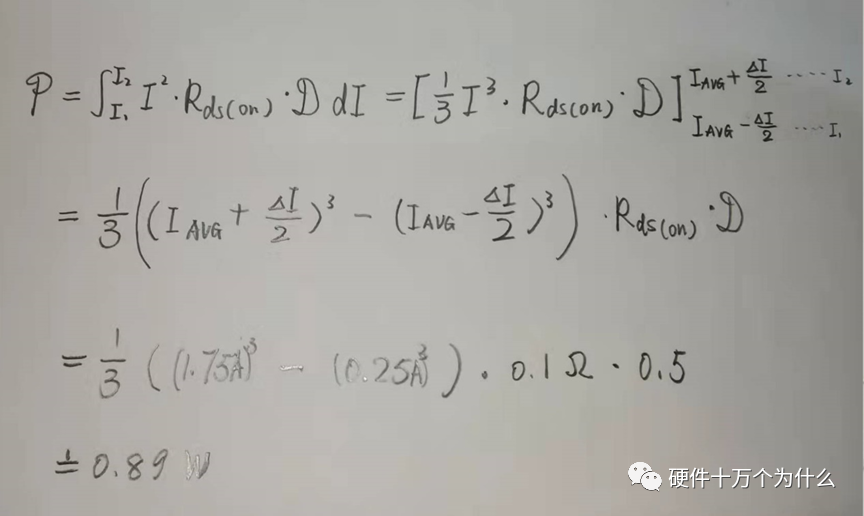

如果紋波帶來的影響不可忽略,則我們需要進行積分運算。我們從開始開啟的電流進行積分,即最小電流處,積分到最大電流處。此處運用牛頓-萊布尼茲公式,計算定積分。

第三個階段,上管關閉的過程

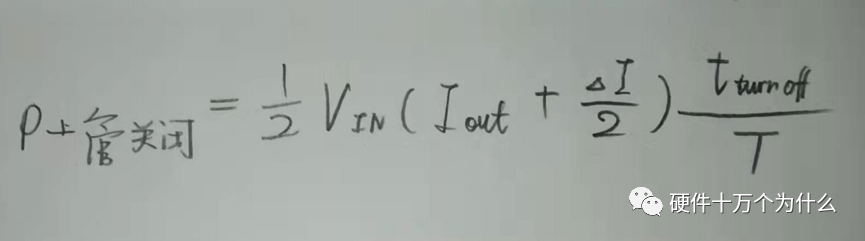

上管打開的過程和關閉的過程是類似的計算方法,此處只是電流為整個周期的最大值,因為經歷了一個充電的過程,電流此時處于峰值。另外就是上管關閉的時間,會與上管打開的時間不一樣。我們計算公式如下:

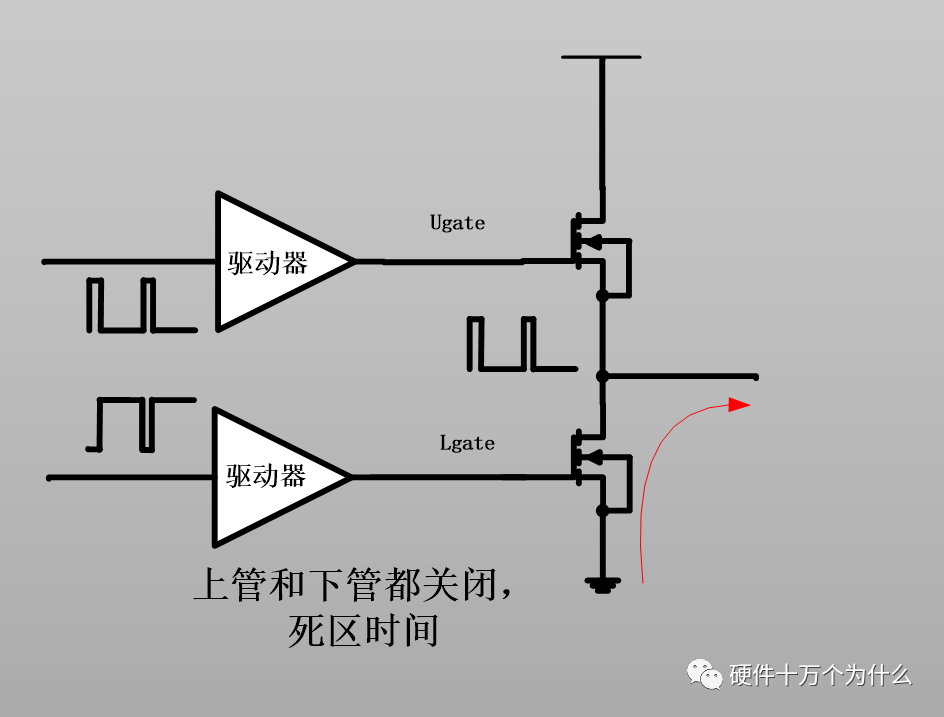

第四個階段,此時上管已經完全關閉,下管暫時還沒有打開,稱為死區時間

我們需要理解,任何控制器都需要控制避免上下管同時打開,如果出現這個狀態,則非常可能燒管,因為相當于通過上下管把輸入電源和GND進行了短路。

為了避免這種狀態,只好在上管關閉之后,等待一個時間段,再對下管進行打開的操作。而在兩個MOSFET都關閉的狀態,我們就稱為死區時間。這個時間,主要依賴下管的寄生二極管進行續流,實現輸出電流的一個回路。

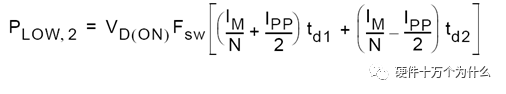

此時的功耗,就是下管的寄生二極管的功耗,也就是二極管的正向導通壓降乘以此時的電流。在開關開關的過程中,會有兩個階段經歷死區時間,所以下管的死區時間功耗計算公式如下:

第五階段,下管導通

導通功耗,因為很顯然下管的功耗是在電流通過MOS的DS溝道之間的電阻(rDS(ON))產生的。下面公式可估算下MOS管的導通功耗。

下管的導通損耗,近似的可以看作是:

如果考慮紋波,可以用以下公式進行計算:

1) 占空比 (高側FET,上管) = Vout/(Vin*效率)

2) 占空比 (低側FET,下管) = 1 – DC (高側FET)

FET 可能會集成到與控制器一樣的同一塊芯片中,從而實現一種最為簡單的解決方案。但是,為了提供高電流能力及(或)達到更高效率,FET 需要始終為控制器的外部元件。這樣便可以實現最大散熱能力,因為它讓FET物理隔離于控制器,并且擁有最大的 FET 選擇靈活性。它的缺點是 FET 選擇過程更加復雜,原因是要考慮的因素有很多。

一個常見問題是“為什么不讓這種 10A FET 也用于我的 10A 設計呢?”答案是這種 10A 額定電流并非適用于所有設計。

選擇 FET 時需要考慮的因素包括額定電壓、環境溫度、開關頻率、控制器驅動能力和散熱組件面積 。關鍵問題是,如果功耗過高且散熱不足,則 FET 可能會過熱起火。我們可以利用封裝/散熱組件 ThetaJA 或者熱敏電阻、FET 功耗和環境溫度估算某個 FET 的結溫,具體方法如下:

3) Tj = ThetaJA * FET 功耗(PdissFET) + 環境溫度(Tambient)

它要求計算 FET 的功耗。這種功耗可以分成兩個主要部分:AC 和 DC 損耗。這些損耗可以通過下列方程式計算得到:

4) AC損耗: AC 功耗(PswAC) = ? * Vds * Ids * (trise + tfall)/Tsw

其中,Vds 為高側 FET 的輸入電壓,Ids 為負載電流,trise 和 tfall 為 FET 的升時間和降時間,而Tsw 為控制器的開關時間(1/開關頻率)。

5) DC 損耗: PswDC = RdsOn * Iout * Iout * 占空比

其中,RdsOn 為 FET 的導通電阻,而 Iout 為降壓拓撲的負載電流。

其他損耗形成的原因還包括輸出寄生電容、門損耗,以及低側 FET 空載時間期間導電帶來的體二極管損耗,但在本文中我們將主要討論 AC 和 DC 損耗。

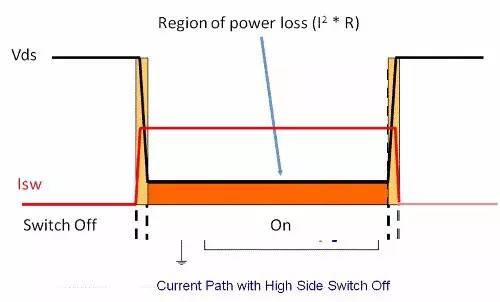

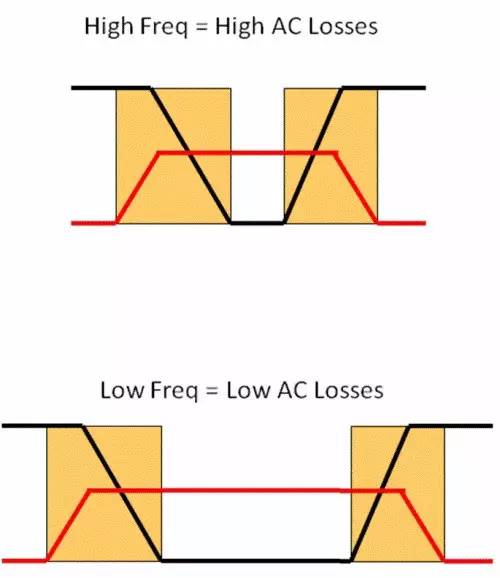

開關電壓和電流均為非零時,AC 開關損耗出現在開關導通和關斷之間的過渡期間。圖 2 中高亮部分顯示了這種情況。根據方程式 4),降低這種損耗的一種方法是縮短開關的升時間和降時間。通過選擇一個更低柵極電荷的 FET,可以達到這個目標。另一個因素是開關頻率。開關頻率越高,升降過渡區域所花費的開關時間百分比就越大。因此,更高頻率就意味著更大的AC開關損耗。所以,降低 AC 損耗的另一種方法便是降低開關頻率,但這要求更大且通常也更昂貴的電感來確保峰值開關電流不超出規范。

AC 損耗圖

開關頻率對 AC 損耗的影響

開關處在導通狀態下出現 DC 損耗,其原因是 FET 的導通電阻。這是一種十分簡單的 I2R 損耗形成機制。但是,導通電阻會隨 FET 結溫而變化,這便使得這種情況更加復雜。所以,使用方程式 3)、4)和 5)準確計算導通電阻時,就必須使用迭代方法,并要考慮到 FET 的溫升。降低 DC 損耗最簡單的一種方法是選擇一個低導通電阻的 FET。另外,DC 損耗大小同FET 的百分比導通時間成正比例關系,其為高側 FET控制器占空比加上 1 減去低側 FET 占空比,如前所述。 我們可以知道,更長的導通時間就意味著更大的DC 開關損耗,因此,可以通過減小導通時間/FET 占空比來降低 DC 損耗。例如,如果使用了一個中間 DC 電壓軌,并且可以修改輸入電壓的情況下,設計人員或許就可以修改占空比。

DC 損耗圖

占空比對 DC 損耗的影響

盡管選擇一個低柵極電荷和低導通電阻的 FET 是一種簡單的解決方案,但是需要在這兩種參數之間做一些折中和平衡。低柵極電荷通常意味著更小的柵極面積/更少的并聯晶體管,以及由此帶來的高導通電阻。另一方面,使用更大/更多并聯晶體管一般會導致低導通電阻,從而產生更多的柵極電荷。這意味著,FET 選擇必須平衡這兩種相互沖突的規范。另外,還必須考慮成本因素。

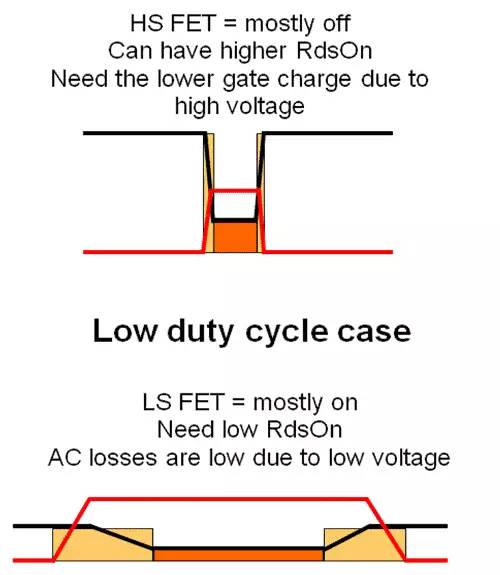

低占空比設計意味著高輸入電壓,對這些設計而言,高側 FET 大多時候均為關斷,因此 DC 損耗較低。但是,高 FET 電壓帶來高 AC 損耗,所以可以選擇低柵極電荷的 FET,即使導通電阻較高。低側 FET 大多數時候均為導通狀態,但是 AC 損耗卻最小。這是因為,導通/關斷期間低側 FET 的電壓因 FET 體二極管而非常的低。因此,需要選擇一個低導通電阻的 FET,并且柵極電荷可以很高。

低占空比設計的高側和低側 FET 功耗

如果我們降低輸入電壓,則我們可以得到一個高占空比設計,其高側 FET 大多數時候均為導通狀態 ,如圖 8 所示。這種情況下,DC 損耗較高,要求低導通電阻。根據不同的輸入電壓,AC 損耗可能并不像低側 FET 時那樣重要,但還是沒有低側 FET 那樣低。因此,仍然要求適當的低柵極電荷。這要求在低導通電阻和低柵極電荷之間做出妥協。就低側 FET 而言,導通時間最短,且 AC 損耗較低,因此我們可以按照價格或者體積而非導通電阻和柵極電荷原則,選擇正確的 FET。

高占空比設計的高側和低側 FET 功耗

假設一個負載點 (POL) 穩壓器時我們可以規定某個中間電壓軌的額定輸入電壓,那么最佳解決方案是什么呢,是高輸入電壓/低占空比,還是低輸入電壓/高占空比呢?使用不同輸入電壓對占空比進行調制,同時查看 FET功耗情況。

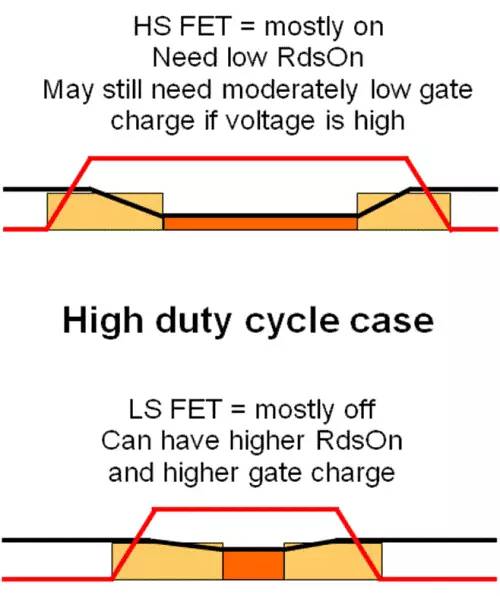

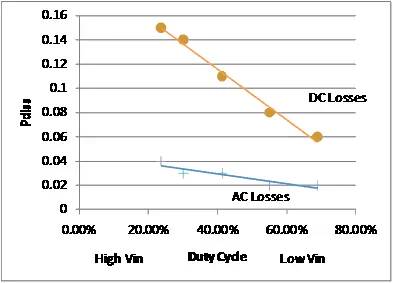

高側 FET 反應曲線圖表明,占空比從 25% 增至 40% 時 AC 損耗明顯降低,而DC 損耗卻線性增加。因此,35% 左右的占空比,應為選擇電容和導通電阻平衡FET的理想值。不斷降低輸入電壓并提高占空比,可以得到最低的AC 損耗和最高的 DC 損耗,就此而言,我們可以使用一個低導通電阻的 FET,并折中選擇高柵極電荷。如低側 FET ,控制器占空比由低升高時 DC 損耗線性降低(低側 FET 導通時間更短),高控制器占空比時損耗最小。整個電路板的AC 損耗都很低,因此任何情況下都應選擇使用低導通電阻的 FET。

高側FET 損耗與占空比的關系

低側 FET 損耗與控制器占空比的關系。

請注意:低側 FET 占空比為 1-控制器占空比,因此低側 FET 導通時間隨控制器占空比增加而縮短

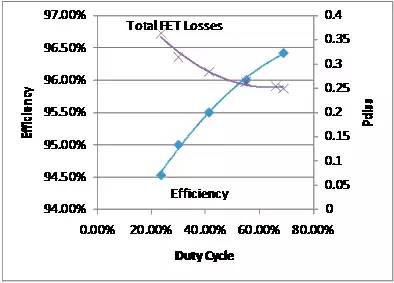

我們將高側和低側損耗組合到一起時總效率的變化情況。我們可以看到,這種情況下,高占空比時組合 FET 損耗最低,并且效率最高。效率從 94.5% 升高至 96.5%。不幸的是,為了獲得低輸入電壓,我們必須降低中間電壓軌電源的電壓,使其占空比增加,原因是它通過一個固定輸入電源供電。因此,這樣可能會抵消在 POL 獲得的部分或者全部增益。另一種方法是不使用中間軌,而是直接從輸入電源到 POL 穩壓器,目的是降低穩壓器數。這時,占空比較低,我們必須小心地選擇 FET。

總損耗與效率和占空比的關系

二、電感的損耗

電感功耗阻性損耗

電感功耗包括線圈損耗和磁芯損耗兩個基本因素,線圈損耗歸結于線圈的直流電阻(DCR),磁芯損耗歸結于電感的磁特性。

DCR 定義為以下電阻公式:

式中,ρ 為線圈材料的電阻系數,l 為線圈長度,A 為線圈橫截面積。

DCR 將隨著線圈長度的增大而增大,隨著線圈橫截面積的增大而減小。可以利用該原則判斷標準電感,確定所要求的不同電感值和尺寸。對一個固定的電感值,電感尺寸較小時,為了保持相同匝數必須減小線圈的橫截面積,因此導致DCR 增大;對于給定的電感尺寸,小電感值通常對應于小的DCR,因為較少的線圈數減少了線圈長度,可以使用線徑較粗的導線。

已知DCR 和平均電感電流(具體取決于SMPS 拓撲),電感的電阻損耗(PL(DCR))可以用下式估算:

PL(DCR) = IL(AVG)^2× DCR

這里,IL(AVG)是流過電感的平均直流電流。對于降壓轉換器,平均電感電流是直流輸出電流。盡管DCR的大小直接影響電感電阻的功耗,該功耗與電感電流的平方成正比,因此,減小DCR 是必要的。

另外,還需要注意的是:利用電感的平均電流計算PL(DCR) (如上述公式)時,得到的結果略低于實際損耗,因為實際電感電流為三角波。本文前面介紹的MOSFET 傳導損耗計算中,利用對電感電流的波形進行積分可以獲得更準確的結果。更準確。當然也更復雜的計算公式如下:

PL(DCR) = (IP^3 - IV^3)/3 × DCR

式中IP 和IV 為電感電流波形的峰值和谷值。

磁芯損耗

磁芯損耗并不像傳導損耗那樣容易估算,很難估測。它由磁滯、渦流損耗組成,直接影響鐵芯的交變磁通。SMPS 中,盡管平均直流電流流過電感,由于通過電感的開關電壓的變化產生的紋波電流導致磁芯周期性的磁通變化。

磁芯材料對磁芯損耗的影響很大。SMPS 電源中普遍使用的電感是鐵粉磁芯,鐵鎳鉬磁粉芯(MPP)的損耗最低,鐵粉芯成本最低,但磁芯損耗較大。

磁芯損耗可以通過計算磁芯磁通密度(B)的最大變化量估算,然后查看電感或鐵芯制造商提供的磁通密度和磁芯損耗(和頻率)圖表。峰值磁通密度可以通過幾種方式計算,公式可以在電感數據資料中的磁芯損耗曲線中找到。

相應地,如果磁芯面積和線圈數已知,可利用下式估計峰值磁通:

這里,B 是峰值磁通密度(高斯),L 是線圈電感(亨),ΔI 是電感紋波電流峰峰值(安培),A 是磁芯橫截面積(cm2),N 是線圈匝數。

磁芯損耗主要由三種構成,磁滯損耗、渦流損耗和剩余損耗。

磁滯損耗如何理解呢?

磁滯損耗源于每個交流周期中磁芯偶極子的重新排列所消耗的功率,可以將其看作磁場極性變化時偶極子相互摩擦產生的“摩擦”損耗,正比于頻率和磁通密度。

磁芯在外磁場的作用下,材料中的一部分與外磁場方向相差不大的磁疇發生了‘彈性’轉動,這就是說當外磁場去掉時,磁疇仍能恢復原來的方向;而另一部分磁疇要克服磁疇壁的摩擦發生剛性轉動,即當外磁場去除時,磁疇仍保持磁化方向。因此磁化時,送到磁場的能量包含兩部分:前者轉為勢能,即去掉外磁化電流時,磁場能量可以返回電路;而后者變為克服摩擦使磁芯發熱消耗掉,這就是磁滯損耗。

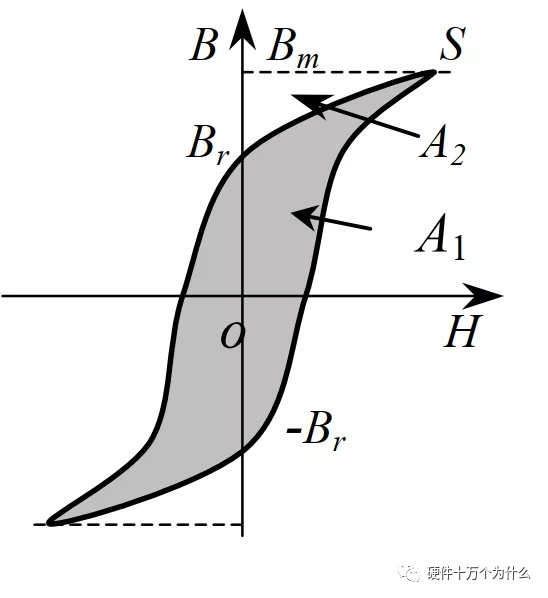

上圖為典型的磁滯曲線,從前面磁滯損耗的理解來看。剩磁Br越小,那么磁疇的剛性轉動越少,損耗就越小。或者說磁滯損耗正比于磁滯回線包圍的面積。

渦流損耗則是磁芯中的時變磁通量引入的。由法拉第定律可知:交變磁通產生交變電壓。因此,這個交變電壓會產生局部電流,在磁芯電阻上產生I2R 損耗。

如下圖,根據電磁感應定律,通電線圈產生磁場B,如果電流是交變的,那么產生的磁場B也是變化的。變化的磁場在磁芯上面產生電場e,并且這個電場是環形電場。因為磁芯材料的電阻率一般不是無限大的,會有一定的電阻值,那么感生出的環形電場會使磁芯中形成環形電流。電流流過電阻,就會發熱,產生損耗,這就是渦流損耗。

剩余損耗

剩余損耗的來源,是因為磁芯在磁化過程中,磁化狀態并不是隨磁化強度的變化立即變化到它的最終狀態,而是需要一個過程,需要一定的時間,這便是引起剩余損耗的原因。

剩余損耗是由于磁化弛豫效應或磁性滯后效應引起的損耗。所謂弛豫是指在磁化或反磁化的過程中,磁化狀態并不是隨磁化強度的變化而立即變化到它的最終狀態,而是需要一個過程,這個‘時間效應’便是引起剩余損耗的原因。它主要是在高頻1MHz以上一些馳豫損耗和旋磁共振等,在開關電源幾百KHz的電力電子場合剩余損耗比例非常低,可以近似忽略。

選擇合適的磁芯,要考慮不同的B-H曲線和頻率特性,因為B-H曲線決定了電感的高頻損耗,飽和曲線及電感量。因為渦流一方面引起電阻損耗,導致磁材料發熱,并引起激磁電流加大,另一方面減少磁芯有效導磁面積。所以盡量選擇電阻率高的磁性材料或采用碾軋成帶料的形式以減少渦流損耗。因此,鉑科新材料NPH-L適用于更高頻率、高功率器件的低損耗金屬粉芯。如圖所示:

磁芯損耗是磁芯材料內交替磁場引致的結果。某一種材料所產生的損耗,是操作頻率與總磁通擺幅(ΔB)的函數,從而降低了有效傳導損耗。磁芯損耗是由磁芯材料的磁滯、渦流和剩余損耗引起的。所以,磁芯損耗是磁滯損耗、渦流損耗和剩磁損耗的總和。公式如下:

在一個世紀以前Steinmetz 總結出一個實用于工程計算磁芯損耗的經驗公式:

這個公式表明單位體積的損耗Pv 是重復磁化頻率和磁通密度的指數函數。Cm ,α 和β 是經驗參數,兩個指數都可以不為整數,一般的1<α<3 和 2<β<3。對于不同的材質,生產廠家一般會給出其相應的一套參數,但公式和參數僅僅適用于正弦的磁化情況,這是該經驗公式應用于開關電源領域的一個主要缺陷。

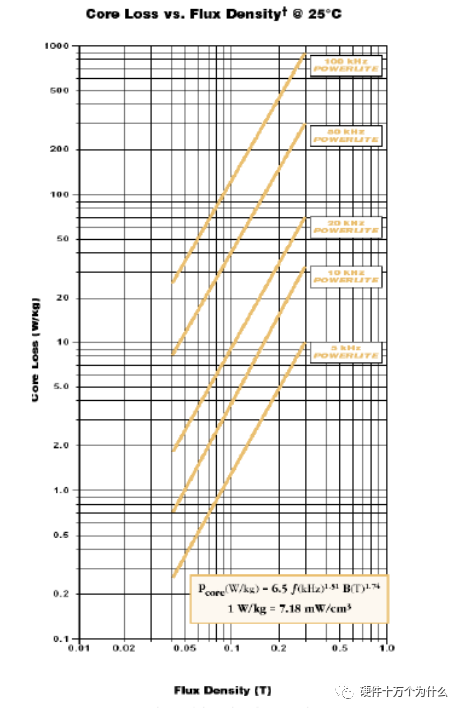

有些廠家給出的計算公式,主要計算磁滯損耗,剩余損耗和渦流損耗都忽略了。如上圖所示:

根據磁芯廠家提供的計算公式計算磁損。

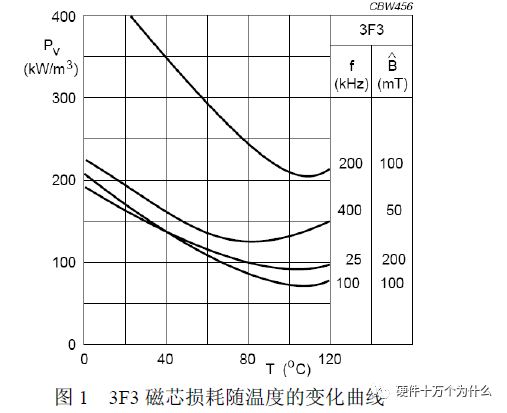

借助 Steinmetz 模型計算磁損在工程上的應用十分廣泛,然而該模型的參數隨頻率變化,也就是說用來反映頻率和最大磁感應強度與磁損關系的冪指數α 和β 的擬合值在不同頻率時是不同的,同時溫度對磁芯損耗的影響也很大。

飛利浦公司的3F3 材料單位體積損耗和溫度的關系。既然磁芯損耗隨溫度的變化而變化,那么計算公式就應該考慮溫度的影響。但式(2)中沒有明顯體現溫度影響的參數。為此,一些產商在Steinmetz 經驗公式的基礎上進行改進,把溫度和頻率的影響包括在一個更加通用的公式中,比如下式就是飛利浦公司提出的計算正弦波下的單位體積的磁芯損耗公式(W/m3)。

其中:

式(3)中參數Cm、α、β 反映了頻率對磁芯損耗的影響。而參數ct0、ct1、ct2,和T 體現了溫度的影響,溫度的總體影響用參數CT 來表示。表1 為飛利浦公司提供的材料的相應參數。應用式(3)和(4) ,Steinmetz 經驗公式(2)可以用來計算正弦波勵磁時,不同頻率和溫度下磁芯材料的單位體積損耗。

表1 飛利浦公司常用磁材料的單位體積損耗(W/m^3)的參數列表

電感磁芯產生損耗的原因: 貼片電感磁芯的損耗主要來源于磁芯損耗和線圈損耗兩個方面,而且這兩個方面的損耗量的大小又需要根據其不同電路模式來進行判斷。其中,磁芯損耗主要是因為磁芯材料內交替磁場而產生的,它所產生的損耗是操作頻率與總磁通擺幅(ΔB)的函數,會大大降低了有效傳導損耗。線圈損耗則是因為磁性能量變化所造成的能源耗損,它會在當功率電感電流下降時,降低磁場的強度。

電感磁芯降低損耗的方法:

1、電感磁芯中產生的磁芯損耗會隨電感磁芯損耗上升而下降的容許銅線損耗,而且還會帶來相同的電感磁芯材料通量激增。因此當開關頻率上升至 500 kHz 以上,電感磁芯損耗和繞組交流損耗就可以極大地減少電感中的容許直流電流。

2、電感磁芯在線圈中的損耗主要表現在銅線損耗上,因此想要降低銅線損耗,必須要在電感磁芯損耗上升時降低,一直持續到各損耗均相等。最好的情況就是在高頻率下損耗穩定保持相等,并允許從磁結構獲得最大輸出電流。

-

二極管

+關注

關注

147文章

9627瀏覽量

166309 -

MOSFET

+關注

關注

147文章

7156瀏覽量

213149 -

buck電路

+關注

關注

27文章

484瀏覽量

46454

發布評論請先 登錄

相關推薦

Buck電路:DCDC電路中的損耗是如何產生的

闡述BUCK電路損耗產生及其估算算法

【原創】同步buck電路講解

分享一下Buck電路的電感要求

buck電路是什么意思_buck電路簡介

開關電源損耗分析 以Buck為例

BUCK型開關電源中的損耗與效率的計算

Buck電路的損耗

Buck電路的損耗

評論