本文探討了如何使用 PSpice for TI 來仿真電機驅動設計中寄生效應的潛在原因,并提供設計技巧來減輕大功率電機驅動系統中常見的負面影響。

大功率系統設計中最令人沮喪的部分之一是寄生效應的結果往往難以捉摸。這尤其適用于大功率電機驅動系統,其中大型電路板設計、大型元件和高輸出電流可能導致輸出振鈴、元件額定值過高或輻射電磁干擾 (EMI)。在本文中,我將使用 適用于 TI 的 PSpice? 模擬電機驅動設計中寄生效應的潛在原因,并提供減輕負面影響的設計技巧。

什么是大功率電機驅動設計?

作為一個完全沉浸在電機驅動系統中的人,我經常理所當然地認為如何根據特定挑戰構建電機驅動系統的基礎知識。寄生分析在大功率系統中變得至關重要有兩個很好的理由。

首先,高功率帶來高電流:在電機中切換 1 A 與在電機中切換 100 A 的效果不同。在高電流下,印刷電路板(PCB)上固有的所有寄生電感和電容都會跳出并開始引起麻煩。保持電流越低,這些寄生元件的重要性就越小。然而,對于具有定義的高輸出功率的系統,目標輸出電流是固定的 - 將設計設置為與任何雜散電感和電容的碰撞過程。

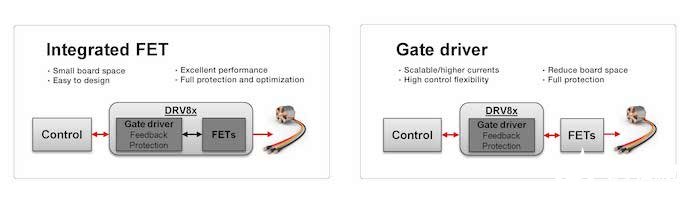

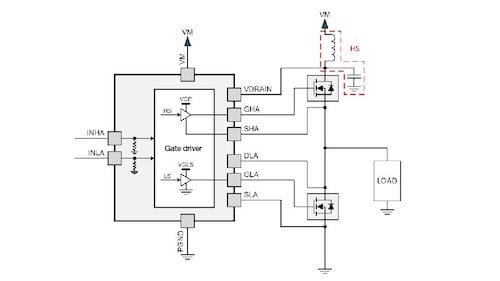

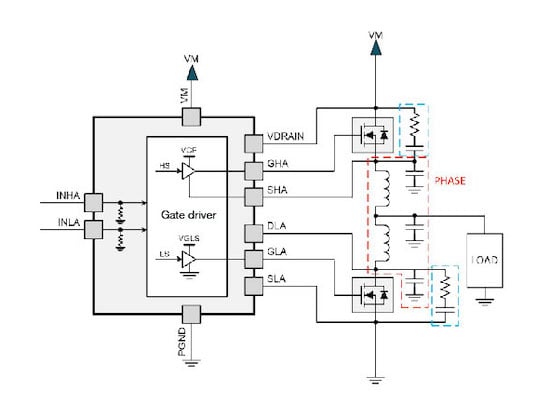

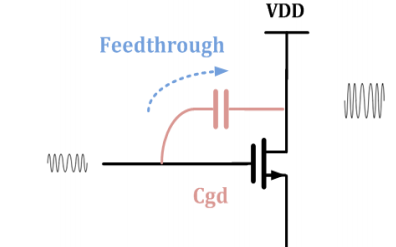

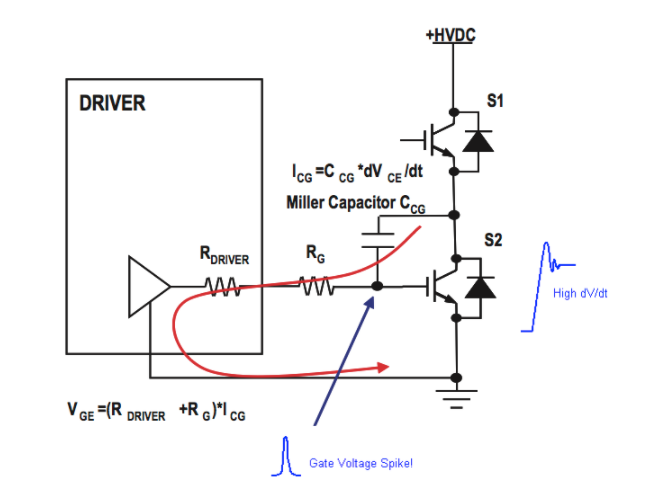

其次,大功率電機驅動系統需要柵極驅動器架構。電機驅動器有兩種類型:集成 FET(場效應晶體管)和帶有外部 FET 的柵極驅動器——見圖 1。集成 FET 電機驅動器對于低功率系統非常有效,因為它們集成了柵極驅動器、功率級和任何其他傳感和保護集成在一個封裝中。這些器件也非常小——例如,DRV8837C僅為 2x2 毫米,因此它們顯著降低了電路板寄生效應。

不幸的是,即使是最高電流的集成 FET 解決方案(例如DRV8873-Q1能夠驅動高達 10 A 的電流),您也無法驅動 100 A 電機,因此需要柵極驅動器架構。當將柵極驅動器與外部分立 MOSFET 一起用于電機驅動器系統時,電路板上的組件之間總會有一些 PCB 走線,這會導致寄生效應。

圖 1.

集成 FET 與柵極驅動器架構

柵極驅動電路和外加脈沖

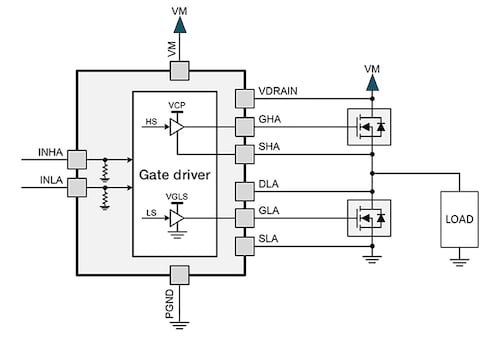

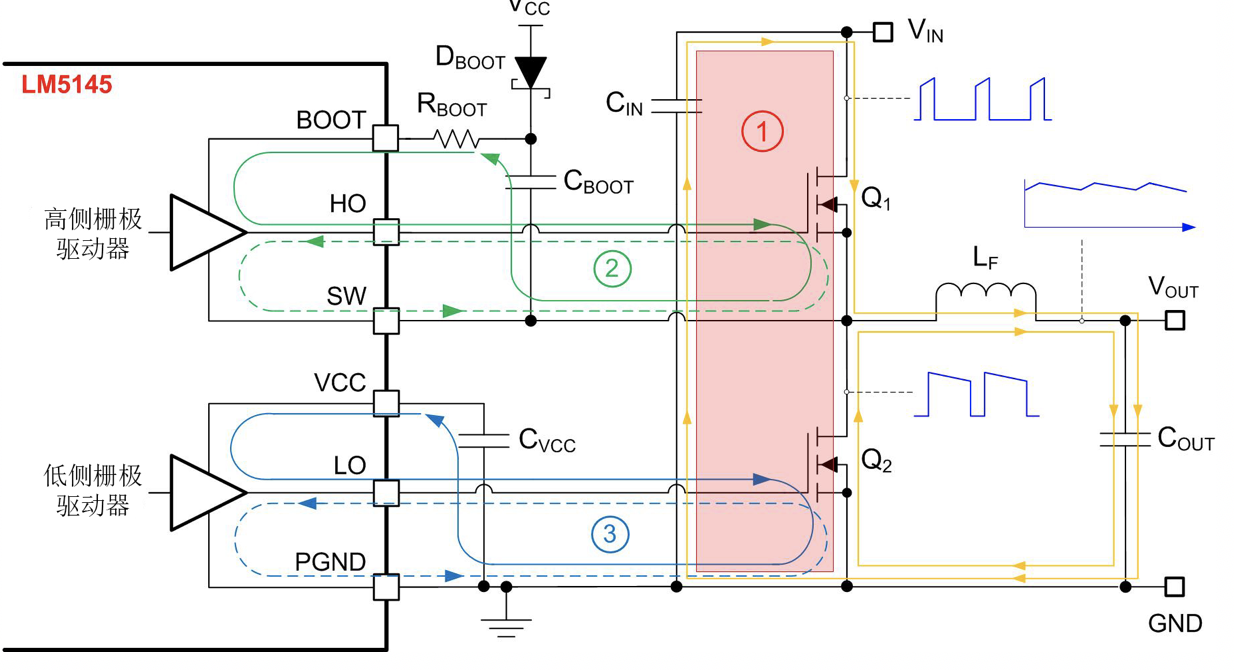

為了構建要分析的電路,讓我們從簡化的半橋電機驅動器開始(圖 2)。我在這個電路中使用的電機驅動器是德州儀器(TI) DRV8343-Q1,帶分流放大器的三相智能柵極電機驅動器。MOSFET 是 TI 的 CSD18540Q5B 我選擇的柵極驅動強度 (IDRIVE) 是 15mA 拉電流和 30 mA 灌電流。為簡單起見,我只使用了一個相位并創建了一個模型負載(240 mΩ和50 μH)。本例中使用的電源為24 V。

圖2.

簡化的驅動電路(無寄生元件)

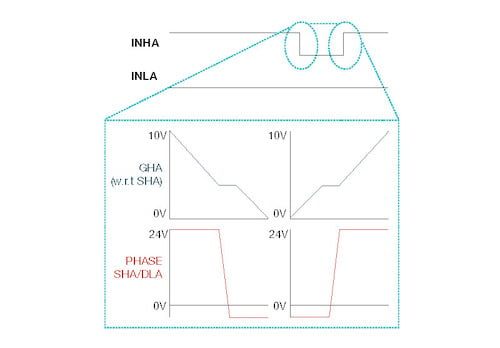

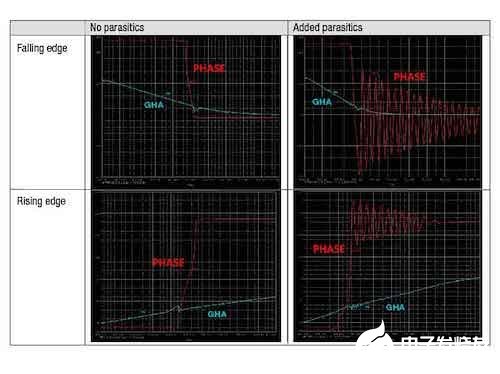

接下來,我模擬了一個“脈沖測試”,其中包括打開高側 MOSFET 一段時間,然后在大量電流流過電路時快速關閉和打開它。模擬脈沖測試將使您能夠觀察在高側 MOSFET 關閉和重新打開時輸出的下降沿和上升沿產生的任何影響。

在圖 3 中,您可以看到應用的控制信號、高側柵極的預期理想波形和輸出電壓。在此仿真中,高側 MOSFET 導通 400 μs,脈沖低電平 30 μs,并在剩余的 70 μs 中變為高電平。低側 MOSFET 保持關閉狀態,因此任何流過低側 MOSFET 體二極管的電流都會傳導。

圖 3.

脈沖測試波形(無寄生元件)

添加寄生元件并進行仿真

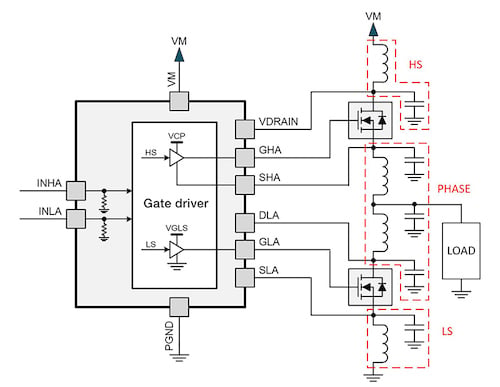

如果在這個電路中加入預期的寄生元件,復雜度會增加得相當快;電路原理圖不再看起來“不錯”。為此,您需要在三個地方添加重要的寄生組件:

在電源和高側 MOSFET (HS) 之間。

在接地和低側 MOSFET (LS) 之間。

在高側和低側 MOSFET (PHASE) 之間。

在這三個位置,您通常會在 PCB 上看到非常大的跡線,對應于高載流網絡。看一下圖 4。

圖 4.

帶有寄生元件的驅動電路

對于寄生值,我使用了以下內容:

高側 (HS):10 nF、5 nH/10 mΩ。

相位 (PHASE):2 nF、2 nH/2 mΩ(每條路徑,在輸出到負載上額外增加 10 nF)。

低側 (LS):10 nF、5 nH/10 mΩ。

由于這只是一個模擬,我使用了(可能)夸大的寄生電感和電容。可以設計一種最小化這些寄生元件的電路板,從而使緩解更容易(盡管遵循相同的過程)。相反,設計不佳的PCB可能具有更多的寄生電感和電容,這使得減輕寄生效應變得更加困難。為了回顧電機驅動器的布局技術,我推薦 電機驅動器電路板布局的最佳實踐應用說明。

當我在添加這些寄生元件之前(圖2)和之后(圖4)仿真電路時,我有一種壓倒性的感覺,我把電路弄壞了。請看圖5,可以看到切換高電平或低電平時相位的顯著振蕩。減輕這些影響以保護電路免受損壞(例如–20 V負電壓尖峰)或防止任何不需要的電磁輻射(振蕩網絡將充當天線)非常重要。

圖5.

添加寄生元件前后用于TI仿真的PSpice結果

為了找出最佳的緩解措施,讓我們逐個分解不同的寄生組件,并模擬每個組件的效果。

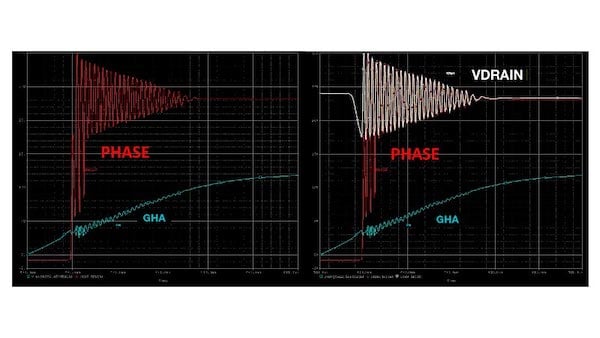

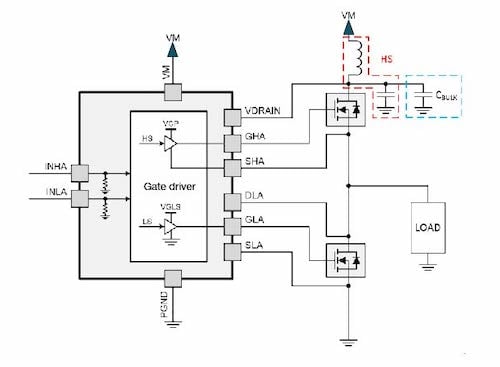

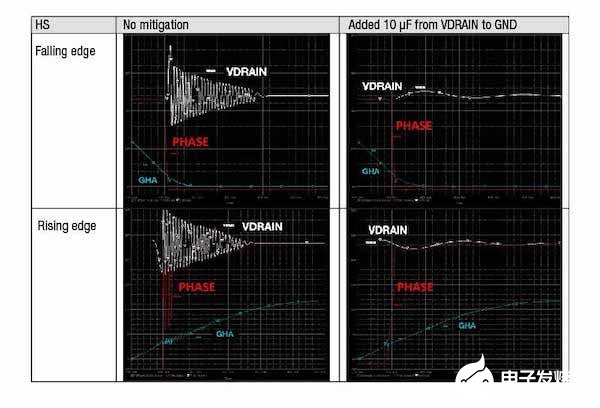

電源和高邊 MOSFET (HS) 之間的寄生元件

當我在電源和高邊MOSFET之間添加寄生元件時(圖6),仿真顯示上升沿輸出端的振蕩非常明顯(圖7)。深入研究更多細節,您可以看到振蕩來自高端MOSFET(VDRAIN)的漏極。在下降沿,當高端MOSFET關斷時,即使輸出不受影響,您也會看到同樣的效果。

圖6.

在高端路徑(HS)中具有寄生效應的驅動器電路

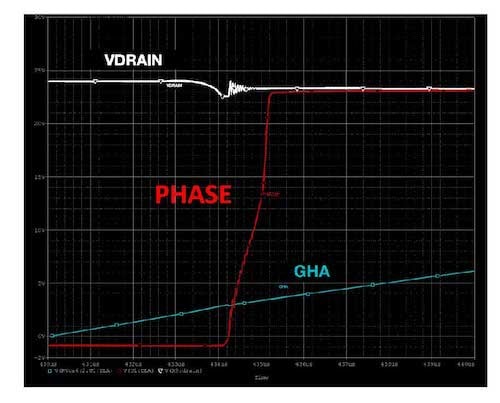

圖7.

在高邊路徑(HS)中添加寄生效應的情況下模擬上升沿

在此階段,您可能會認為需要添加緩沖器,或者壓擺率過高,需要降低。考慮一下:緩沖器在減少相位振蕩方面最有效,而不是VDRAIN振蕩。為了進行研究,我在高端和低端MOSFET上實現了1.2 Ω和33 nF的緩沖器。您可以在圖8中看到效果,其中VDRAIN在開關事件之前仍然會丟失,因此這不是緩解振鈴的最佳方法。

圖8.

盡管有緩沖,但由于 VDRAIN 上的振蕩,緩解效果不佳

要了解有關緩沖器設計的更多信息,請查看技術文章 電源提示:通過七個步驟計算 R-C 緩沖器.

減少振蕩的另一種可能解決方案是降低壓擺率,這在仿真中會顯著減少但不能消除振鈴(圖 9)。由于開關損耗較高,壓擺率降低會導致更多的功率損耗(更熱的組件),應盡可能避免。在本例中,我將柵極驅動電流從15 mA源降低到1.5 mA源,上升時間延長了10倍。

圖9.

盡管柵極驅動電流降低,上升時間較長,但由于功耗較高和持續振蕩,緩解措施無效

為了更好地緩解這些影響,讓我們在VDRAIN節點上添加一個大容量電容(圖10);這將使振蕩明顯變慢,振幅更小。我只是簡單地使電感電容時間常數更長。圖 11 顯示了這種添加的結果。

在仿真中,增加大容量電容使峰值振蕩從37 V(高于電源電壓13 V)降至更易于管理的25 V(高于電源電壓1 V)。該電容器必須盡可能靠近高端 MOSFET,以減輕電容器和 MOSFET 之間的任何額外寄生電感。陶瓷電容器是優選的,因為它們的引線電感較低,高頻響應更好。

圖 10.

在VDRAIN上增加一個大容量電容器

圖 11.

使用大容量電容器(VDRAIN 至 GND)減輕高邊寄生元件的影響

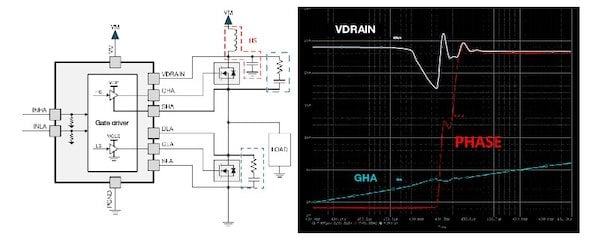

接地和低側 MOSFET (LS) 之間的寄生元件

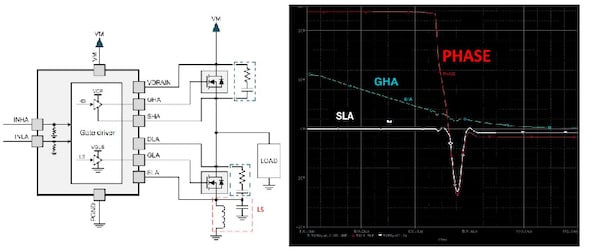

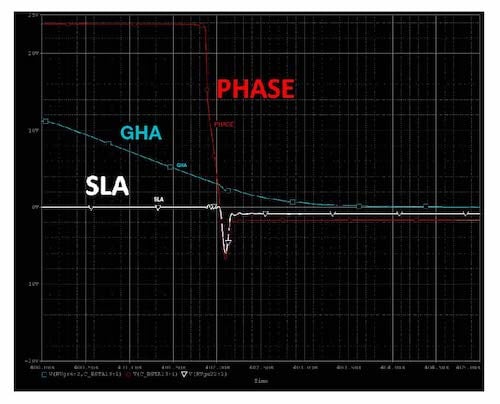

與高側路徑相比,低側路徑幾乎相反。下降沿導致顯著振蕩,而上升沿則顯得干凈。仔細觀察,您可以看到低側 MOSFET 源極節點 (SLA) 在上升沿和下降沿均出現振鈴效應(圖 12)。

圖 12.

在低側路徑(LS)中添加寄生效應的原理圖和仿真

當面對這種情況時,你們中的一些人會想要添加緩沖器或延長上升時間來對抗振鈴,但是,在這種情況下,您也應該避免這種方法。與之前一樣,我在高端和低端MOSFET上實現了1.2 Ω和33 nF的緩沖器。結果是相位振蕩顯著改善,但初始負電壓脈沖仍然存在(圖 13)。

圖 13.

盡管存在緩沖,但由于負電壓尖峰,緩解措施無效

如果降低壓擺率,振鈴會顯著減少(圖14)。在本例中,柵極驅動電流從30 mA灌電流降至7 mA灌電流;下降時間延長>4倍。

圖 14.

盡管柵極驅動電流降低,上升時間較長,但由于功耗較高,緩解措施無效

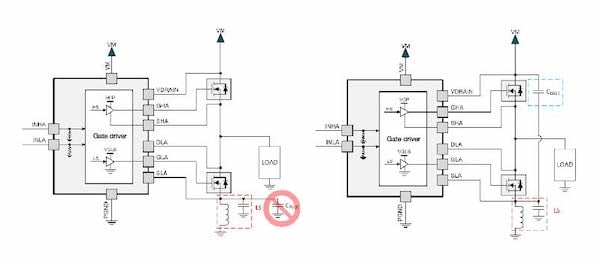

您可以對高邊外殼采用類似的方法,并在電路板上增加額外的大容量電容來抵消這種振鈴。但是,在這種情況下,您不希望在SLA到地增加一個大電容。大多數電機驅動系統使用電流檢測電阻和電流檢測放大器實現低側電流檢測。典型的 2512 封裝檢測電阻將具有 1 至 5nH 的寄生電感,從而為我們假設的寄生值提供了一定程度的可信度。

與檢測電阻并聯的超大電容器會抑制系統正確檢測電流的能力(圖 15)。添加此大容量電容器的正確位置是從VDRAIN到低側源(SLA)。請記住,當添加該去耦電容時,仍然會對通過檢測電阻的峰值電流產生一些影響。該電容的非常大的值將影響通過低側電流檢測得出的任何峰值過流限制。

圖 15.

大容量電容器的放置不正確(左)和正確放置(右),以減輕低側寄生效應

圖 16 說明了這種添加的結果。在仿真中,增加大容量電容可將峰值振蕩從–16 V顯著降低到–3 V。 與前一種情況類似,該電容必須盡可能靠近高端MOSFET漏極和低側MOSFET源極放置,以減輕電容器和MOSFET之間的任何額外寄生電感。陶瓷電容器因其較低的引線電感和更好的高頻響應而更受歡迎。

圖 16.

利用大容量電容器減輕低側寄生元件的影響(VDRAIN 至 SLA)

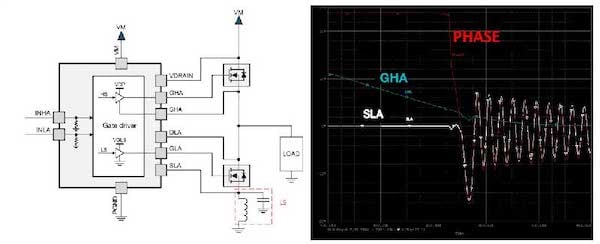

MOSFET 之間的寄生元件(相位)

您可能已經了解到,應始終將高端和低端MOSFET盡可能靠近在一起,以便在開關時將寄生效應降至最低。這是非常好的建議,但你永遠無法完全消除這些負面影響。

即使是最有效的多芯片 MOSFET 解決方案(參見 CSD88599Q5直流 例如)在高端和低端MOSFET之間仍將具有一些寄生電感和電容。MOSFET輸出電容(COSS)和電機電纜電容(電纜長度較長)可能是PCB外相位節點電容的重要貢獻者。

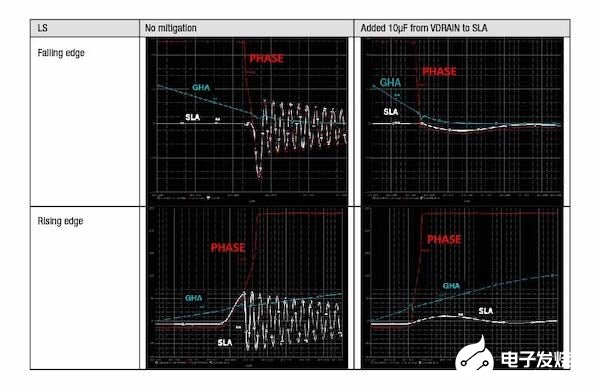

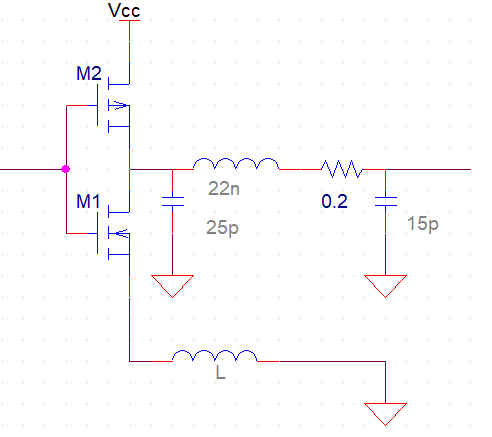

在這種情況下,不可能向電路增加額外的大容量電容來旁路寄生電感。電機的輸出將切換高低電平,并且該網絡上的其他大型電容器將反復充電和放電 - 這是一種非常低效的系統解決方案。發生這種情況時,最好先使用緩沖器作為第一個策略(圖 17)。

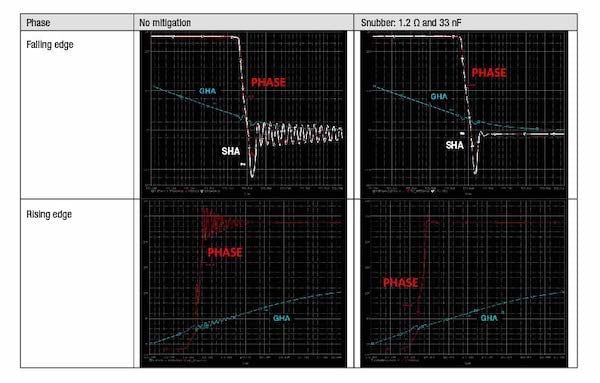

如果你是一個冷落的支持者,你可以松一口氣——讓我們現在就使用它們吧!您可以在圖18中看到在電路中添加緩沖器的效果。

圖 17.

在相路徑(PHASE)和附加緩沖器中添加寄生效應的原理圖

圖 18.

使用緩沖器減輕相位寄生元件

緩沖器幾乎完全解決了上升沿的振蕩問題,并顯著改善了下降沿的情況。與之前的實驗一樣,我在高端和低端MOSFET上實現了1.2 Ω和33 nF的緩沖器。然而,與低側MOSFET寄生情況(圖14)非常相似,第一個負脈沖仍然存在。

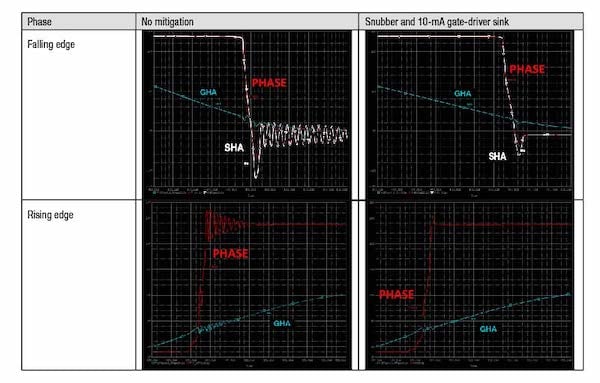

在這個階段,您可以得出結論,為了完全克服這些寄生效應,需要增加下降時間。您必須改善圖18下降沿上的–11 V負電壓尖峰,以便保持在 DRV8343-Q1 (–7 V,200 ns)。將柵極驅動吸電流從 30 mA 降至 10 mA 時,將在最大額定值內得到該負尖峰(圖 19)。

圖 19.

通過緩沖器和降低柵極驅動電流吸收器減輕相位寄生元件

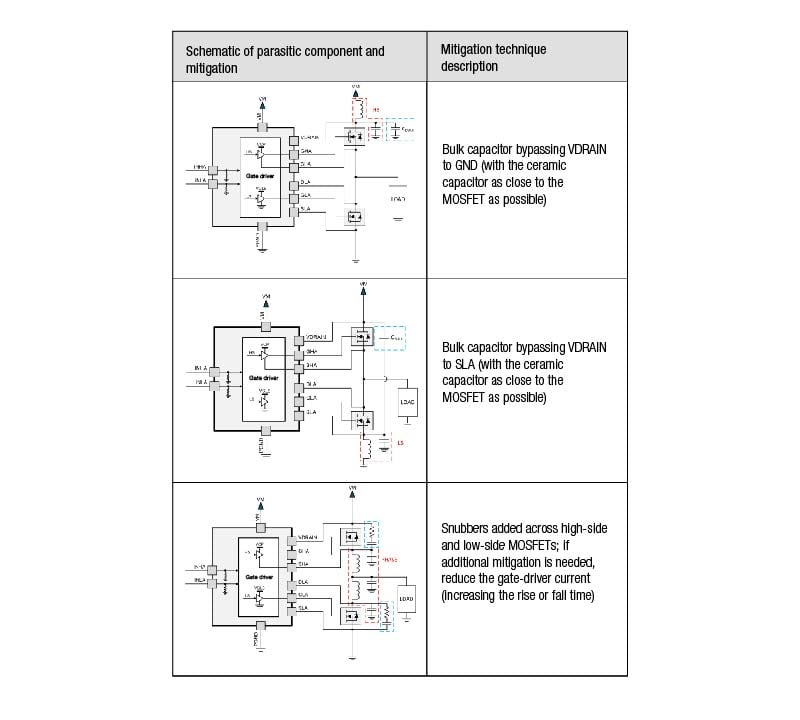

將一切整合在一起

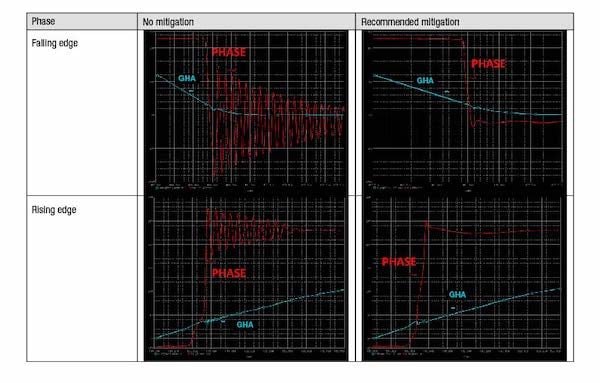

那么,通過這次模擬練習,我們學到了什么呢?對于這三種常見的寄生效應(高壓側、低側和相位),有三種不同的緩解技術。如果將本文所述的所有緩解技術應用于包含所有寄生元件的電路(表1),則可以顯著減少過沖、下沖和振鈴(圖20)。

表 1.寄生元件抑制技術摘要

圖 20.

使用概述的方法減輕所有寄生組件

這對我來說是一個特別有趣的練習,因為它給了我一個很好的機會來嘗試 適用于 TI 仿真工具的 PSpice.這些仿真比物理電路板實驗更容易、更快捷,并且可以很好地了解當您遇到電路板寄生效應的實際問題時該怎么做。

-

驅動

+關注

關注

12文章

1839瀏覽量

85263 -

電機

+關注

關注

142文章

9002瀏覽量

145347 -

仿真

+關注

關注

50文章

4073瀏覽量

133555

發布評論請先 登錄

相關推薦

PCB布局的DC電阻,寄生電容和寄生電感

求助: 樹莓派驅動MOS(場效應)管電機驅動板時高電平無法設置的問題

寄生電路的效應:Latch-Up(鎖定)

【高速PCB布線指南(2)】寄生效應

EMI 簡介:標準、原因和緩解技術

平衡MOSFET差分對中的模擬布局寄生效應

Spectre和Meltdown的利用漏洞的軟件影響和緩解措施

減小高速PCB中過孔的寄生效應帶來的不利影響的方法

寄生效應和Via及Ground Bounce的詳細介紹和綜合應用資料概述

EMI了解功率級寄生效應

通過仿真了解和緩解電機驅動板寄生效應

通過仿真了解和緩解電機驅動板寄生效應

評論