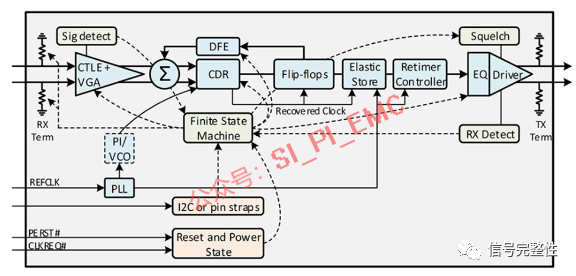

下面是Retimer的結(jié)構(gòu)框圖,其中包含了均衡、CDR等模塊。

從框圖中可以看到Retimer就類似于一顆PHY芯片,信號(hào)在經(jīng)過Retimer的之后,通過內(nèi)部均衡之后再通過CDR重構(gòu)信號(hào),使信號(hào)傳輸能力增加,再進(jìn)行下一階段的傳遞。所以信號(hào)經(jīng)過了Retimer之后,降低了信號(hào)的抖動(dòng)、恢復(fù)了驅(qū)動(dòng)力能力,這樣就傳遞的更遠(yuǎn)。以達(dá)到更好的信號(hào)完整性。但是,復(fù)雜的ReTimer會(huì)增加更多的潛伏時(shí)間。對(duì)于一些低傳輸延時(shí)的系統(tǒng),要慎重使用。

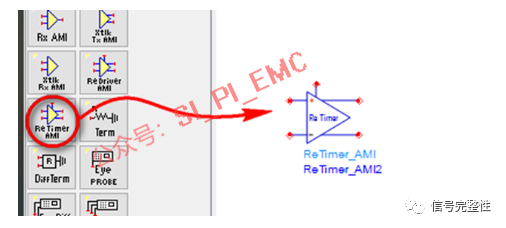

下面我們來看看如何在ADS中添加Retimer進(jìn)行仿真分析。在ADS中有一個(gè)專門的Retimer模型元件ReTimer_AMI,如下圖所示:

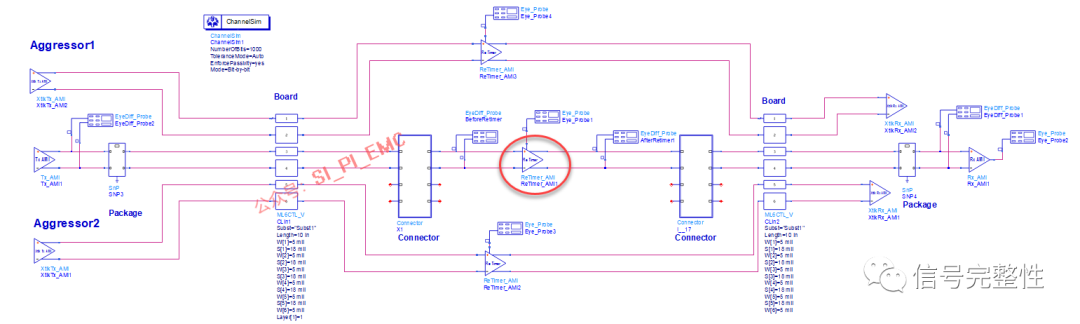

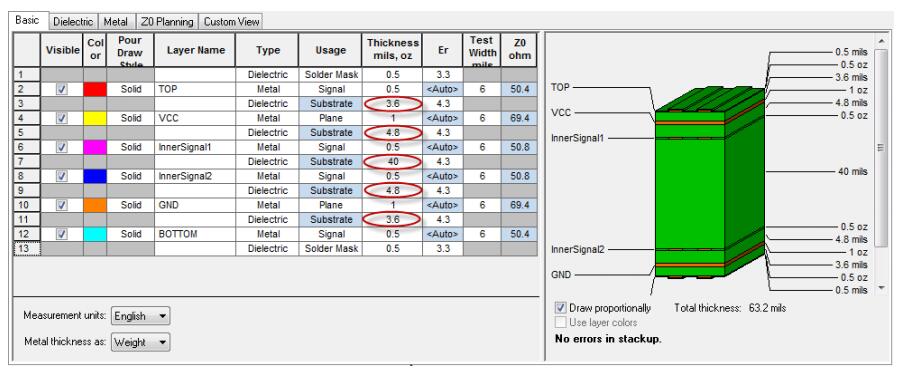

本文以PCIe3.0的仿真為例,由于在PCIe3.0的通道中損耗比較大,且有串?dāng)_的影響,所以導(dǎo)致信號(hào)不能滿足信號(hào)完整性的要求,所以在鏈路中間添加了Retimer。建立帶有Retimer元件的仿真原理圖如下圖所示(紅色圈中為Retimer模型),在Retimer前后分別放置了兩個(gè)Eye_Probe。

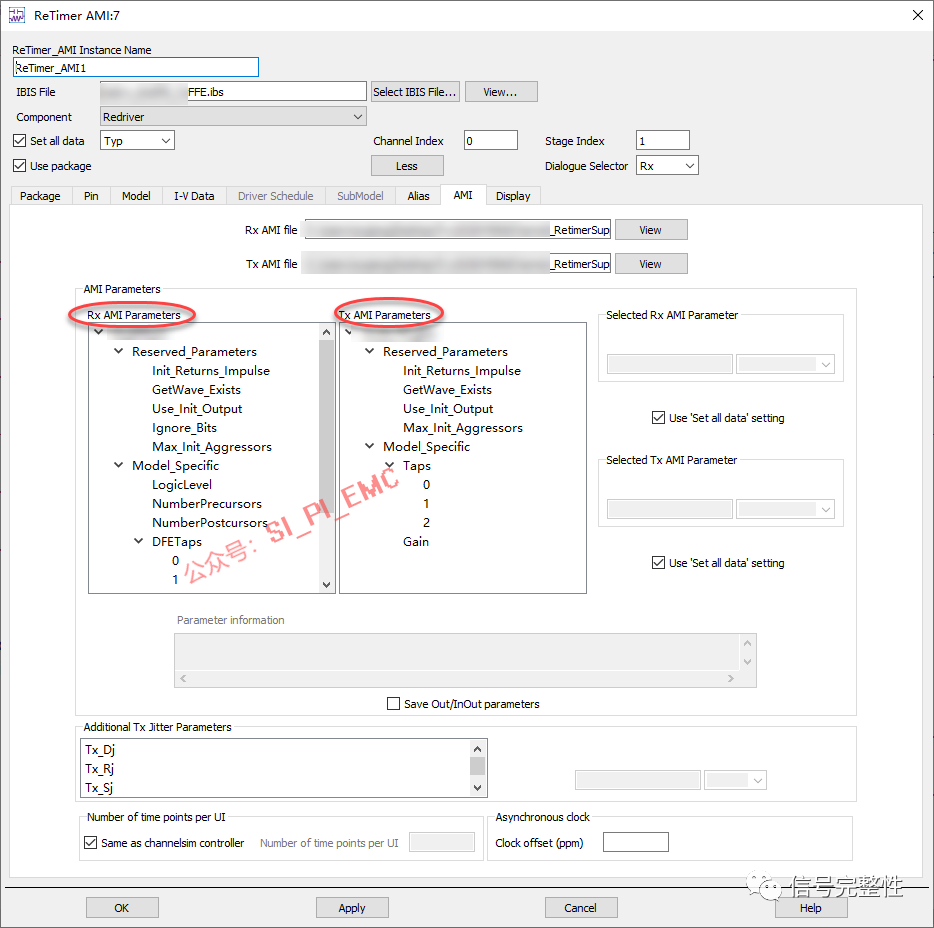

雙擊ReTimer_AMI導(dǎo)入Retimer的IBIS-AMI模型。在設(shè)置Retimer模型時(shí),需要配置好AMI模型,如下圖所示:

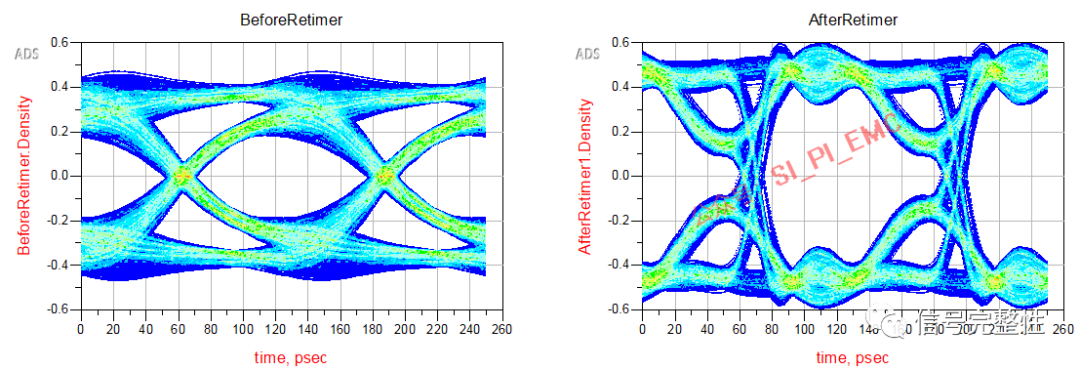

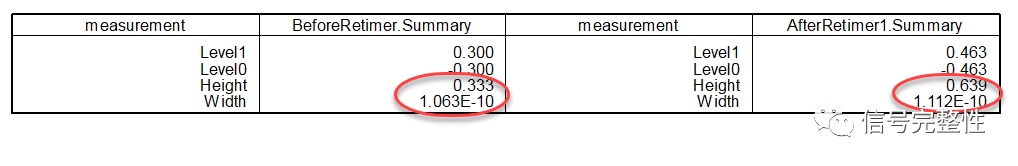

仿真后,分別觀察Retimer前后的眼圖,眼圖如下圖所示:

分別讀取眼圖的眼高和眼寬,如下圖所示:

從結(jié)果上可以看到,在Retimer前后的眼圖差異非常大,眼高和眼寬都改善了很多。

審核編輯:劉清

-

信號(hào)完整性

+關(guān)注

關(guān)注

68文章

1418瀏覽量

95880 -

PHY

+關(guān)注

關(guān)注

2文章

309瀏覽量

52055 -

cdr

+關(guān)注

關(guān)注

1文章

51瀏覽量

18200 -

Retimer

+關(guān)注

關(guān)注

2文章

10瀏覽量

7565

原文標(biāo)題:如何在ADS中使用Retimer

文章出處:【微信號(hào):SI_PI_EMC,微信公眾號(hào):信號(hào)完整性】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

高速電路信號(hào)完整性分析與設(shè)計(jì)—信號(hào)完整性仿真

信號(hào)完整性仿真應(yīng)用

信號(hào)完整性與電源完整性的仿真分析與設(shè)計(jì)

Altium Designer中進(jìn)行信號(hào)完整性分析

高速電路信號(hào)完整性分析與設(shè)計(jì)—信號(hào)完整性仿真

信號(hào)完整性的仿真分析

信號(hào)完整性與電源完整性仿真分析

信號(hào)完整性分析

信號(hào)完整性與電源完整性的仿真分析與設(shè)計(jì)

如何在考慮信號(hào)完整性的情況下進(jìn)行高速的PCB設(shè)計(jì)

信號(hào)完整性與電源完整性的仿真

如何在通道中添加Retimer進(jìn)行信號(hào)完整性仿真分析?

如何在通道中添加Retimer進(jìn)行信號(hào)完整性仿真分析?

評(píng)論