1, 介紹

本文主要介紹總線相關的知識,會從以下幾個方面展開:什么是總線,為什么需要總線,總線的組成,總線的分類,ARM中常見的總線協(xié)議是什么,然后后面的部分會著重介紹一下ARM中常見的總線協(xié)議及工作原理。

什么是總線呢?總線是計算機各種功能部件(運算器、控制器、內(nèi)存、輸入、輸出等)之間傳送信息的公共通信干線,它是由導線組成的傳輸線束。簡單來說總線也是導線,是連接兩個以上計算機部件的專用信號線,在各個部件之間傳送信息的公共通路。

為什么需要總線呢?總的來說現(xiàn)代計算機及嵌入式系統(tǒng)基本結(jié)構(gòu),包括3個部件:CPU(運算器+控制器)、存儲器、IO設備(輸入設備+輸出設備),但在實際應用中計算機及嵌入式系統(tǒng)的結(jié)構(gòu)遠比基本結(jié)構(gòu)要復雜,一個計算機或嵌入式系統(tǒng)中往往會有多個CPU、存儲器或者IO設備,這些部件只有連接在一起才能形成完整的計算機系統(tǒng)。這些部件可以由多種不同的拓撲結(jié)構(gòu)進行連接,比如星型、樹型、環(huán)形、總線型、交叉開關。這幾種拓撲結(jié)構(gòu)相較而言,總線型結(jié)構(gòu)更有優(yōu)勢,它主要具有如下優(yōu)點:

1)結(jié)構(gòu)簡單靈活,便于擴充或減少部件;

2)可靠性高,響應速度快;

3)共享資源能力強,非常便于廣播式工作,即一個結(jié)點發(fā)送所有結(jié)點都可接收。

因此,計算機及嵌入式系統(tǒng)主要采用總線型結(jié)構(gòu)連接各部件。

總線由哪些部分組成的呢?總線是從源部件傳送信息到一個或多個目的部件的一組傳輸線,而導線則是僅僅連接一個源部件到一個或多個目的部件的傳輸線。總線除了要有傳輸導線外,重要的是總線控制線路。由于總線有輸出信息的源部件,多個接收信息的目的部件,對于發(fā)送的信息就必須經(jīng)過選擇判優(yōu),分開發(fā)送,避免多個部件同時發(fā)送信息的矛盾。同時還應對傳送的信息進行定時,防止信息丟失。這樣,總線中應該設置總線控制線路。總線控制線路,包括總線判優(yōu)或仲裁控制邏輯、驅(qū)動器和中斷邏輯等。

都有哪些類型總線呢?其實按照不同的分類標準,總線有多種類型。按照功能分類:數(shù)據(jù)總線、地址總線、控制總線,分別用來傳輸數(shù)據(jù)、數(shù)據(jù)地址和控制信號。按照總線的傳輸格式劃分:串行總線和并行總線,分別串行、并行地傳輸數(shù)據(jù)。按照時序控制方式劃分:同步總線和異步總線,同步總線所連接的各部件使用同一個時鐘,在規(guī)定的時鐘節(jié)拍進行規(guī)定的總線操作,來完成部件之間的信息交換,異步總線所連接的各部件沒有統(tǒng)一的時鐘,部件之間通過信號握手的方式進行,總線操作時序不固定。我們著重關注按照總線功能劃分:片內(nèi)總線、系統(tǒng)總線、通信總線。

- 片內(nèi)總線:CPU內(nèi)部的總線。它是CPU內(nèi)部控制器、運算邏輯單元、寄存器等模塊之間的公共連接線。

- 系統(tǒng)總線:CPU、GPU、ISP、CODEC、主存、I/O等各大部件之間的信息傳輸線,它把這些部件連接起來構(gòu)成了計算機或嵌入式系統(tǒng)。由于這些部件通常都在硬件板子上,因此又叫做板級總線和板間總線。按系統(tǒng)總線傳輸信息的不同,它又可分為三類:數(shù)據(jù)總線、地址總線和控制總線。

- 數(shù)據(jù)總線(Data Bus):用來傳輸各功能部件之間的數(shù)據(jù)信息,它是雙向傳輸總線,其位數(shù)與機器字長、存儲字長有關。在任意兩個涉及數(shù)據(jù)(包括要運算的數(shù)據(jù)信息,要處理的指令信息)的存儲、處理乃至交換、傳輸?shù)脑O備之間,都應有數(shù)據(jù)總線。它的兩個性能指標是傳輸?shù)乃俾屎涂偩€的寬度。前者是指每個單位時間它傳送多少個數(shù)據(jù),顯然這個指標將對計算機或嵌入式的運算速度有重大影響,而它與傳輸?shù)木嚯x也有關系。后者是每條總線可以同時傳送多少位,也就是這個總線一共有多少條實際的物理線路,我們把它稱為總線的寬度。

- 地址總線(Address Bus):用來指出數(shù)據(jù)總線上的源數(shù)據(jù)或目的數(shù)據(jù)所在的主存單元或I/O端口的地址,它是單向傳輸總線,地址總線的位數(shù)與主存地址空間的大小有關。地址總線用于傳送地址信號,以確定所訪問的存儲單元或某個輸入/輸出端口。計算機或嵌入式中地址總線一般有16位、20位、24位、32位、36位等幾種寬度標準,與存儲器所用的地址的位數(shù)以及端口的地址位數(shù)相對應。地址總線要和數(shù)據(jù)總線一起使用才有效。比如,如果要從某個設備向存儲設備存入數(shù)據(jù),則這個數(shù)據(jù)應該放到從某個設備連接到存儲設備的數(shù)據(jù)總線上,同時應在連接這兩個設備的地址總線上給出存儲設備的地址,這樣才能實現(xiàn)正確的存入(寫入)操作。只有掌握總線控制權(quán)的主控部件,如CPU、DSP等,才能向地址總線上發(fā)送地址信息。而像存儲器這樣不掌握總線控制權(quán)的部件,只能從地址總線上接收地址信息,并配合控制信號進行地址譯碼就可以了。

- 控制總線(Control Bus):傳輸?shù)氖强刂菩畔ⅲ–PU送出的控制命令和主存(或外設)返回CPU的狀態(tài)反饋信號。其實要實現(xiàn)對存儲器的讀、寫操作,需要在控制信號上的信號控制之下,同時有數(shù)據(jù)總線、地址總線的參與,讀、寫操作才能實現(xiàn)。以實現(xiàn)把數(shù)據(jù)總線上的數(shù)據(jù)存入地址總線給出相應地址的存儲器的某個存儲單元為例,控制總線在其工作的周期中首先使地址總線工作,從而使相應單元發(fā)送地址信息到存儲器做好接收數(shù)據(jù)的準備,然后使數(shù)據(jù)總線工作,把它上面的數(shù)據(jù)寫到該存儲單元中。地址總線與數(shù)據(jù)總線上的信息一直維持到控制總線工作周期的結(jié)束。

- 通信總線:用于計算機或嵌入式系統(tǒng)之間或計算機或嵌入式系統(tǒng)與其他系統(tǒng)(如遠程通信設備、測試設備)之間信息傳送的總線,通信總線也稱為外部總線。常見的通信總線,比如USB、PCIE、SPI、IIC、UART等總線。

ARM為高性能嵌入式系統(tǒng)定義了AMBA(Advanced Micro-Controller Bus Architecture,高級微控制器總線架構(gòu))的On-Chip Bus片上總線規(guī)范,這個協(xié)議定義的主要是一系列系統(tǒng)總線。比如,AHB(Advanced High-Performance Bus,高級高性能總線)、APB(Advanced Peripheral Bus,高級外設總線)、AXI(Advanced Extensible Interface,高級可擴展接口總線)、ACE(AXI Coherency Extensions,AXI一致擴展總線)、ASB(Advanced System Bus,高級系統(tǒng)總線)等。接下來重點介紹一下AHB、APB、AXI總線。

AHB(用于高性能,高數(shù)據(jù)吞吐部件,如CPU、DMA、DSP之間的連接)、APB(為系統(tǒng)的低速外部設備提供低功耗的簡易互連)、AXI(主要面向高性能地址映射通信的需求)

2,AMBA總線

2.1 AMBA的演進

AMBA是ARM在1996年推出的互聯(lián)協(xié)議,主要用在片上系統(tǒng)中各IP(比如:CPU、GPU、內(nèi)存、DSP等)之間的通信,整個通信基于主從協(xié)議。AMBA促進了IP的模塊化設計、可重用性、兼容性和可擴展性。

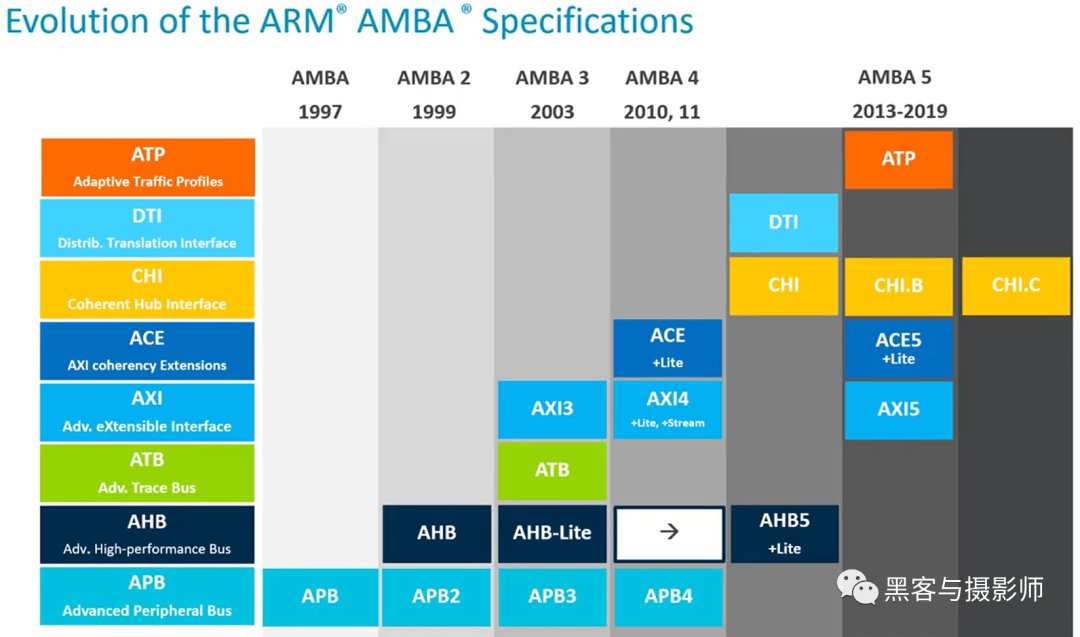

AMBA高級微控制器總線架構(gòu)的演進過程如下:

AMBA自1996年以來經(jīng)過不斷發(fā)展,目前已經(jīng)發(fā)展到第五代了。APB(高級外設總線)和ASB(高級系統(tǒng)總線)是最早的AMBA總線協(xié)議。隨后在1999年推出了AMBA2,在此版本中,AMBA增加了AHB(高性能總線)。到2003年,AMBA3引入了AXI(高級可擴展接口),將互連的性能做了比較大的提升。它還帶來了ATB(高級跟蹤總線),用于CoreSight跟蹤的解決方案和片上調(diào)試。ASB總線協(xié)議由于設計復雜而不再使用。這種設計持續(xù)了多年,直到2010年AMBA4引入了ACE(AXI一致性擴展總線)。引入QoS和long burst的支持,根據(jù)不同應用可選擇AXI4、AXI4-lite、AXI4-stream。這個版本在很大程度上提升了AXI,并為新版本奠定了基礎。到2013年,AMBA5出現(xiàn)了,并提供了CHI(相干集線器接口)以及新設計的高速傳輸應用程序,有助于減少擁堵。AMBA的影響如此之大,以至于今天這些協(xié)議被作為所有嵌入式處理器的行業(yè)標準。

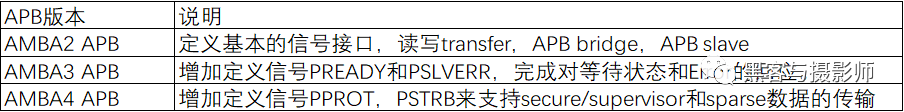

APB:是低帶寬總線協(xié)議,為了支持外圍設備,在低功耗和低復雜性方面進行了特定的優(yōu)化。讀寫操作共享同一組信號,不支持burst數(shù)據(jù)傳輸。它用作外圍設備的低成本接口,不需要大量數(shù)據(jù),低延時的傳輸,因此不需要高性能的流水線總線接口。APB總線的任何傳輸至少需要2個周期。典型的含有APB總線的系統(tǒng),在 AHB、AXI與連接外圍設備接口的APB總線之間含有APB橋接器,通過它可以訪問外圍設備的可編程寄存器。

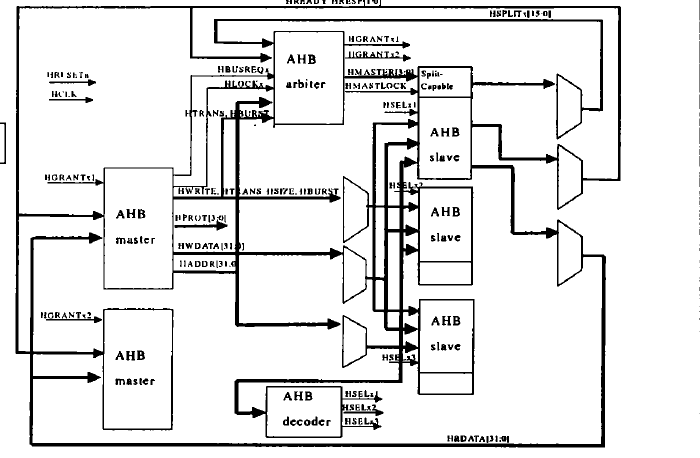

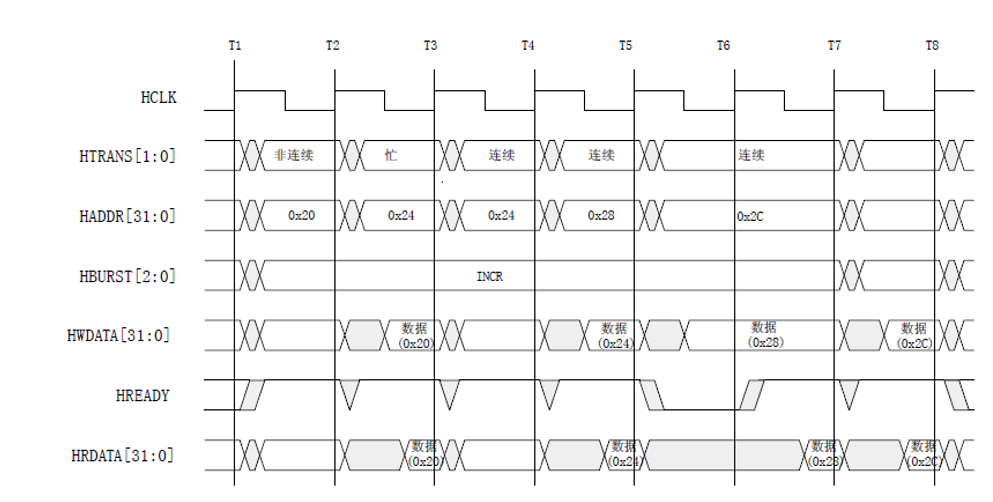

AHB:主要是針對高性能、高時鐘頻率及快速系統(tǒng)模塊所設計的總線,它充當高性能系統(tǒng)主干總線,可以連接如微處理器、芯片上或芯片外的內(nèi)存模塊和DMA等高效率模塊。它支持多個總線主控并支持高帶寬操作。典型的AMBA系統(tǒng)設計包含 AHB主機、AHB從機、AHB仲裁器和AHB解碼器。它用于在共享總線上連接需要高帶寬的組件,如DMA、DSP和內(nèi)存。AMBA AHB支持了如下特性:

- 突發(fā)傳輸

- 拆分交易

- 更寬的數(shù)據(jù)總線配置(64/128 位)

- 單時鐘邊沿操作

- 單周期總線主切換

AHB-lite:是AHB的一個簡化版本。簡化后只支持一個Master,這消除了對任何仲裁、重試、分割事務等的需求,通過簡化設計,提高了傳輸性能。

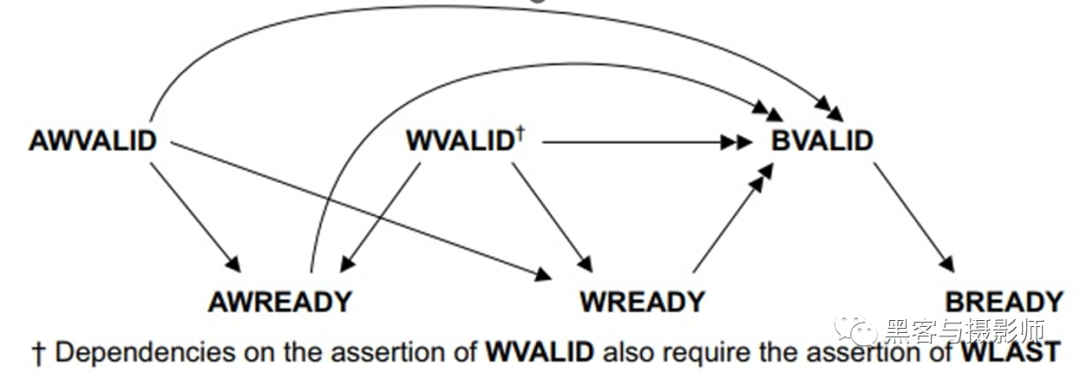

AXI:是一種并行、高性能、高頻率、同步的總線協(xié)議。適合于高帶寬和低延遲互連。這是一個點對點的互連協(xié)議,支持亂序傳輸、讀寫通道分離,它克服了AHB、APB等共享總線協(xié)議在可連接的代理數(shù)量方面的限制。該協(xié)議支持多個outstanding 的數(shù)據(jù)傳輸(多組未完成事務共存)、burst數(shù)據(jù)傳輸、單獨的讀寫通道和支持不同的總線寬度。它針對高性能和高頻系統(tǒng),具有以下主要特點: - 多筆未完成交易

- 亂序數(shù)據(jù)補全

- 僅發(fā)布起始地址的基于突發(fā)的事務

- 支持使用選通的非對齊數(shù)據(jù)傳輸

- 同時讀取和寫入事務

- 用于高速操作的流水線互連

AXI-lite:簡單低吞吐量的內(nèi)存映射通信,是AXI總線協(xié)議的簡化版本,簡化后不支持突發(fā)數(shù)據(jù)傳輸,用于操作控制和狀態(tài)寄存器。

AXI-stream:是AXI總線協(xié)議的另一種風格,它只支持數(shù)據(jù)流從master流到slave單向流動,用于高速流數(shù)據(jù)傳輸。與完整的AXI或AXI-lite不同,AXI-stream協(xié)議數(shù)據(jù)流只在一個方向流動,沒有單獨的讀、寫通道。

ACE:AXI4協(xié)議的擴展,應用于在一個芯片上集成多個CPU核心與一致性cache的場景。ACE協(xié)議擴展了AXI讀寫數(shù)據(jù)通道,同時引入了單獨的snoop 地址、snoop 數(shù)據(jù)和snoop 響應通道。這些額外的通道提供了實現(xiàn)基于snoop的一致性協(xié)議的機制。ACE一致性協(xié)議確保所有master都能看到任何地址位置的正確數(shù)據(jù)。這避免了對緩存之間主要一致性的軟件緩存維護。ACE 還提供屏障事務來保證系統(tǒng)內(nèi)多個事務的排序,以及分布式虛擬內(nèi)存 (DVM) 功能來管理虛擬內(nèi)存。

ACE-Lite:對于沒有自己cache的agents,但仍屬于可共享一致性域的一部分,如DMA或網(wǎng)絡接口agent,使用ACE-lite協(xié)議實現(xiàn)這種“單向”一致性。

CHI:ACE協(xié)議作為AXI的擴展而開發(fā),以支持一致性互連。ACE協(xié)議使用了master/slave之間的信號電平通信,因此互連需要大量的線和增加的通道來進行snoops和響應。隨著SOC上集成越來越多的一致性clusters,AMBA5修訂版引入了CHI協(xié)議。定義了連接完全一致的處理器的接口。它是一種基于數(shù)據(jù)包的分層通信協(xié)議,具有協(xié)議、鏈路和網(wǎng)絡層。它與拓撲無關,并提供基于服務質(zhì)量 (QoS) 的機制來控制系統(tǒng)中的資源。它支持處理器之間的高頻和非阻塞相干數(shù)據(jù)傳輸,為數(shù)據(jù)中心等應用提供性能和規(guī)模。

以上的AMBA演進及各總線協(xié)議的介紹,是我們深入地了解這些協(xié)議的開始,要想進一步深入了解這些總線的最好方法是閱讀相應的協(xié)議規(guī)范,通過這些協(xié)議規(guī)范,我們可以了解每個協(xié)議的細節(jié)。其中APB和AHB總線協(xié)議相對簡單,比較容易學習。而AXI和ACE、CHI總線相對復雜,需要詳細閱讀,以及了解緩存一致性和一般通信協(xié)議的基本知識,加上實踐才能掌握這些總線協(xié)議。本文后面會詳細介紹APB、AHB及AXI,由于是現(xiàn)學現(xiàn)賣,難免會有理解不到位的地方,僅供大家參考。

2.2 AMBA總線框架

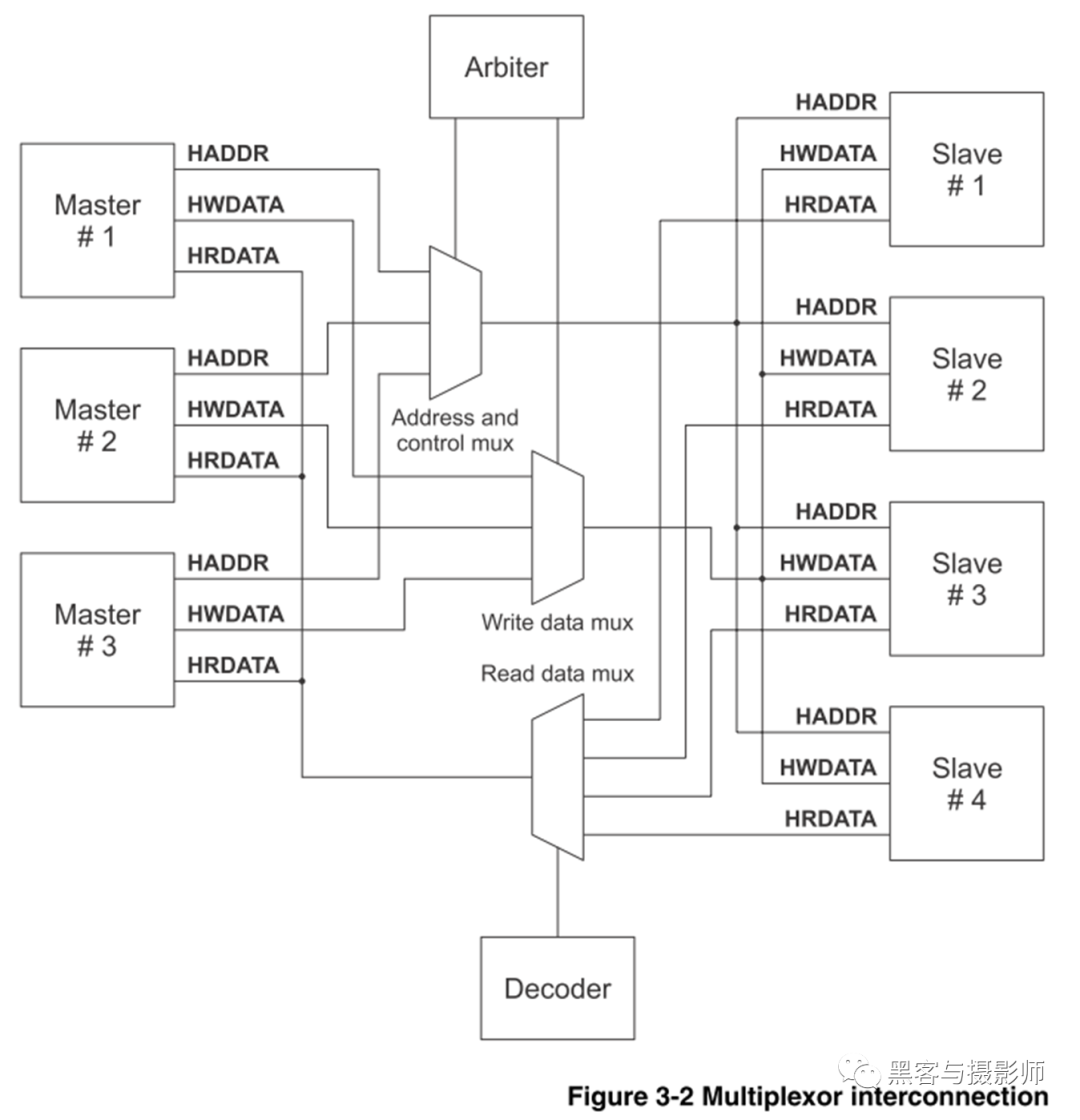

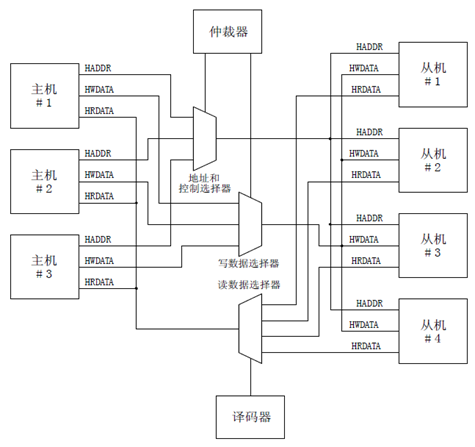

系統(tǒng)總線連接的設備,根據(jù)功能不同分為主模塊和從模塊。大部分掛在總線上的模塊只是單一屬性的功能模塊:比如要么是主模塊,要么是從模塊。主模塊是向從模塊發(fā)出讀寫操作的模塊,如CPU、DSP等。從模塊是接受主模塊發(fā)來的命令并做出反應的模塊,如片上的RAM,AHB/APB橋接器等。另外,還有一些模塊同時具有兩種屬性,比如DMA(直接存儲器存取),在被CPU編程時是從模塊,但在后續(xù)傳輸數(shù)據(jù)時是主模塊。

系統(tǒng)芯片上,通常設計多個主模塊和多個從模塊。不同的從模塊在總線上對應著互不重疊的地址區(qū)間,總線通過主模塊發(fā)起傳輸任務的目標地址。AXI總線使用不同的ID號來區(qū)分主模塊,主模塊可以在其他主模塊訪問未完成的情況下繼續(xù)發(fā)起請求。同一條AHB總線上的設備共享固定的地址數(shù)據(jù)傳輸通道,這意味著其中一個主模塊占用AHB總線后,其余主模塊均處于等待狀態(tài)。如果總線上存在多個主模塊,這就需要仲裁器來決定如何控制各種主模塊對總線的訪問。雖然仲裁規(guī)范是AMBA總線規(guī)范中的一部分,但具體使用的算法由RTL設計工程師決定,其中兩個最常用的算法是固定優(yōu)先級算法和循環(huán)制算法。AHB總線上最多可以有16個主模塊和任意多個從模塊,如果主模塊數(shù)目大于16,則需再加一層結(jié)構(gòu)(具體參閱ARM公司推出的Multi-layer AHB規(guī)范)。

AHB-APB橋接器既是APB總線上唯一的主模塊,也是AHB總線上的從模塊。其主要功能是鎖存來自AHB系統(tǒng)總線的地址、數(shù)據(jù)和控制信號,并提供二級譯碼以產(chǎn)生APB外圍設備的選擇信號,從而實現(xiàn)AHB協(xié)議到APB協(xié)議的轉(zhuǎn)換。AXI-AHB橋接器跟AHB-APB橋接器具有類似的功能。

如上AMBA系統(tǒng)總線框圖,AXI總線連接嵌入式處理器、片內(nèi)RAM、DMA主機、ISP、CODEC等高速設備,AHB總線連接著PCIE、USB、HDMI、ROM等高速接口設備,APB總線連接UART、SPI、IIC、GPIO、TIMER等低速設備。這樣處理器就能通過這些總線及橋接器訪問到相應的從模塊。根據(jù)工作頻率不同,總線被設計成高速總線和低速總線:高速總線支持較高的時鐘頻率,擁有較高的數(shù)據(jù)帶寬和性能,但功耗也比較高,一般適用于處理器、DSP、DMA等高速設備的連接。低速總線工作頻率低,雖然性能差,但功耗也低,適合掛載串口等低速外設。

2.2.2 總線術(shù)語

- Transfer與transaction:transfer指的是傳輸1bit數(shù)據(jù),transaction是多個transfer的集合(在AXI里也成為一個burst)。Transaction是包含整個burst的傳輸,包括address/data/response。Transfer值的是單個信息的傳輸,比如一個address或一個data。

- Burst傳輸:在AXI協(xié)議中,一個transaction一般以一個burst為單位進行傳輸,burst的傳輸類型:FIXED、INCR、WRAP。

- Outstanding傳輸:表示正在進行中的傳輸,master在當前transaction任務完成之前,就可以開始進行下一個transaction,因此系統(tǒng)中可能存在多個outstanding的transaction。即一個transaction已經(jīng)發(fā)出,但還沒有得到response。

2.2.3 總線的性能指標

- 總線時鐘周期:機器的時鐘周期。計算機有一個統(tǒng)一的時鐘,以控制整個計算機的各個部件,總線也要受此時鐘的控制。大多數(shù)情況下,一個總線周期包含多個總線時鐘周期。有時,一個總線周期就是一個總線時鐘周期。有時,一個總線時鐘周期可包含多個總線周期。

- 總線的時鐘頻率:即機器的時鐘頻率,為總線時鐘周期的倒數(shù)。若總線時鐘周期為T,則總線時鐘頻率為1/T。實際上指一秒內(nèi)有多少個時鐘周期。

- 總線的傳輸周期(總線周期):一次總線操作所需的時間(包括申請階段、尋址階段、傳輸階段和結(jié)束階段),通常由若干個總線時鐘周期構(gòu)成。

- 總線的工作頻率:總線上各種操作的頻率,為總線周期的倒數(shù)。若總線周期=N個總線時鐘周期,則總線的工作頻率=時鐘頻率/N。實際上指一秒內(nèi)傳送幾次數(shù)據(jù)。

- 總線寬度:又稱為總線位寬,它是總線上同時能夠傳輸?shù)臄?shù)據(jù)位數(shù),通常是指數(shù)據(jù)總線的根數(shù),如32根稱為32位(bit)總線。

- 總線帶寬:可理解為總線的數(shù)據(jù)傳輸率,即單位時間內(nèi)總線上可傳輸數(shù)據(jù)的位數(shù),通常用每秒鐘傳送信息的字節(jié)數(shù)來衡量,單位可用字節(jié)/秒(B/s)表示。總線帶寬=總線工作頻率×總線寬度(bit/s)=總線工作頻率×(總線寬度/8)(B/s)=(總線寬度)/(總線周期)(bit/s)。總線帶寬是指總線本身所能達到的最高傳輸速率。在計算實際的有效數(shù)據(jù)傳輸率時,要用實際傳輸?shù)臄?shù)據(jù)量除以耗時。

- 總線復用:總線復用是指一種信號線在不同的時間傳輸不同的信息。可以使用較少的線傳輸更多的信息,從而節(jié)省了空間和成本。

- 信號線數(shù):地址總線、數(shù)據(jù)總線和控制總線3種總線數(shù)的總和稱為信號線數(shù)。

2.2.4 總線仲裁

由于總線上連接著許多模塊(設備),什么時候由哪個模塊發(fā)送信息,如何給信息傳送定時,如何防止信息丟失,如何避免多個模塊同時發(fā)送,如何規(guī)定接受信息的模塊等等一系列問題,都需要由總線控制器進行管理。它主要包括總線仲裁(或稱為總線判優(yōu)控制)和通信控制兩個方面。

總線上所連接的各類設備,按其對總線有無控制功能可分為主設備和從設備兩種。主設備對總線有控制權(quán),從設備只能響應從主設備發(fā)來的總線命令。總線上信息的傳送是由主設備啟動的。

如某個主設備想與另一個設備進行通信時,首先由主設備發(fā)出總線請求信號,若多個主設備同時要使用總線時,就由總線控制器的判優(yōu)、仲裁邏輯按一定的優(yōu)先等級順序,確定哪個主設備能先使用總線。只有獲得總線使用權(quán)的主設備才能開始傳送數(shù)據(jù)。

總線仲裁方式可分集中式和分布式兩種,前者有一個稱為總線控制器或仲裁器的硬件設備負責分配總線使用權(quán),這個設備可以是獨立的模塊,也可以是CPU的一部分。后者沒有明確的總線控制器,而是將控制邏輯功能分散在與總線連接的各個部件或設備中。

-

ARM

+關注

關注

134文章

9087瀏覽量

367390 -

總線

+關注

關注

10文章

2878瀏覽量

88053 -

AMBA

+關注

關注

0文章

68瀏覽量

14982

發(fā)布評論請先 登錄

相關推薦

AMBA AHB總線與APB總線資料合集

AMBA總線IP核的設計

總線概述之AMBA總線

ARM體系的特點與ARM的技術(shù)的簡介及AMBA總線的分析

AMBA 3.0 AXI總線接口協(xié)議的研究與應用

基于AMBA總線介紹?

深度解讀AMBA、AHB、APB、AXI總線介紹及對比

介紹AMBA2.0總線

深度分析AMBA總線工作原理1

深度分析AMBA總線工作原理1

評論