今天推出Xilinx已發布的《Vivado使用誤區與進階》系列:用TCL定制Vivado設計實現流程。

上一篇《Tcl在Vivado中的應用》介紹了Tcl的基本語法以及如何利用Tcl在Vivado中定位目標。其實Tcl在Vivado中還有很多延展應用,接下來我們就來討論如何利用Tcl語言的靈活性和可擴展性,在Vivado中實現定制化的FPGA設計流程。

基本的 FPGA 設計實現流程

FPGA的設計流程簡單來講,就是從源代碼到比特流文件的實現過程。大體上跟IC設計流程類似,可以分為前端設計和后端設計。其中前端設計是把源代碼綜合為對應的門級網表的過程,而后端設計則是把門級網表布局布線到芯片上最終實現的過程。

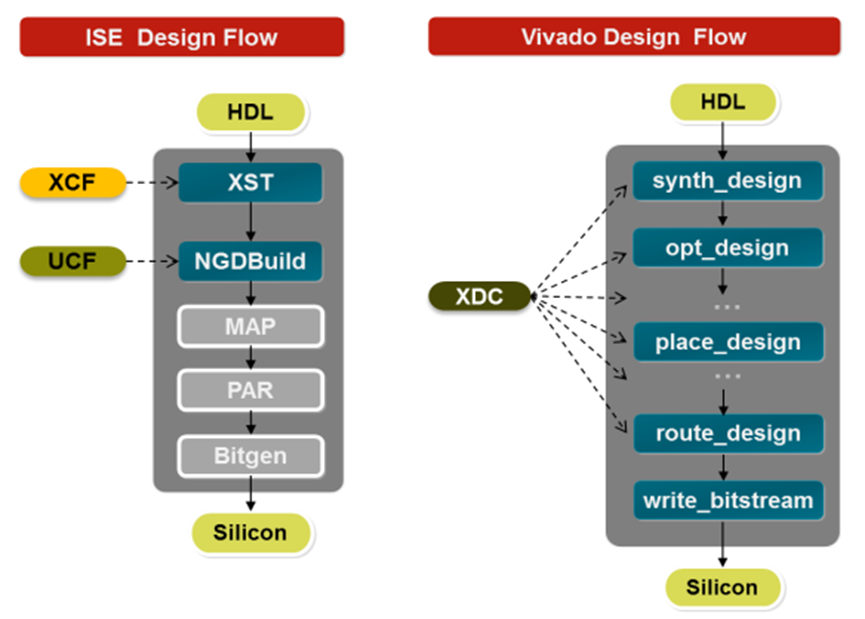

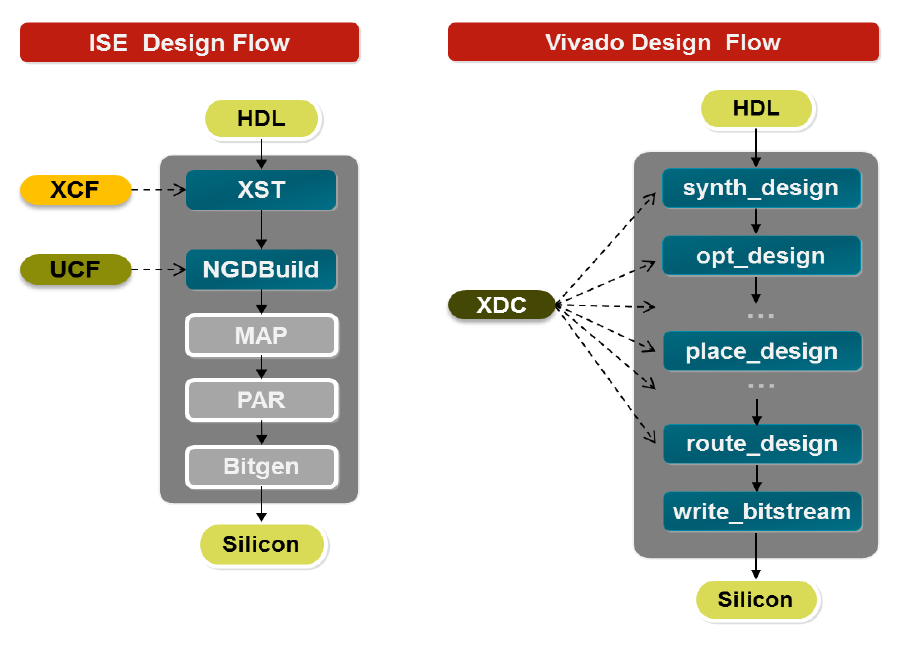

以下兩圖分別表示ISE和Vivado的基本設計流程:

ISE中設計實現的每一步都是相對獨立的過程,數據模型各不相同,用戶需要維護不同的輸入文件,例如約束等,輸出文件也不是標準網表格式,并且形式各異,導致整體運行時間過長,冗余文件較多。

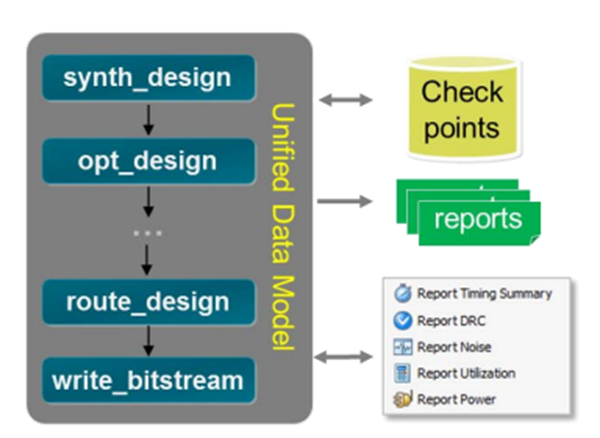

Vivado中則統一了約束格式和數據模型,在設計實現的任何一個階段都支持XDC約束,可以生成時序報告,在每一步都能輸出包含有網表、約束以及布局布線信息(如果有)的設計檢查點(DCP)文件,大大縮短了運行時間。

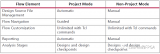

從使用方式上來講,Vivado支持工程模式(Project Based Mode)和非工程模式(None Project Mode)兩種,且都能通過Tcl腳本批處理運行,或是在Vivado圖形化界面IDE中交互運行和調試。

工程模式

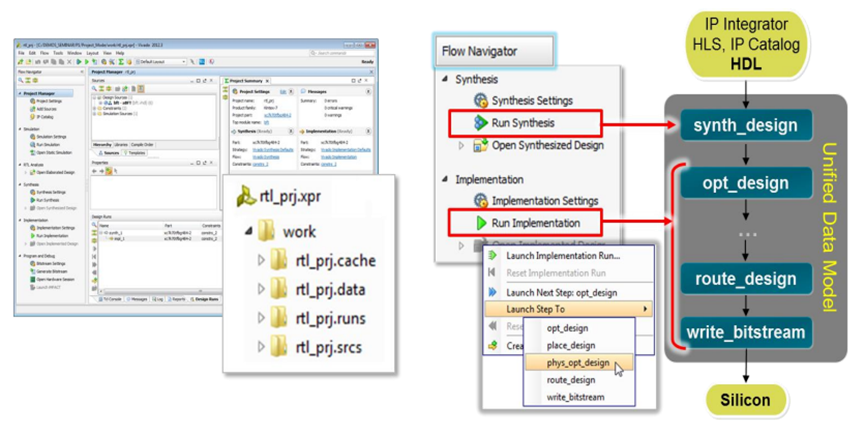

工程模式的關鍵優勢在于可以通過在Vivado中創建工程的方式管理整個設計流程,包括工程文件的位置、階段性關鍵報告的生成、重要數據的輸出和存儲等。

如下左圖所示,用戶建立了一個Vivado工程后,工具會自動創建相應的.xpr工程文件,并在工程文件所在的位置同層創建相應的幾個目錄,包括.cache、.data、.runs和.srcs等等(不同版本可能有稍許差異),分別用于存儲運行工程過程中產生的數據、輸出的文件和報告以及工程的輸入源文件(包含約束文件)等。

如下右圖所示,在Vivado IDE中還可以一鍵式運行整個設計流程。這些預置的命令按鈕就放置在工具最左邊的側欄:Flow Navigator。不同按鈕對應不同的實現過程,其中在后端實現階段,還可以用右鍵調出詳細分步命令,指引工具具體執行實現的哪一步。

特別需要指出的是Flow Navigator只有在Vivado IDE中打開.xpr工程文件才會顯示,如果打開的是設計檢查點.dcp文件(不論是工程模式或是非工程模式產生的dcp)都不會顯示這個側欄。

非工程模式

非工程模式下,由于不會創建工程,用戶就需要自己管理設計源文件和設計過程。源文件只能從當前位置訪問,在設計實現過程中的每一步,數據和運行結果都存在于Vivado分配到的機器內存中,在用戶不主動輸出的情況下,不會存儲到硬盤中。

簡單來講,非工程模式提供了一種類似ASIC設計的流程,用戶擁有絕對的自由,可以完全掌控設計實現流程,但也需要用戶對設計實現的過程和數據,尤其對文件輸出和管理全權負責,包括何時、何地、輸出怎樣的文件等等。

使用非工程模式管理輸入輸出文件、進行設計實現都需要使用Tcl腳本,但這并不代表非工程模式不支持圖形化界面。非工程模式下產生的.dcp文件一樣可以在Vivdao IDE中打開,繼而產生各種報告,進行交互式調試等各種在圖形化下更便捷直觀的操作。這是一個常見誤區,就像很多人誤認為工程模式下不支持Tcl腳本運行是一個道理。但兩種模式支持的Tcl命令確實是完全不同的,使用起來也不能混淆。

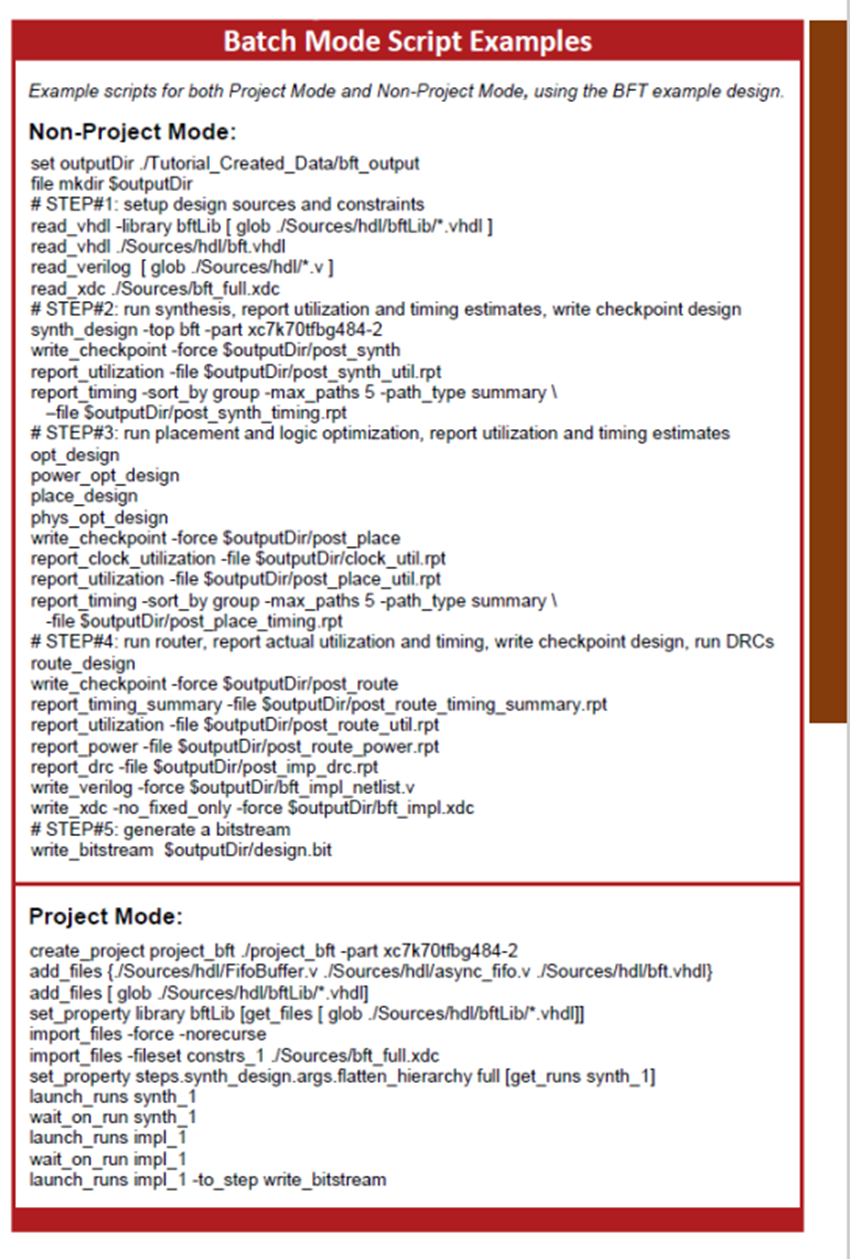

下圖所示是同一個設計(Vivado自帶的Example Design)采用兩種模式實現所需使用的不同腳本,更詳細的內容可以在UG975和UG835中找到。需要注意的是,工程模式下的Tcl腳本更簡潔,但并不是最底層的Tcl命令,實際執行一條相當于執行非工程模式下的數條Tcl命令。

Tcl對圖形化的補充

相信對大部分FPGA工程設計人員來說,圖形化界面仍舊是最熟悉的操作環境,也是設計實現的首選。在Xilinx推出全面支持Tcl的Vivado后,這一點依然沒有改變,但我們要指出的是,即使是在圖形化界面上跑設計,仍然可以充分利用Tcl的優勢。在Vivado IDE上運行Tcl腳本主要有以下幾個渠道。

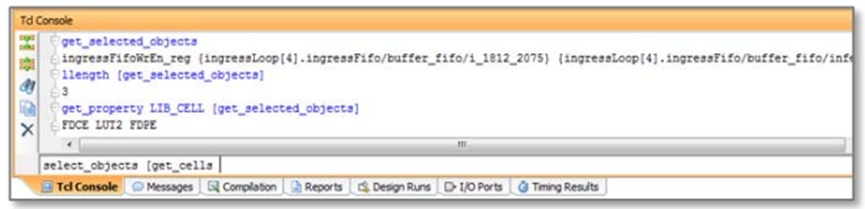

Tcl Console

Vivado IDE的最下方有一個Tcl Console,在運行過程中允許用戶輸入Tcl/XDC命令或是source預先寫好的Tcl腳本,返回值會即時顯示在這個對話框。

舉例來說,設計調試過程中,需要將一些約束應用在某些網表目標上(具體可參照《Tcl在Vivado中的應用》所示),推薦的做法就是在IDE中打開.dcp然后在Tcl Console中輸入相應的Tcl/XDC命令,驗證返回值,碰到問題可以直接修改,直到找到正確合適的命令。然后可以記錄這些命令,并存入XDC文件中以備下次實現時使用。

還有一種情況是,預先讀入的XDC中有些約束需要修改,或是缺失了某些重要約束。不同于ISE中必須修改UCF重跑設計的做法,在Vivado中,我們可以充分利用Tcl/XDC的優勢,在Tcl Console中輸入新的Tcl/XDC,無需重跑設計,只要運行時序報告來驗證。當然,如果能重跑設計,效果會更好,但是這種方法在早期設計階段提供了一種快速進行交互式驗證的可能,保證了更快地設計迭代,大大提升了效率。

另外,通過某些Tcl命令(例如show_objects、select_objects等等)的幫助,我們還可以利用Tcl Console與時序報告、RTL和門級網表以及布局布線后的網表之間進行交互調試,極大發揮Vivado IDE的優勢。

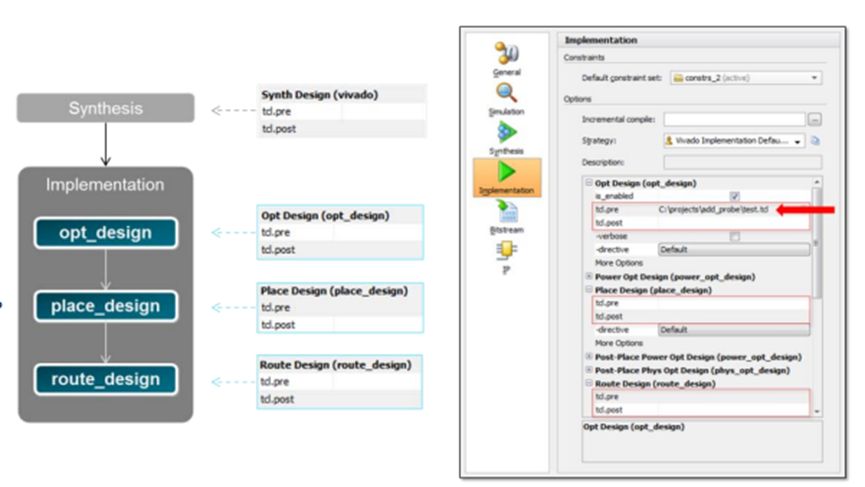

Hook Scripts

Vivado IDE中內置了tcl.pre和tcl.post,用戶可以在Synthesis和Implementation的設置窗口中找到。設計實現的每一步都有這樣兩個位置可供用戶加入自己的Tcl腳本。

tcl.pre表示當前這步之前Vivado會主動source的Tcl腳本,tcl.post表示這步之后會source的腳本。

Tcl腳本必須事先寫好,然后在上圖所示的設置界面由用戶使用彈出窗口指定到腳本所在位置。

這些就是所謂的“鉤子”腳本,正是有了這樣的腳本,我們才得以在圖形化界面上既享有一鍵式執行的便利,又充分利用Tcl帶來的擴展性。比較常見的使用場景是,在某個步驟后多產生幾個特別的報告,或是在布線前再跑幾次物理優化等。

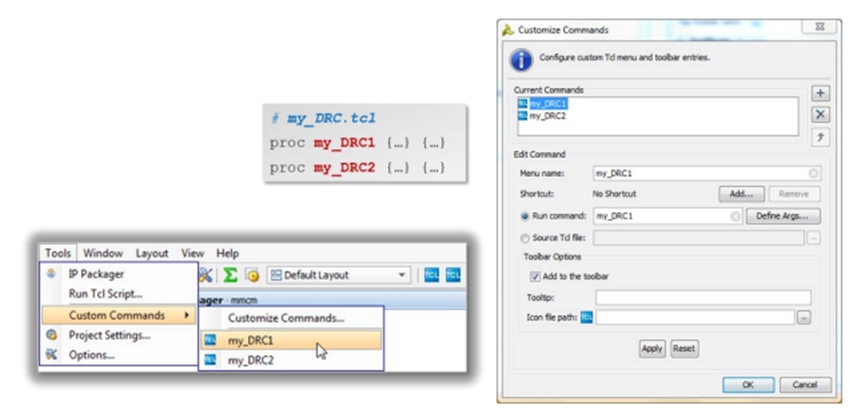

Customer Commands

Vivado IDE中還有一個擴展功能,允許用戶把事先創建好的Tcl腳本以定制化命令的方式加入圖形化界面,成為一個按鈕,方便快速執行。這個功能常常用來報告特定的時序信息、修改網表內容、實現ECO等等。

用Tcl定制實現流程

綜上所述,標準的FPGA設計實現流程完全可以通過Vivado IDE一鍵式執行,如果僅需要少量擴展,通過前述鉤子腳本等幾種方法也完全可以做到。若是這些方法都不能滿足需求,還可以使用Tcl腳本來跑設計,從而實現設計流程的全定制。

注:以下討論的幾種實現方案中僅包含后端實現具體步驟的區別,而且只列出非工程模式下對應的Tcl命令。

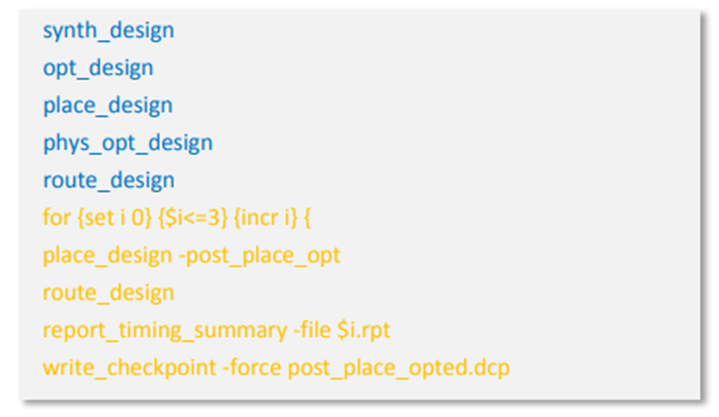

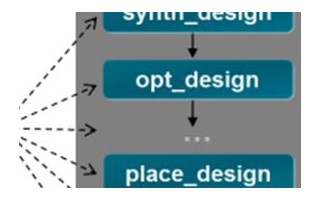

右圖所示是Vivado中設計實現的基本流程,藍色部分表示實現的基本步驟(盡管opt_design這一步理論上不是必選項,但仍強烈建議用戶執行),對應Implementation的Default策略。黃色部分表示可選擇執行的部分,不同的實現策略中配置不同。

這里不會討論那些圖形化界面中可選的策略,不同策略有何側重,具體如何配置我們將在另外一篇關于Vivado策略選擇的文章中詳細描述。

我們要展示的是如何對設計流程進行改動來更好的滿足設計需求,這些動作往往只能通過Tcl腳本來實現。

充分利用物理優化

物理優化即phys_opt_design是在后端通過復制、移動寄存器來降扇出和retiming,從而進行時序優化的重要手段,一般在布局和布線之間運行,從Vivado 2014.1開始,還支持布局后的物理優化。

很多用戶會在Vivado中選中phys_opt_design,但往往不知道這一步其實可以運行多次,并且可以選擇不同的directive來有側重的優化時序。

比如,我們可以寫這樣一個Tcl腳本,在布局后,使用不同的directive或選項來跑多次物理優化,甚至可以再多運行一次物理優化,專門針對那些事先通過get_nets命令找到并定義為highfanout_nets的高扇出網絡具體directive的含義可以通過UG835、UG904或phys_opt_design -help命令查詢。

布局布線之間的多次物理優化不會惡化時序,但會增加額外的運行時間,也有可能出現時序完全沒有得到優化的結果。布線后的物理優化有時候會惡化THS,所以請一定記得每一步后都運行report_timing_summary,并且通過write_checkpoint寫出一個.dcp文件來保留階段性結果。這一步的結果不理想就可以及時退回到上一步的.dcp繼續進行。

閉環設計流程

通常的FPGA設計流程是一個開環系統,從前到后依次執行。但Vivado中提供了一種可能,用戶可以通過place_design -post_place_opt在已經完成布局布線的設計上再做一次布局布線,從而形成一個有了反饋信息的閉環系統。這次因為有了前一次布線后的真實連線延遲信息,布局的針對性更好,并且只會基于時序不滿足的路徑進行重布局而不會改變大部分已經存在的布局信息,之后的布線過程也是增量流程。

這一過程所需的運行時間較短,是一種很有針對性的時序優化方案。可以通過Tcl寫一個循環多次迭代運行,但需留意每次的時序報告,若出現時序惡化就應及時停止。

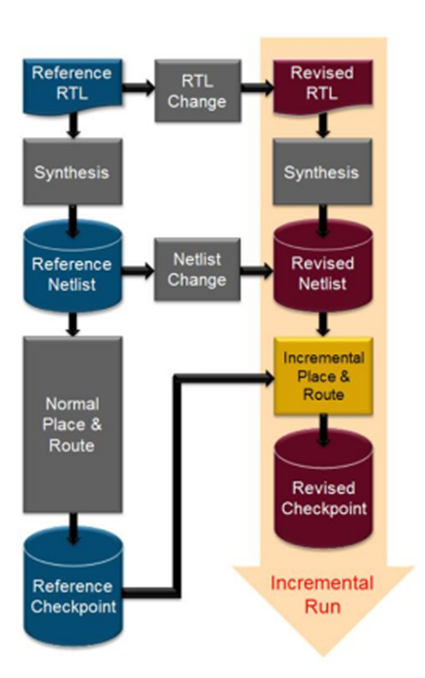

增量設計流程

Vivado中的增量設計也是一個不得不提的功能。當設計進行到后期,每次運行改動很小,在開始后端實現前讀入的設計網表具有較高相似度的情況下,推薦使用Vivado的增量布局布線功能。

如上圖所示,運行增量流程的前提是有一個已經完成布局布線的.dcp文件,并以此用來作為新的布局布線的參考。

運行過程中,Vivado會重新利用已有的布局布線數據來縮短運行時間,并生成可預測的結果。當設計有95%以上的相似度時,增量布局布線的運行時間會比一般布局布線平均縮短2倍。若相似度低于80%,則使用增量布局布線只有很小的優勢或者基本沒有優勢。

除了縮短運行時間外,增量布局布線對沒有發生變化的設計部分造成的破壞也很小,因此能減少時序變化,最大限度保留時序結果,所以一般要求用做參考的.dcp文件必須是一個完全時序收斂的設計。

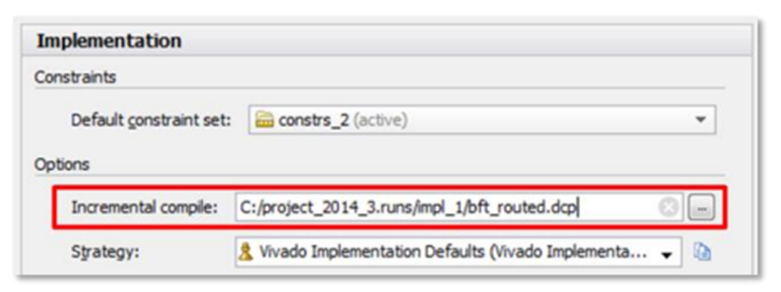

參考點.dcp文件可以在Vivado IDE的Implementation設置中指定,也可以在Tcl腳本中用read_checkpoint -incremental讀入。特別需要指出的是,在工程模式中,如要在不新建一個impl實現的情況下使用上一次運行的結果作為參考點,必須將其另存到這次運行目錄之外的位置,否則會因沖突而報錯。

以上用Tcl定制Vivado設計實現流程的討論就到這里,后面我將就Tcl使用場景,包括ECO流程等的更多細節進行展開。

-

FPGA

+關注

關注

1645文章

22021瀏覽量

617351 -

Xilinx

+關注

關注

73文章

2184瀏覽量

124968 -

TCL

+關注

關注

11文章

1782瀏覽量

89854 -

時序

+關注

關注

5文章

397瀏覽量

37909 -

Vivado

+關注

關注

19文章

834瀏覽量

68604

原文標題:用 TCL 定制 Vivado 設計實現流程

文章出處:【微信號:HXSLH1010101010,微信公眾號:FPGA技術江湖】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

VIVADO從此開始高亞軍編著

Vivado設計之Tcl定制化的實現流程

Tcl在Vivado中的基礎應用

Vivado使用誤區與進階——在Vivado中實現ECO功能

如何使用Tcl命令語言讓Vivado HLS運作

如何用Tcl實現Vivado設計流程介紹

評論