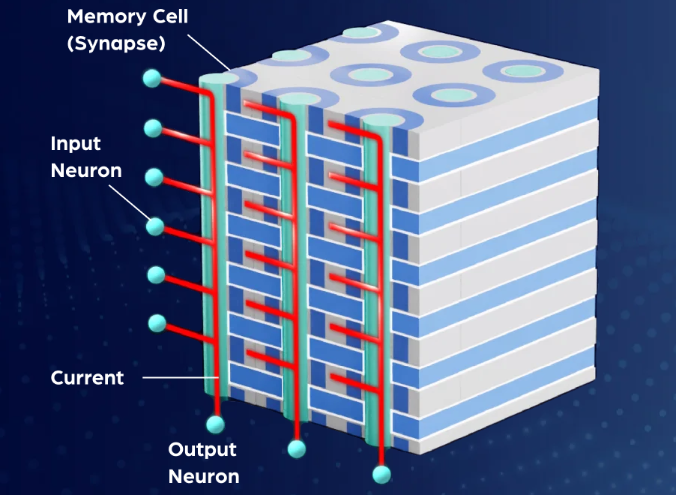

在邊緣計(jì)算領(lǐng)域里,對(duì)DRAM帶寬的要求遠(yuǎn)高于容量,此時(shí)采用Chiplet方式集成3D DRAM存儲(chǔ)方案,就可以同時(shí)提供高帶寬和低功耗。

今年2月,在正式加入U(xiǎn)CIe(Universal Chiplet Interconnect Express)產(chǎn)業(yè)聯(lián)盟之后,華邦電子隨即宣布其創(chuàng)新產(chǎn)品CUBE: 3D TSV DRAM和3DCaaS(3D CUBE as a Service)一站式服務(wù)平臺(tái),將成為公司向客戶提供優(yōu)質(zhì)定制化內(nèi)存的首選解決方案。

芯片微縮化的“續(xù)命良藥”

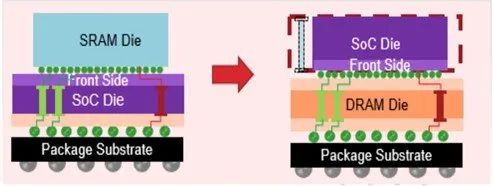

CUBE是Customized/Compact Ultra Bandwidth Elements,即“半定制化緊湊型超高帶寬DRAM”的簡(jiǎn)稱。華邦電子次世代內(nèi)存產(chǎn)品營(yíng)銷企劃經(jīng)理曾一峻在向《電子工程專輯》說(shuō)明CUBE核心價(jià)值時(shí)表示,新能源汽車、5G、可穿戴設(shè)備等領(lǐng)域的不斷發(fā)展,對(duì)芯片性能的需求越來(lái)越高,但如果采用諸如“直接在5nm SoC裸片上堆疊7nm SRAM裸片”的做法,會(huì)因?yàn)閹胩郥SV工藝架構(gòu)而導(dǎo)致芯片成本暴漲。

于是,采用先進(jìn)封裝技術(shù)的Chiplet成為了芯片微縮化進(jìn)程的“續(xù)命良藥”。“這也是華邦解決方案的思路”,按照曾一峻的解釋,在邊緣計(jì)算領(lǐng)域,華邦將SoC裸片置上,DRAM裸片置下,省去了SoC中的TSV工藝(圖中虛線部分所示),從而大幅降低了SoC裸片的尺寸與成本。與此同時(shí),3D DRAM TSV工藝又可以將SoC信號(hào)引至外部,使它們成為同一顆芯片,進(jìn)一步縮減了封裝尺寸。

另一方面,考慮到現(xiàn)在的AI芯片都有著很高的算力需求,SoC裸片置上也可以帶來(lái)更好的散熱效果。因此,華邦方面認(rèn)為,按照這樣的方式進(jìn)行CUBE 3D DRAM 裸片堆疊可以帶來(lái)高帶寬、低功耗和優(yōu)秀的散熱表現(xiàn),這也是華邦CUBE解決方案主要面向低功耗、高帶寬、中低容量?jī)?nèi)存需求應(yīng)用的主要原因。

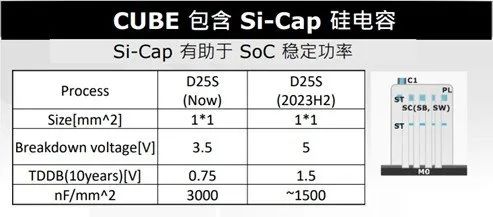

眾所周知,DRAM裸片中都會(huì)包含電容,華邦CUBE芯片也不例外。目前,先進(jìn)制程SoC芯片的核心電壓約為0.75V-1V,運(yùn)行過(guò)程中電源產(chǎn)生的波動(dòng)會(huì)影響功耗和信號(hào)穩(wěn)定性。但CUBE芯片所采用的硅電容(Si-Cap)卻可以有效降低電源波動(dòng)帶來(lái)的影響。

下圖是華邦當(dāng)前硅電容規(guī)格和制程的進(jìn)展。可以看到,盡管電容縮小到了原來(lái)的一半,但是運(yùn)行的經(jīng)時(shí)擊穿電壓(TDDB)卻被提高了1倍至1.5V(這也是目前大部分先進(jìn)制程芯片的核心電壓),擊穿電壓也是目前先進(jìn)制程所需的5V,因此1500nF/(mm2)是完全符合目前先進(jìn)制程芯片的電容需求。而根據(jù)規(guī)劃,下半年還會(huì)有更優(yōu)規(guī)格的硅電容產(chǎn)品面世。

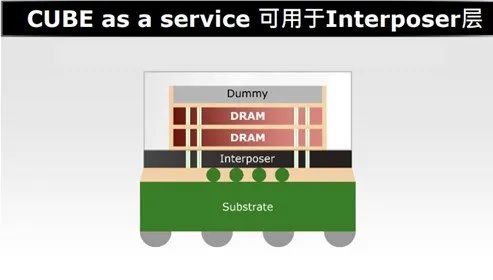

再來(lái)關(guān)注一下華邦DRAM堆疊和中介層(Interposer)架構(gòu)的演進(jìn)。如圖所示,由于中介層也是華邦提供,因此客戶可以得到一個(gè)包括DRAM、中介層、硅電容在內(nèi)的整體解決方案,這也是華邦加入U(xiǎn)CIe后做出的貢獻(xiàn)之一。

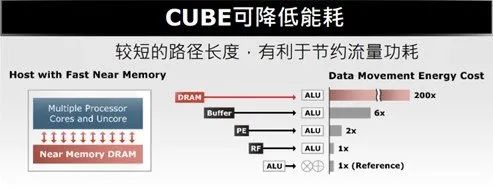

另一個(gè)值得關(guān)注的優(yōu)勢(shì)來(lái)自功耗的降低。由于SoC裸片和DRAM裸片堆疊的時(shí)候,相比于傳統(tǒng)的引線鍵合(Wire Bonding),微鍵合(Micro Bonding)工藝可以將1000微米的線長(zhǎng)縮短至40微米,僅有傳統(tǒng)長(zhǎng)度的2.5%,在未來(lái)的混合鍵合(Hybrid Bonding)封裝工藝下,線長(zhǎng)甚至可以縮短至1微米。這意味著在芯片內(nèi)部,信號(hào)所經(jīng)過(guò)的傳輸距離更短,功耗自然也得到相應(yīng)的降低。此外,當(dāng)采用混合鍵合工藝時(shí),兩顆堆疊的芯片其實(shí)可以被看作同一顆芯片,因此內(nèi)部傳輸信號(hào)和SIP表現(xiàn)會(huì)更優(yōu)秀。

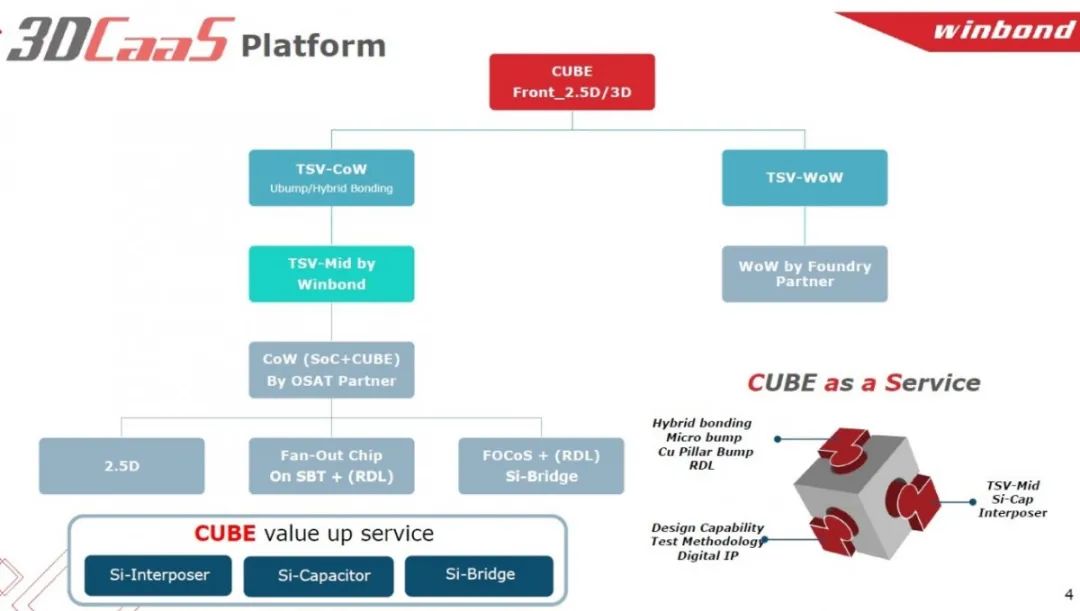

與CUBE同時(shí)出現(xiàn)的還包括3D CaaS平臺(tái),也就是 CUBE as a Service。這意味著對(duì)于客戶來(lái)說(shuō),華邦不僅僅提供3D TSV DRAM KGD內(nèi)存芯片和針對(duì)多芯片設(shè)備優(yōu)化的2.5D/3D后段工藝(采用CoW/WoW),還可獲取由華邦的平臺(tái)合作伙伴提供的技術(shù)咨詢服務(wù),是一套完整且全面的CUBE產(chǎn)品支持,并享受Silicon-Cap、interposer等技術(shù)的附加服務(wù)。

CUBE應(yīng)用架構(gòu)

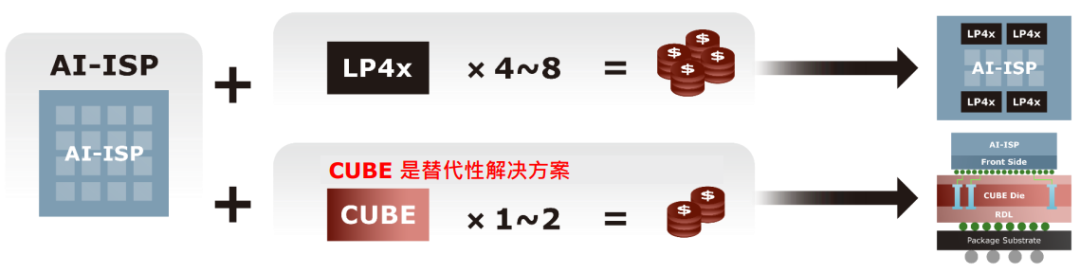

ChatGPT的面世帶動(dòng)了AI應(yīng)用領(lǐng)域的再次火熱,而CUBE就可以應(yīng)用到AI-ISP架構(gòu)中。

上圖中的灰色部分代表AI-ISP中的神經(jīng)網(wǎng)絡(luò)處理器(NPU),如果AI-ISP要實(shí)現(xiàn)大算力,就需要很大的帶寬,或者是SPRAM加持。但目前來(lái)看,在AI-ISP上使用SPRAM成本高昂,轉(zhuǎn)而使用LPDDR4則需要4-8顆,如果用到傳輸速度為4266Mhz的高速LPDDR4,還需要依賴7nm或12nm的先進(jìn)制程工藝。

相比之下,CUBE解決方案就可以允許客戶使用成熟制程(28nm/22nm)獲得類似的高速帶寬。簡(jiǎn)單而言,CUBE芯片可以通過(guò)多個(gè)I/O(256或者512個(gè))結(jié)合28nm SoC提供500MHz運(yùn)行頻率,以及最高256GB/s帶寬。據(jù)透露,華邦在未來(lái)可能會(huì)和客戶共同探討64GB/s帶寬的合作可能性,如果成功,I/O數(shù)量和裸片尺寸都將進(jìn)一步縮小。

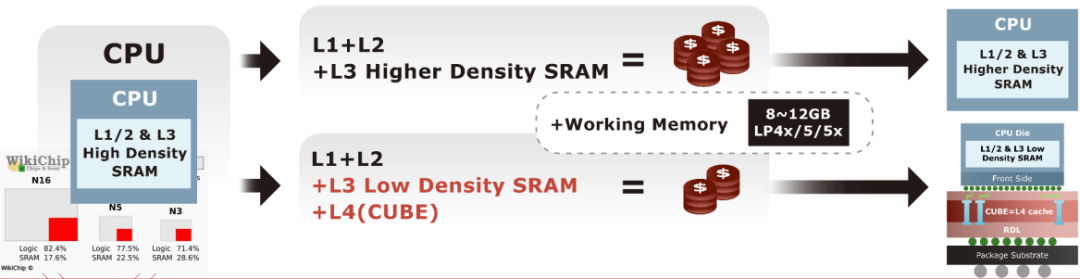

在下面的應(yīng)用場(chǎng)景中,CPU的高速運(yùn)算需求對(duì)制程的要求從16nm、7nm、5nm到3nm,越來(lái)越高。但不難發(fā)現(xiàn),盡管制程工藝越來(lái)越先進(jìn),圖中紅色部分所代表的SRAM占比并沒有同比例縮小,因此當(dāng)需要實(shí)現(xiàn)AI運(yùn)算或者高速運(yùn)算的情況下,就需要將L3緩存SRAM容量加大,即便采用堆疊方式達(dá)到幾百M(fèi)B,也會(huì)導(dǎo)致高昂的成本。

華邦的做法是將L3緩存縮小,轉(zhuǎn)而使用L4緩存的CUBE解決方案。這并不意味著CUBE解決方案的時(shí)鐘傳播延遲(Latency)等同于SRAM,而是可以作為L(zhǎng)4緩存。原因在于CUBE可以進(jìn)行定制化的設(shè)計(jì),使得時(shí)鐘傳播延遲比一般的DRAM還要短。同時(shí),考慮到AI模型在某些情況下需要外置一定容量的內(nèi)存,例如在某些邊緣計(jì)算場(chǎng)景下會(huì)需要8-12GB LPDDR4/LPDDR5,因此在需要的情況下,也可以外掛高容量工作內(nèi)存(Working Memory)。

“在邊緣計(jì)算領(lǐng)域里,對(duì)DRAM帶寬的要求遠(yuǎn)高于容量,此時(shí)采用Chiplet方式集成類似CUBE的存儲(chǔ)方案,就可以同時(shí)提供高帶寬和低功耗。”但曾一峻也同時(shí)強(qiáng)調(diào)稱,畢竟Chiplet芯片需要兼容多個(gè)接口協(xié)議才能避免造成信號(hào)偏差,因此,如何進(jìn)一步縮小3D DRAM的裸片尺寸,如何更好的實(shí)現(xiàn)不同芯粒間的互聯(lián)互通,是繞不開的挑戰(zhàn)。

華邦DRAM技術(shù)路線圖

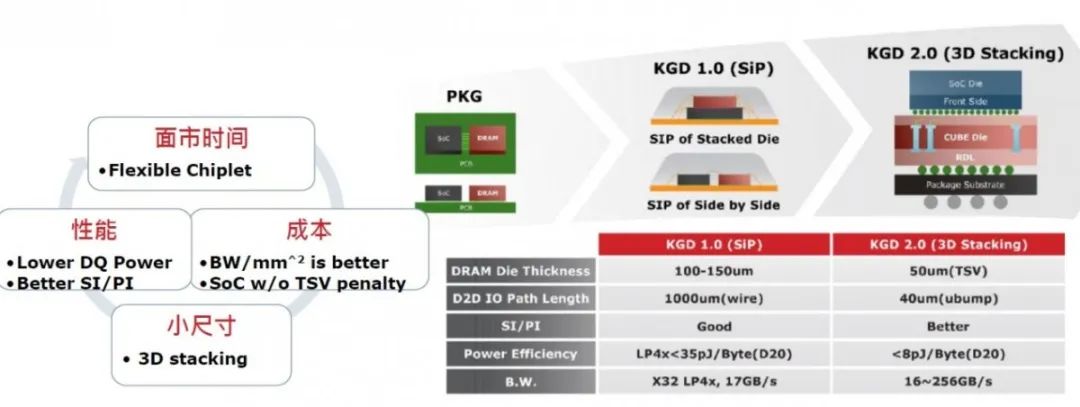

相對(duì)于市場(chǎng)上三大頭部?jī)?nèi)存廠商而言,華邦主要專注于利基型內(nèi)存,產(chǎn)品容量一般最大為8GB,其特點(diǎn)是不需要非常先進(jìn)的制程,并以KGD為主,便于與SoC進(jìn)行合封。

在KGD 1.0(SiP)中,DRAM Die厚度約為100-150微米,裸片至裸片(Die to Die)的I/O路徑為1000微米,目前這種性能的KGD信號(hào)完整性/電源完整性(SI/PI)是主流的,也是夠用的。華邦方面曾經(jīng)對(duì)LPDDR4的電源效率進(jìn)行過(guò)估算,其小于35pJ/Byte,帶寬方面X32 LPDDR4x每I/O為17GB/s。

當(dāng)進(jìn)化到KGD 2.0(3D堆疊)后,得益于TSV的深寬比能力,DRAM Die厚度可以達(dá)到50微米的深度,未來(lái),通過(guò)Hybrid Bonding工藝還可以實(shí)現(xiàn)1微米的距離。同時(shí),信號(hào)完整性/電源完整性(SI/PI)性能更好,功耗更低,可以達(dá)到甚至低于LPDDR4的四分之一(為8pJ/Byte),而帶寬可以實(shí)現(xiàn)16-256GB/s。

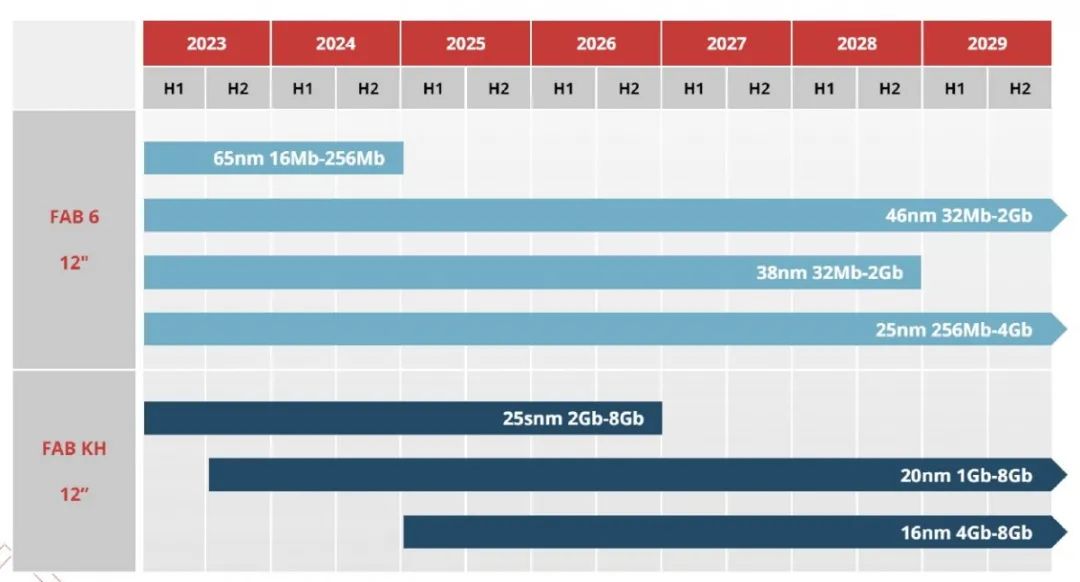

目前,華邦擁有兩座12寸晶圓廠,一座是位于臺(tái)中的Fab 6工廠,另一座是在高雄新建的第二座工廠,其產(chǎn)能為1萬(wàn)片/月左右,后續(xù)將逐漸提升至1.4萬(wàn)片-2萬(wàn)片/月。

從制程工藝角度來(lái)看,高雄工廠投產(chǎn)后,華邦會(huì)將一些先進(jìn)制程的DRAM產(chǎn)能轉(zhuǎn)移至高雄廠,臺(tái)中廠的中小容量DRAM制程會(huì)維持在65nm、46nm、38nm和25nm,且無(wú)意再向更小制程演進(jìn),而是專注于成熟制程產(chǎn)品。高雄廠已經(jīng)量產(chǎn)的包括25nm 2GB和4GB兩種產(chǎn)品,20nm產(chǎn)品預(yù)計(jì)在今年年中進(jìn)入量產(chǎn)階段,并繼續(xù)向19nm制程演進(jìn)。

華邦電子大陸區(qū)產(chǎn)品營(yíng)銷處處長(zhǎng)朱迪再次強(qiáng)調(diào)了華邦對(duì)于DDR3的生產(chǎn)和支持。盡管他認(rèn)為像三星這樣的大廠逐漸舍棄DDR3和中小容量DDR4是一個(gè)大概率的事件,但從實(shí)際使用情況來(lái)看,4Gb DDR3產(chǎn)品將有望繼續(xù)被廣泛采用至少到2027-2028年,尤其在工業(yè)和汽車領(lǐng)域需要長(zhǎng)期支持。而且,相同容量相同速度下,DDR3較DDR4更具成本效益(相同制程下,與DDR3相比,Die尺寸DDR4增加10%,LPDDR4增加18%),DDR4將會(huì)持續(xù)向更高容量發(fā)展,并隨著PC和服務(wù)器市場(chǎng)的需求遷移至DDR5。

根據(jù)規(guī)劃,DDR3仍將保持1Gb、2Gb、4Gb和8Gb四種容量,并計(jì)劃在2025年演進(jìn)至16nm;DDR4方面,當(dāng)20nm制程就緒之后,高雄廠會(huì)在2024年初量產(chǎn)DDR4 DRAM芯片。

“利基型存儲(chǔ)市場(chǎng)大約只占整個(gè)存儲(chǔ)市場(chǎng)的10%,它的供需相對(duì)而言是比較平衡和穩(wěn)定的。在當(dāng)前終端客戶、代理商、以及原廠庫(kù)存都比較低的情況下,確實(shí)有可能會(huì)出現(xiàn)缺貨的情況,但對(duì)具體時(shí)間節(jié)點(diǎn)做出判斷為時(shí)尚早,需要做進(jìn)一步的觀察。”朱迪說(shuō)。

審核編輯 :李倩

-

芯片

+關(guān)注

關(guān)注

455文章

50732瀏覽量

423266 -

可穿戴設(shè)備

+關(guān)注

關(guān)注

55文章

3814瀏覽量

167013 -

chiplet

+關(guān)注

關(guān)注

6文章

431瀏覽量

12587

原文標(biāo)題:3D DRAM,Chiplet芯片微縮化的“續(xù)命良藥”

文章出處:【微信號(hào):wc_ysj,微信公眾號(hào):旺材芯片】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

2.5D/3D封裝技術(shù)升級(jí),拉高AI芯片性能天花板

3D掃描技術(shù)醫(yī)療領(lǐng)域創(chuàng)新實(shí)踐,積木易搭3D掃描儀Mole助力定制個(gè)性化手臂康復(fù)輔具

3D DRAM內(nèi)嵌AI芯片,AI計(jì)算性能暴增

SK海力士5層堆疊3D DRAM制造良率已達(dá)56.1%

SK海力士五層堆疊的3D DRAM生產(chǎn)良率達(dá)到56.1%

三星已成功開發(fā)16層3D DRAM芯片

三星電子研發(fā)16層3D DRAM芯片及垂直堆疊單元晶體管

3D DRAM進(jìn)入量產(chǎn)倒計(jì)時(shí),3D DRAM開發(fā)路線圖

3D DRAM,Chiplet芯片微縮化的“續(xù)命良藥”

3D DRAM,Chiplet芯片微縮化的“續(xù)命良藥”

評(píng)論