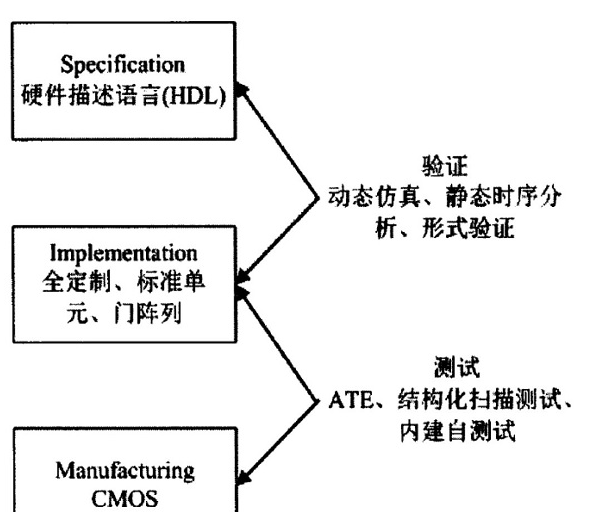

DFT是確保芯片在制造過程中具有可測試性的一種技術。DFT友好的ECO是指在進行ECO時, 不會破壞芯片的DFT功能或降低DFT覆蓋率的設計方法。DFT不友好的ECO會對芯片的測試和調試帶來很大的困難,可能導致芯片測試效率降低甚至無法測試。

因此,在進行功能性ECO時,需要特別注意DFT功能的保護。一般來說,可以將DFT邏輯設置為非活動模式,以防止任何功能性更改對其產生影響。但是,在進行ECO時需要特別注意,涉及DFT路徑的ECO是否會對DFT邏輯產生影響。如果ECO涉及DFT路徑,可能需要重新評估ECO的影響,以確保DFT邏輯不受影響。

此外,DFT友好的ECO應確保掃描鏈完整,時鐘和復位信號可控。這是為了確保芯片在測試和調試過程中可以正確地工作。因此,在進行ECO時,需要注意這些方面的設計和實現。如果一個功能ECO破壞了DFT功能或降低了DFT覆蓋率,則稱其為DFT不友好的ECO。而DFT友好的ECO應確保DFT功能不受影響,掃描鏈完整,時鐘和復位信號可控。

一、在相鄰寄存器中插入ECO

其中一個例子是在部分掃描鏈中在相鄰寄存器上執行ECO插入,例如從A_REG到D_REG所示的鏈路,其中B_REG和C_REG形成相鄰路徑。在這種情況下,ECO之前, C_REG可以是非掃描寄存器, 而DFT是完好的。

如果ECO在從A_REG到D_REG的掃描鏈中的B_REG和C_REG之間插入組合邏輯,并且C_REG是非掃描寄存器,則掃描鏈將被打破,如圖 2 所示。Conformal ECO會通過在此類ECO中直接插入后續路徑中的邏輯,而不考慮保持掃描鏈的需要,從而破壞DFT。

圖2

為了解決ECO引起的掃描鏈斷裂問題,GOF的解決方案涉及將C_REG的類型從非掃描寄存器更改為掃描寄存器,并根據圖 3 所示的方式正確連接掃描鏈。

圖3

圖3

二、選擇適合的DFT信號

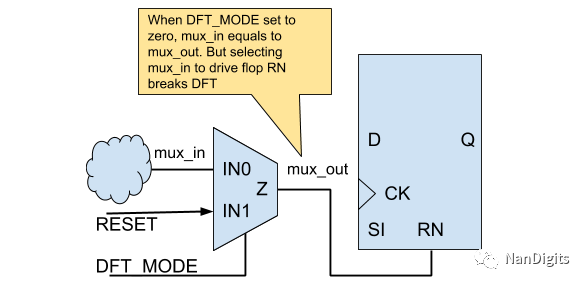

為確保在功能ECO期間DFT邏輯保持不活動狀態,需要將DFT_MODE信號設置為零。然而,有些信號可能是等效的,但不適合用于DFT,這可能會導致DFT失效。例如,在圖 4 中,一個ECO必須選擇mux_in或mux_out信號來驅動寄存器的復位引腳。雖然這兩個信號是等效的,但是Conformal ECO選擇了mux_in,這破壞了DFT。相比之下,GOF可以識別MUX并選擇mux_out作為復位引腳的正確信號,從而保持DFT邏輯的完整性。

圖4

三、可重置和可設置型寄存器交換

在執行功能性網表 ECO 時,常常需要在可重置和可設置型寄存器之間進行交換。這個操作被認為是一種簡單和直接的方式,只需交換相同的寄存器實例。然而,在圖 5 中,Cadence Conformal 引入了一種冗余的方法,使用了一個新的可設置型寄存器 reg1_1,而不是直接將原始的寄存器轉換為可設置型。新的寄存器 reg1_1 驅動原始的功能電路,而舊的寄存器 reg1 驅動掃描鏈扇出 reg2。這種方法存在兩個主要問題。首先,新的寄存器 reg1_1 沒有包含在掃描鏈中。在存在許多這樣的重置/設置型寄存器交換的情況下(約占所有寄存器數量的 0.2%),將會導致 ATPG at-speed覆蓋率約 0.2% 的損失。其次,Conformal LEC 未將新的寄存器 reg1_1 視為寄存器 reg1 的等效關鍵點,在 ECO 后的等效性報告中會出現大量的非等效點。

圖5

圖 6 所示的ECO中,GOF采用了一種直接的方法,將寄存器類型從可復位更改為可設置,從而保留了掃描鏈并確保DFT覆蓋率不受影響。

圖6

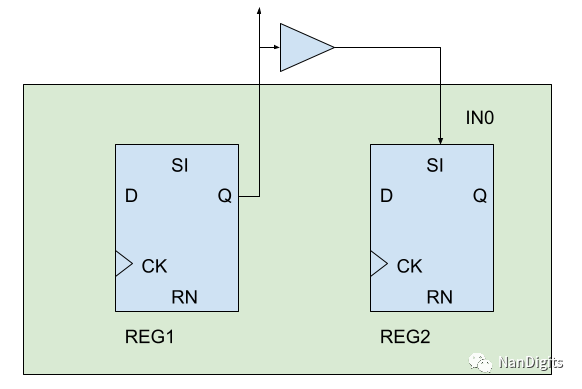

Cadence Conformal ECO中常見的一個錯誤是 "Error: Duplicate fanout branch # for net 'IN#'"。

這個問題通常出現在一個場景中,其中一個寄存器(REG1)的Q輸出連接到父級,而相同的輸出也連接到另一個寄存器(REG2)的掃描輸入(SI)引腳。當對REG1執行ECO(例如將其類型更改為可設置寄存器)時,可能會導致Conformal ECO出現錯誤,從而可能導致工具停止操作。

圖7

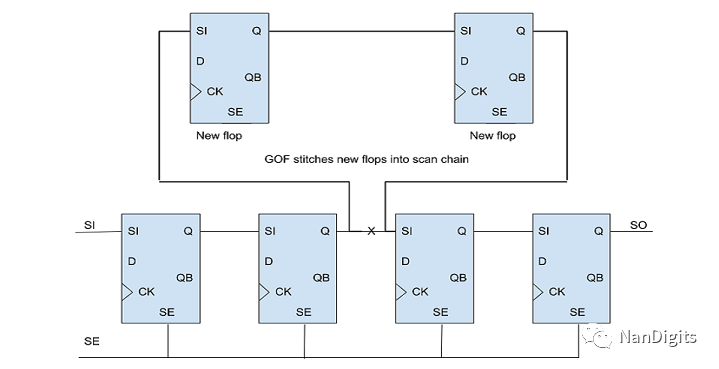

四、將新的寄存器插入掃描鏈中

ECO中插入的新寄存器應該被縫合到現有的掃描鏈中,以避免DFT覆蓋率的損失。從工業數據來看,在具有100K個寄存器的設計中,100個新的非掃描寄存器可能會導致超過0.1%的DFT覆蓋率損失。對于像汽車IC這樣的高可靠性芯片,DFT覆蓋率的損失是不可接受的。因此,如果在功能ECO中有新的寄存器,則應重新設計掃描鏈以包括新的寄存器。

圖8

GOF提供了幾種將新寄存器插入掃描鏈的方法。可以使用API "stitch_scan_chain" 自動縫合掃描鏈來插入新寄存器。還可以通過使用多個網表處理API來手動執行。

4.1 自動模式將寄存器插入本地模塊的掃描鏈中

可以使用自動方法將寄存器集成到本地模塊的掃描鏈中。在以下示例腳本中,假設'fix_design'命令添加了名為'state_new_reg_0'到'state_new_reg_7'的8個新寄存器。要將這些寄存器集成到本地模塊的掃描鏈中,請執行以下步驟:

# API stitch_scan_chain without any argument to insert new flops in the local modules

stitch_scan_chain();

4.2 自動模式在一個寄存器之前插入新的寄存器

GOF提供了一種自動方法,可以在指定寄存器實例之前插入新的寄存器。用戶可以標識一個寄存器實例的名稱,然后GOF將在該實例之前將所有新寄存器插入到掃描鏈中。

例如,假設需要將所有新寄存器插入到名稱為'u_pixel_ctrl/pulse_reg'的寄存器實例之前,請執行以下步驟:

# API stitch_scan_chain with -to option

stitch_scan_chain('-to', 'u_pixel_ctrl/pulse_reg');

4.3 手動模式連接所有新寄存器

掃描鏈可以通過ECO APIs手動重新連接,并且可以創建新的掃描輸入/輸出端口。

# GofCall ECO script, run_manual_stitch_scan_chain_example.pl

use strict;

undo_eco; # Discard previous ECO operations

setup_eco("eco_manual_stitch_scan_chain_example");# Setup ECO name

read_library("art.5nm.lib"); # 讀lib庫

read_svf("-ref", "reference.svf.txt"); # 可選讀入svf

read_svf("-imp", "implementation.svf.txt"); # 可選讀入svf

read_design("-ref", "reference.gv"); # 讀參考網表

read_design("-imp", "implementation.gv"); # 讀實現網表,ECO目標

set_top("topmod"); # 設置頂層名字

set_ignore_output("scan_out*");

set_pin_constant("scan_enable", 0);

set_pin_constant("scan_mode", 0);

fix_design;

save_session("current_eco_name"); # Save a session for future restoration

set_error_out(0); # Don't exit if finds error

my @flops = get_cells("-hier", "-nonscan"); # Find all new flops that are not in scan chain yet

# @flops can be defined by reading a list file

if(scalar(@flops)){ # If there are new flops, start the work

new_port("so1", "-output"); # New a scan out port so1

new_port("si1", "-input"); # New a scan in port si1

my $cnt = 0;

my $now_si;

foreach my $flop (@flops){

$cnt++;

if(is_scan_flop($flop)==0){

my $flop_name = get_ref($flop);

my $scanflop = get_scan_flop($flop_name); # If the flop is not scan type, change to scan type flop

change_gate($flop, $scanflop);

}

if($cnt==1){

change_port("so1", "$flop/Q"); # The first flop drives the new scan out port

}else{

change_pin($now_si, "$flop/Q");

}

$now_si = "$flop/SI";

change_pin("$flop/SE", "te"); # All scan enable pin is connected to scan enable signal

}

change_pin($now_si, "si1"); # The last flop has the new scan in port driving SI pin

}

write_verilog("eco_verilog.v");# Write out ECO result in Verilog

exit;

五、結論

總之,DFT友好的ECO是電子設計自動化(EDA)流程中非常理想的解決方案,因為它比傳統方法提供了多種好處。其中最顯著的優點之一是能夠確保生成的設計是DFT友好的,這簡化了測試和驗證過程。在現代復雜集成電路的時代,確保DFT兼容性對于有效和可靠的測試至關重要。

DFT友好的ECO的一個關鍵特征是它能夠在優化改變設計功能的情況下不影響可測試性。這是通過考慮設計的特定DFT要求的先進算法和方法實現的。相比之下,傳統的EDA流程可能不會為DFT進行優化,從而導致測試和驗證方面的重大挑戰。

此外,使用DFT友好的ECO可以在市場上提供競爭優勢。這是因為它可以實現更快的上市時間,減少設計迭代,并提高整體產品質量。相比之下,沒有使用DFT友好方法的競爭對手可能難以實現類似的結果,導致延遲、成本增加和產品競爭力降低。

總的來說,DFT友好的ECO是現代EDA流程的一種非常有效的解決方案,比傳統方法提供了重要的優勢。它優化設計以實現DFT兼容性,可以實現更快的上市時間、減少設計迭代并提高產品質量,從而在市場上提供競爭優勢。

-

芯片

+關注

關注

455文章

50714瀏覽量

423152 -

寄存器

+關注

關注

31文章

5336瀏覽量

120230 -

DFT

+關注

關注

2文章

231瀏覽量

22713 -

ECO

+關注

關注

0文章

52瀏覽量

14885

發布評論請先 登錄

相關推薦

V6 FPGA可以ECO功能嗎?

什么是DFT,DFT是什么意思

汽車eco模式使用技巧_eco模式真能省油嗎

DFT基本原理解析

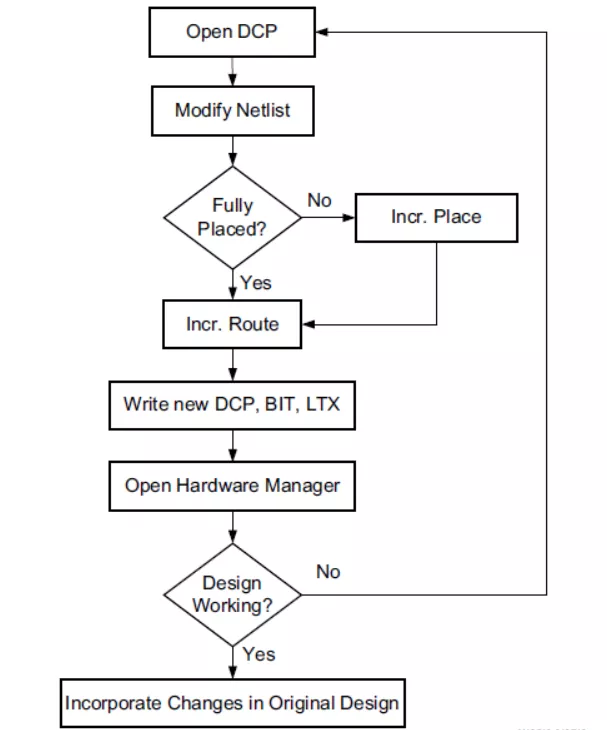

詳解Xilinx FPGA的ECO功能

一個典型設計的DFT組件

NanDigits GOF提供一種快速DFT DRC檢查的功能

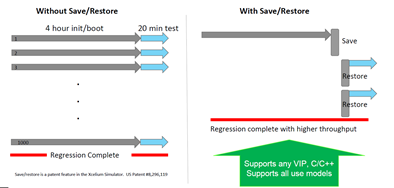

Lightelligence使用Cadence Xcelium多核加速DFT仿真

解析什么是DFT友好的功能ECO?

解析什么是DFT友好的功能ECO?

評論