本篇是Xilinx已發布的《Vivado使用誤區與進階》系列:在Vivado中實現ECO功能。

關于Tcl在Vivado中的應用文章從Tcl的基本語法和在Vivado中的應用展開,繼上篇《用Tcl定制Vivado設計實現流程》介紹了如何擴展甚至是定制FPGA設計實現流程后,引出了一個更細節的應用場景:如何利用Tcl在已完成布局布線的設計上對網表或是布局布線進行局部編輯,從而在最短時間內,以最小的代價完成個別的設計改動需求。

什么是ECO?

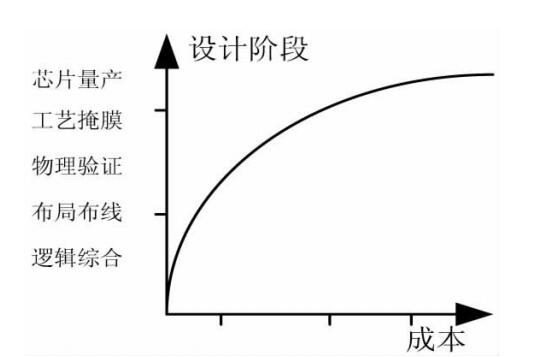

ECO指的是Engineering Change Order,即工程變更指令。目的是為了在設計的后期,快速靈活地做小范圍修改,從而盡可能的保持已經驗證的功能和時序。ECO的叫法算是從IC設計領域繼承而來,其應用在FPGA設計上尚屬首次,但這種做法其實在以往的FPGA設計上已被廣泛采用。簡單來說,ECO便相當于ISE上的FPGA Editor。

但與FPGA Editor不同,Vivado中的ECO并不是一個獨立的界面或是一些特定的命令,要實現不同的ECO功能需要使用不同的方式。

ECO的應用場景和實現流程

ECO的應用場景主要包含:修改cell屬性、增減或移動cell、手動局部布線。還有一些需要多種操作配合的復雜場景,例如把RAM(或DSP)的輸出寄存器放入/拉出RAMB(或DSP48)內部,或是把設計內部信號接到I/O上作調試probe用等等。

針對不同的應用場景,Vivado中支持的ECO實現方式也略有區別。有些可以用圖形界面實現,有些則只能使用Tcl命令。但通常可以在圖形化界面上實現的操作,都可以改用一條或數條Tcl命令來實現。

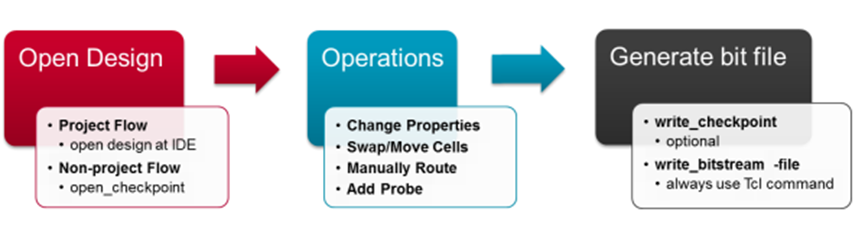

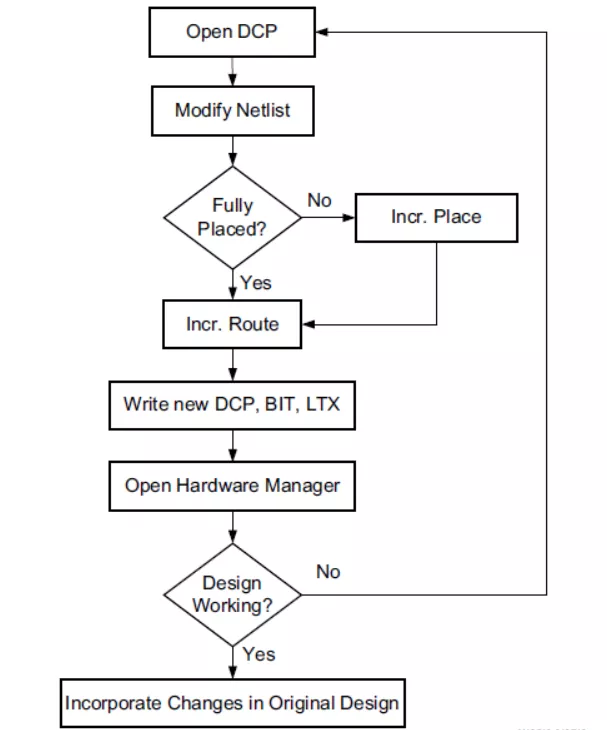

ECO的實現流程如下圖所示:

第一步所指的Design通常是完全布局布線后的設計,如果是在工程模式下,可以直接在IDE中打開實現后的設計,若是僅有DCP文件,不論是工程模式或是非工程模式產生的DCP,都可以用open_checkpoint命令打開。

第二步就是ECO的意義所在,我們在布局布線后的設計上進行各種操作,然后僅對改動的部分進行局部布局/布線而無需整體重跑設計,節約大量時間的同時也不會破壞已經收斂的時序。

第三步就是產生可供下載的bit文件了,此時必須在Tcl Console中或是Tcl模式下直接輸入命令產生bit文件,而不能使用IDE上的“Generate Bitstream”按鈕。原因是后者讀到的還是ECO前已經完成布局布線的原始設計,生成的bit文件自然也無法使用。

修改屬性

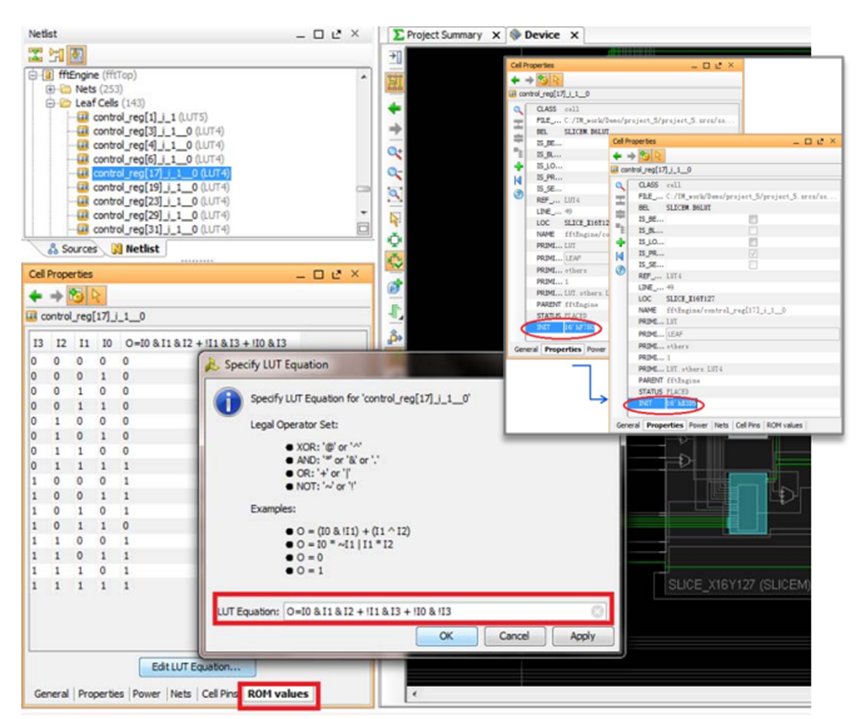

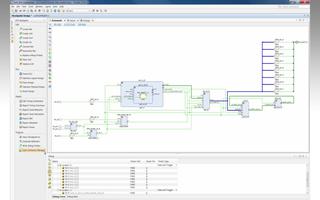

絕大部分的屬性修改都能通過IDE界面完成,如下圖所示。

比如要修改寄存器的初值INIT或是LUT的真值表,用戶只需在Vivado IDE中打開布局布線后的設計(Implemented Design),在Device View中找到并選中這個FF/LUT,接著在其左側的Cell Properties視圖中選擇需要修改的屬性,直接修改即可。

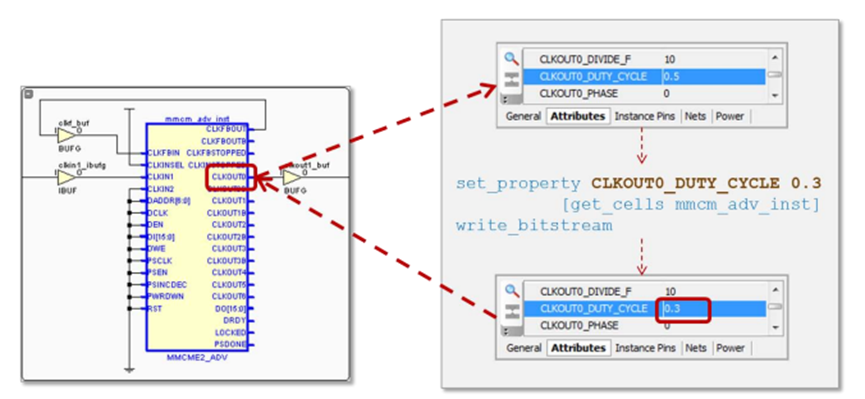

除了對FF/LUT的操作外,很多時候我們需要對MMCM/PLL輸出時鐘的相移進行修改。對于這種應用,用戶也無需重新產生MMCM/PLL,與上述方法類似,可以在布局布線后的Device View上直接修改。

移動/交換cells

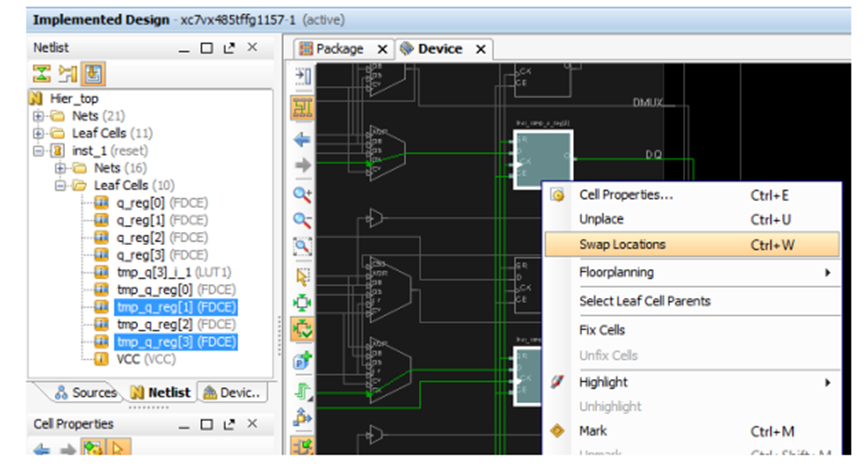

移動/交換cells是對FF/LUT進行的ECO操作中最基本的一個場景,目前也只有這種情況可以通過圖形化實現。如要刪減cells等則只能通過Tcl命令來進行。

具體操作方法也相當簡便,要互換cells位置的情況下,只要在Device View上選中需要的那兩個cells,如上圖所示的兩個FFs,然后右鍵調出菜單,選擇Swap Locations即可。若要移動cells則更簡單,直接在圖中選中FF拖移到新的位置即可。

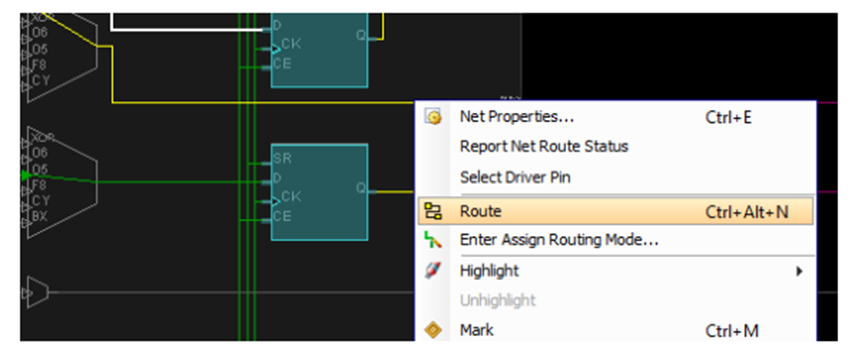

當用戶移動或改變了cells的位置后會發現與其連接的nets變成了黃色高亮顯示,表示這些nets需要重新布線。這時候需要做的就是在圖中選中這些nets然后右鍵調出菜單,選擇Route進行局部布線。

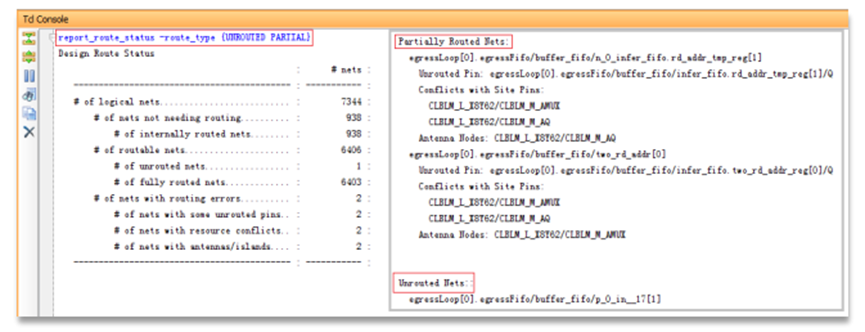

局部布線后一定要記得在Tcl Console中使用report_route_status命令檢查布線情況,確保沒有未完成布線(unrouted)或是部分未完成布線(partial routed)的nets存在。給這個命令加上選項則可以報告出更細致的結果,如下圖所示。

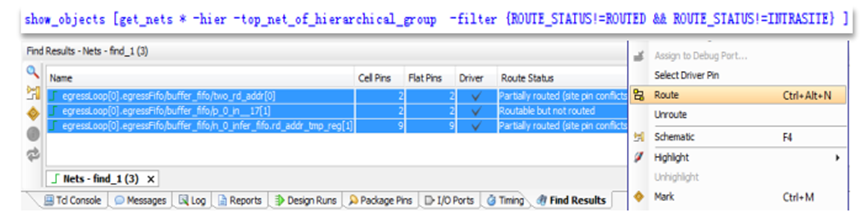

如果換個稍復雜些的Tcl命令配合圖形化顯示,更加直觀的同時,也可以方便右鍵調出命令進行針對性的局部布線。

手動布線

手動布線是一種非常規的布線方式,一次只能針對一根net在圖形化界面下進行。所謂手動布線,除了完全手動一個節點一個節點的選擇外,也支持工具自動選擇資源來布線。通常我們并不建議全手動的方式,Vivado是時序驅動的工具,所以其自動選擇的布線結果已經是遵循了時序約束下的最佳選擇。

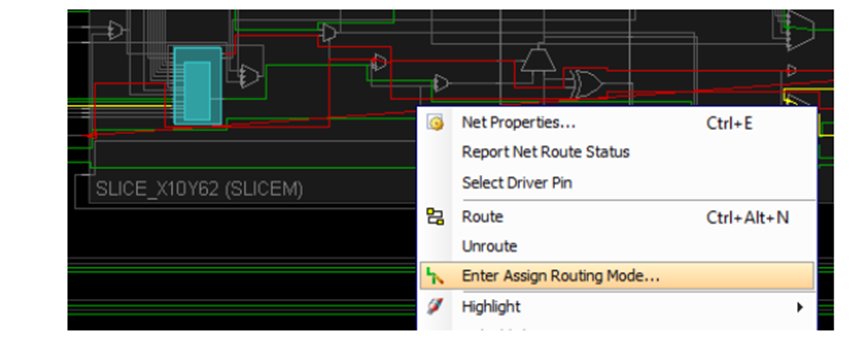

在Device View中選擇一根沒有布線或是預先Unroute過的net(顯示為紅色高亮),右鍵調出菜單并選擇Enter Assign Routing Mode…便可進入手動布線模式。

復雜的ECO場景

篇幅過半,一直在鋪墊,其實最有實踐意義的ECO還沒提到。相信大部分用戶最懷念FPGA Editor中的一個功能就是probe了,如何快速地把一根內部信號連接到FPGA管腳上,無需重新布局布線,直接更新bit文件后下載調試。曾經數次被客戶問及,很多人還為Vivado中不支持這樣的做法而深表遺憾。

其實這樣類似的功能在Vivado中一直支持,唯一的問題是暫時還沒有圖形化界面可以一鍵操作(相關開發工作已經在進行中)。但受益于Tcl的靈活多變,我們可以更有針對性地實現probe功能,效率也更高。

Tcl操作命令

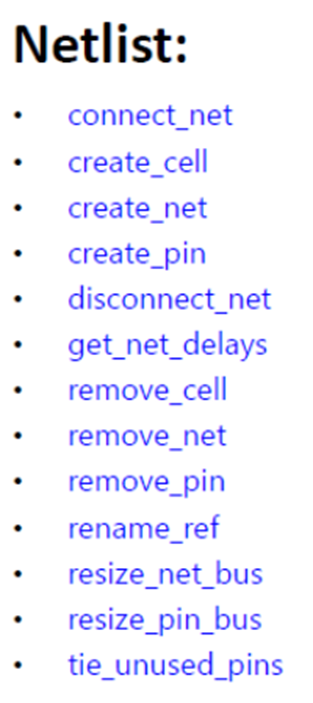

在UG835中把Vivado支持的Tcl命令按照Category分類,這些列于Netlist目錄下的命令就是實現ECO需要用到的那些。

通常涉及到增減cells的ECO基本分為三步實現:首先用create_cell / create_net等創建相關cell和/或net,然后用disconnect_net / connect_net等命令修正因為cell和net的改動而影響到的連接關系,最后用route_design加選項完成局部布線。

不同的Vivado版本對此類ECO修改有稍許不同的限制,例如在2014.1之后的版本上,需要在改變cell的連接關系前先用unplace_cell將cell從當前的布局位置上釋放,在完成新的連接關系后,再用place_cell放到新的布局位置上。

具體操作上可以根據Vivado的提示或報錯信息來改動具體的Tcl命令,但操作思路和可用的命令相差無幾。

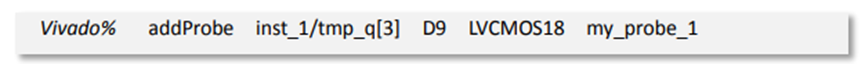

Add Probe

這是一個在Vivaod上實現probe功能的Tcl腳本,已經寫成了proc子程序,簡單易懂。可以直接調用,也可以做成Vivado的嵌入式擴展命令。調用其生成probe只需先source這個腳本,然后按照如下所示在Tcl Console中輸入命令即可。

該腳本已經在Vivado2014.3和2014.4上測試過,一次只能完成一個probe的添加,而且必須按照上述順序輸入信號名,管腳位置,電平標準和probe名。因為不具備預檢功能,可能會碰到一些報錯信息而導致無法繼續。例如選擇的信號是只存在于SLICE內部的INTRASITE時,則無法拉出到管腳。再比如輸入命令時拼錯了電平標準等,也會造成Tcl已經部分修改Vivado數據庫而無法繼續的問題。此時只能關閉已經打開的DCP并選擇不保存而重新來過。

ECO在Vivado上的發展

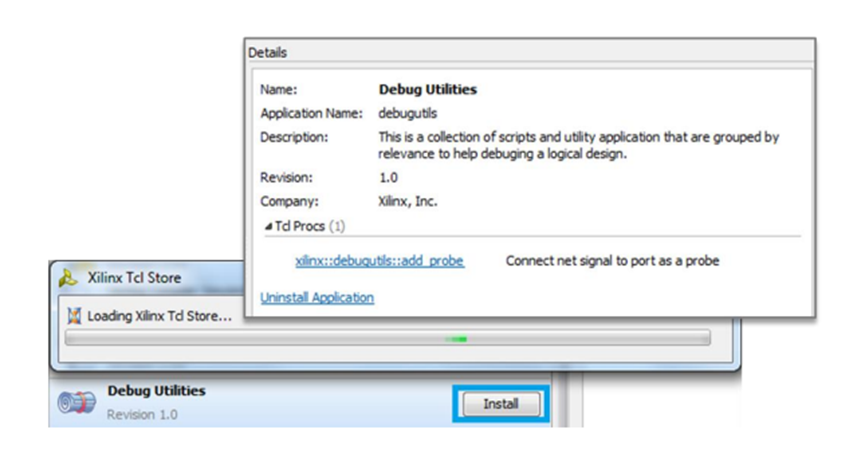

經過了兩年多的發展,在Vivado上實現ECO已經有了多種方式,除了前面提到的圖形化上那些可用的技巧,還有用戶自定義的Tcl命令和腳本等。隨著Xilinx Tcl Store的推出,用戶可以像在App Store中下載使用app一樣下載使用Tcl腳本,簡化了Tcl在Vivado上應用的同時,進一步擴展了Tcl的深入、精細化使用,其中就包括Tcl在ECO上的應用。

目前Vivado 2014.4版本上新增了很多有用的腳本。安裝好Vivado后,只需打開Tcl Store,找到Debug Utilities,點擊Install稍等片刻,即可看到一個add_probe的Tcl proc被安裝到了你的Vivado中。

這個add_probe是在上述addProbe例子的基礎上擴展而來,不僅可以新增probe,而且可以改變現有probe連接的信號。此外,這個腳本采用了argument寫法,點擊程序可以看help,所以不一定要按照順序輸入信號、電平標準等選項,輸錯也沒有問題。另外增加了預檢和糾錯功能,碰到問題會報錯退出而不會改變Vivado數據庫,效率更高。

此外,Tcl Store上還有很多其它好用的腳本,歡迎大家試用并反饋給我們寶貴意見。雖然里面關于ECO的腳本還很少,但我們一直在補充。此外Tcl Store是一個基于GitHub的完全開源的環境,當然也歡迎大家上傳自己手中有用的Tcl腳本,對其進行補充。

總體來說,ECO是一個比較大的命題,因為牽扯到的改動需求太多,其實也很難限制在一個GUI界面中實現。這篇文章的目的就是為了讓大家對在FPGA上實現ECO有個基本的認識,梳理看似復雜無序的流程,所謂觀一葉而知秋,窺一斑而見全豹,希望能帶給更多用戶信心,用好Vivado其實一點都不難。

審核編輯:湯梓紅

-

FPGA

+關注

關注

1643文章

21946瀏覽量

613599 -

IC設計

+關注

關注

38文章

1345瀏覽量

105181 -

Xilinx

+關注

關注

73文章

2181瀏覽量

124243 -

ECO

+關注

關注

0文章

52瀏覽量

15104 -

Vivado

+關注

關注

19文章

828瀏覽量

68143

原文標題:在 Vivado 中實現 ECO 功能

文章出處:【微信號:HXSLH1010101010,微信公眾號:FPGA技術江湖】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

在vivado中是否有像Logic Lock這樣的功能

Tcl在Vivado中的基礎應用

Vivado使用誤區與進階——在Vivado中實現ECO功能

Vivado Design Suite 2015.3的新功能介紹

Vivado Design Suite 2018.1設計套件中的新增功能介紹

一起體驗Vivado 的ECO流程

帶大家一起體驗一下Vivado的ECO流程

ECO技術在SoC芯片設計中的應用

在Vitis中把Settings信息傳遞到底層的Vivado

詳解Xilinx FPGA的ECO功能

評論