IP庫簡介

一直想做一個可以供大家學習、使用的開源IP庫,類似OpenCores,OC上IP在領域內的IP很少,通用性強一點,所以作為OC的“補充”,所以做了一個開源IP庫,側重點在領域的IP輔以工程或者仿真驗證,一個人能力有限,歡迎大家能夠共同構建,有什么問題可以在網頁郵箱批評指正,謝謝~

FPGA 上的跳頻無線電

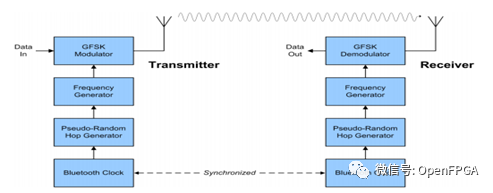

列表中的第一個 FPGA 項目是一個標準擴頻系統,屬于“direct sequence”或“frequency hopping”類型,或者是這兩種“混合”類型的某種組合。在跳頻中,系統在很寬的頻帶上從一個頻率“跳”到另一個頻率。頻率參與的模式是代碼序列的作用,從一個頻率跳到另一個頻率的速率是數據速率的函數。

該項目旨在 FPGA 上設計、仿真和開發用于跳頻系統的發射器和接收器。該項目的完成涵蓋了安全數字通信的藝術,現在正被用于商業、工業和軍事目的。

該設計包括以下模塊;PN sequence block; serial to parallel converter; random input block; frequency synthesizer; mixer block。

圖1:無線電架構

FPGA 上的數字視頻縮放

此IP具有以下特點:

AXI STREAM接口;

支持向上或者向下縮放;

輸入支持RGB或者YYCbCr 444;

允許獨立的水平和垂直縮放,可以生成任何分辨率或者長寬比;

內具18個相位的7×7 FIR多相濾波器來提高視頻質量;

支持2K及以上視頻;

無需進行幀緩沖;

雙線性和最近鄰調整大小模式。

Canny 邊緣檢測是一種用于視覺處理的多階段算法,用于復雜視覺算法(例如車牌識別)的邊緣處理。Canny 邊緣檢測可以消除不相關的圖像信息,并為每個像素提供清晰的輸出。高性能計算傳統上是通過 Canny 邊緣檢測來實現的。但是,現在可以在嵌入式平臺上為低功耗移動應用程序實施視覺算法。

多個處理階段包括 Canny 等視覺算法。通常,處理器必須從外部存儲器獲取、處理輸入圖像幀并將其寫回外部存儲器。對于下一個處理塊,處理器重復這個過程。這種傳統的塊間內存洗牌效率低下:在這個 FPGA 項目中,我們已經實現了帶有 9×9 算子的 Canny 邊緣檢測器。能夠在每個時鐘周期產生 1 個像素。我們已經在高達 400Mhz 時鐘頻率的 Virte系列FPGA上成功實現。該項目的目的是檢測圖像中的銳利邊緣。

直接數字頻率合成器

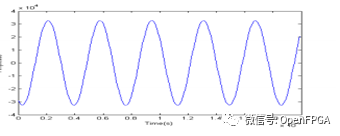

直接數字合成 (DDS) 通過生成數字時變信號然后進行數模轉換來生成模擬波形,通常是正弦波。由于 DDS 系統內部的操作主要是數字操作,因此它可以提供輸出頻率之間的快速切換、令人滿意的頻率分辨率以及在寬頻率范圍內的操作。設計人員可以使用多種頻率生成:從基于鎖相環 (PLL) 的甚高頻合成技術到動態數模轉換器 (DAC) 輸出編程,以產生較低頻率的任意波形。但在通信和工業應用中,DDS 方法正在迅速獲得解決頻率(或波形)生成要求的認可,因為單芯片 IC 器件只能產生具有高分辨率和準確性的可編程模擬輸出波形。

在這個 FPGA 項目中,我們實現了用于數字上/下轉換和周期波形生成的高精度直接數字頻率合成器 (DDFS)。例如,正弦波、余弦波、方波和鋸齒波。輸出是 16 位帶符號數據樣本。該項目非常適合正交信號生成、數字調制/解調和軟件無線電應用。此外,它還可以用作振蕩器和生成復雜的正交信號。以及周期性波形的產生。例如,正弦波、余弦波、方波和鋸齒波。輸出是 16 位帶符號數據樣本。

該項目非常適合正交信號生成、數字調制/解調和軟件無線電應用。此外,它還可以用作振蕩器和生成復雜的正交信號。以及周期性波形的產生。例如,正弦波、余弦波、方波和鋸齒波。輸出是 16 位帶符號數據樣本。該項目非常適合正交信號生成、數字調制/解調和軟件無線電應用。此外,它還可以用作振蕩器和生成復雜的正交信號。

圖4:正弦波

優化區塊鏈系統的哈希算法

加密哈希函數是一種哈希算法。它是一種將任意大小的信息映射到固定大小的哈希的數學算法。在 IT 中,加密哈希函數是很常用的。我們可以將它們用于數字簽名、消息的身份驗證碼 (MAC) 和其他驗證類型。我們還可以將它們用于哈希表中的索引數據、指紋識別、文件識別、檢測重復項或用作校驗和(我們可以感知發送的文件是否發生了意外或故意的數據損壞)。哈希函數的算法被設計為一種不可逆的單向函數。然而,近年來有多種哈希算法被破壞。該 FPGA 項目旨在提供哈希算法的 FPGA 實現,以生成工作量證明 (Pow) 的哈希值。在這個項目中,開發了區塊鏈系統來挖掘0x比特幣。我們使用了CVP 13 FPGA板,并在其上實現了Keccak-256算法。我們已經實現了每秒500千兆的哈希值。

雷達信號處理器在FPGA上的實現

用于機載降水回波信號處理的高性能數字電子電路——已開發出商用領域的雷達測量設備——可編程門陣列(FPGA)。以前,將雷達回波數據下行到后處理地面站是一種常見的做法,這是一種昂貴的做法,消除了近實時使用自動瞄準數據的可能性。理論上,一個由大約20個個人計算機類型的微處理器組成的系統可以執行機載處理;與這樣的系統相比,當前基于 FPGA 的處理器體積小得多,功耗也低得多。或者,專用集成電路 (ASIC) 可用于板載處理。然而,與 ASIC 實現相比,當前的 FPGA 實現具有以下優勢:(1) 研究應用程序具有更大的通用性,例如當前的應用程序;(2) 在研究應用程序典型的有限生產量中成本更低。在 FPGA 上實現雷達信號處理技術是重要的領域。在這個FPGA項目中,我們選擇了FPGA中的幾個算法實現雷達方程以及脈沖壓縮算法,實現多普勒頻移以檢測目標速度,并實現脈沖多普勒波形。

在FPGA上實現了一種恒虛警率(CFAR)檢測自適應算法,用于雷達系統在噪聲、雜波和干擾的背景下檢測目標信號。該項目的目的是從噪聲條件下檢測目標。

FPGA 上的快速傅立葉變換 (FFT)

快速傅里葉變換 (FFT) 是 DSP 系統中使用的基本構建塊,其應用范圍從基于 OFDM 的數字調制解調器到超聲波、雷達和 CT 圖像重建的算法。盡管它的算法簡單易懂,但對于當今的工程師來說,實現架構和細節的變體是必不可少的,并且是一個巨大的時間消耗。在這個FPGA項目中,我們在FPGA上實現了快速傅里葉變換;我們已經使用蝶形技術在FPGA上實現了它。FFT用于在復雜信號計劃中執行頻率分量的查找。這是一個4096點的FFT。通過設備級固定點C模型,該FFT項目核心提供了四種不同的架構,并將平均實現時間從3-6個月縮短到按下一個按鈕。它還為用戶提供了對DSP算法和硬件工程師所需的所有適當算法和實現進行復雜權衡的機會。FFT項目強調增加動態范圍,將數據和相位因子寬度的支持增加到34位,并支持IEEE單精度浮點數據形式。通過在內部使用更高精度的定點FFT,實現可比的噪聲效率。

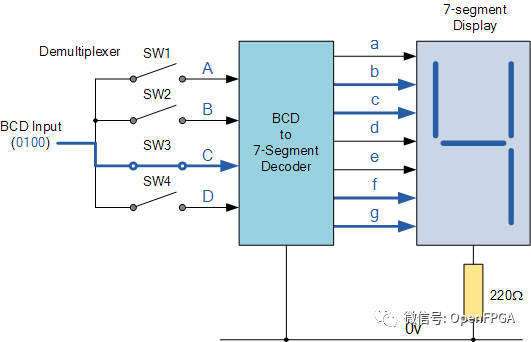

在 FPGA 上將 BCD 碼轉換為 7 段碼

數字解碼器 IC 是一種將一種數字格式轉換為另一種數字格式的設備,二進制編碼的十進制 (BCD) 到 7 段顯示解碼器是執行此操作最廣泛使用的設備之一。7 段 LED(發光二極管)或 LCD(液晶顯示器)式顯示器為數字、字母甚至字母數字字符提供了一種非常方便的方式來顯示信息或數字數據。通常,7 段顯示器由七個不同顏色的 LED(稱為段)組成。LED 段的正確組合需要在顯示屏上點亮,以生成從 0 到 9 和 A 到 F 的必要數字或十六進制字符,相應地,BCD 到 7 段顯示解碼器 74LS47 就是這樣做的。

圖5:BCD 轉七段顯示

FPGA 上的數字時鐘

數字時鐘的主要用途是使用 Artix-7 FPGA 板上的 7 段面板以數字方式顯示時間。默認情況下,數字時鐘顯示運行時間,可以使用分配給板載開關的時間設置來調整時間。警報角色也使用警報集和套件開關上的警報進行配置。開發的數字時鐘是為 24 時鐘設計的格式。對于數字時鐘的硬件實現,本項目采用FPGA。一旦 FPGA 打開,時鐘就會開始。FPGA 和板載時鐘將產生時序信號。可以使用板上的撥碼開關設置時鐘時間和鬧鐘時間。使用數字運算:計數、比較、遞增和遞減,改進了建議的數字時鐘設計。使用時間設置開關,可以設置時鐘時間,可以使用鬧鐘設置開關設置鬧鐘時間。如果時鐘等于鬧鐘時間,鬧鐘就會響起。通過使用顯示器上的按鈕,可以增加和減少分鐘和小時。在這個 FPGA 項目中,我們在 FPGA 上實現了數字時鐘。該模塊有一個輸入“FPGA 的源時鐘”,有 3 個輸出(時針、分針和秒針)。

FPGA 上的 JPEG 硬件壓縮器

壓縮圖像可以通過在不顯著降低圖像存儲和傳輸圖像質量的情況下最大限度地減少成本和時間來提高設備效率。可以在圖像元素(像素)的矩陣上描述每個像素的單色圖像,由8位的灰度值描述。圖像數據的這種描述可能需要大量存儲需求。圖像壓縮旨在減小圖像的大小,同時保留大部分細節。它可以是有損壓縮,也可以是無損壓縮。與無損壓縮相比,有損在數據量上有更高的壓縮比;而只是初始壓縮的近似值,可以重新創建圖像。圖像壓縮有很多規范,例如聯合圖像專家解壓縮 (CODEC) 團隊、圖形交換格式 (GIF)、便攜式網絡圖形 (PNG)、文件圖片標簽格式 (TIFF)。最常用的 JPEG 壓縮方式,使用并基于余弦離散變換 (DCT) 的有損圖像壓縮類型。根據在圖像和圖像中發現的細節,JPEG 格式的壓縮圖像的壓縮效率可能約為原始大小的 10%。結果是所需帶寬減少了 90%。這個 FPGA 項目包括一個完整的 JPEG 硬件,具有 41 子采樣,能夠以最大分辨率(256×256 @ 60 MHz)以每秒高達 42 張圖像的速率進行壓縮,并將壓縮的JPEG圖像輸出到存儲器。。

FPGA 上的 FM 接收器

我們在 FPGA 上構建了一個簡單的 FM 接收器,用于解調 FM 調制頻率信號。我們使用偶極天線接收 FM 信號,然后使用 FM 解調器邏輯解調接收到的信號。首先,我們使用ADC將模擬FM信號轉換為數字信號,然后對其進行數字處理以去除載波,從而獲得來自廣播電臺的唯一純聲波。

FPGA 上的平方根

在物理學中,平方根函數sqrt(x)是一個重要的基本函數——數字信號和圖像處理,ANN方程。現場可編程門陣列(FPGA)目前正在擴展以解決這個問題。需要計算函數sqrt(x)的問題。FPGA制造商和第三方公司正在提出sqrt計算(x)的各種IP核心。但這些IP核心是幾十年前開發的,通常沒有考慮到最新一代FPGA的特性。因此,它們確實需要升級。在這個FPGA項目中,提出了一種計算sqrt(x)的增強特征算法,它適合FPGA的實現。已經在FPGA上編寫了一個代碼來尋找有符號數的平方根。該代碼基于“非恢復平方根算法”。該代碼采用一個32位大小的有符號數字,并返回平方根,平方根也是16位大小的帶符號類型。提出了一種類似CORDIC的改進算法,用于推導平方根方程。該算法由與給定數據成比例的減少的步數之和分開,結果是位寬。

FPGA 錯誤檢測-CRC

錯誤檢測決定了通過介質獲得的數據在傳輸時是否損壞。為實現這一點,發射器使用一種功能來測量原始數據幀的數據校驗和并附加校驗和值。為了為接收到的數據幀創建校驗和,接收器使用相同的計算技術并將接收到的校驗和與傳輸的校驗和進行比較。如果兩個校驗和值相同,則得到的數據幀是正確的,在傳輸或存儲過程中沒有數據損壞。在這個 FPGA 項目中,在這個FPGA項目中,我們在FPGA上開發了CRC來檢測傳輸消息中的錯誤。所生成的CRC電路的優點是假定輸入被串行饋送到電路中。這意味著,輸入可能很長,并且FPGA資源的使用仍然保持不變。

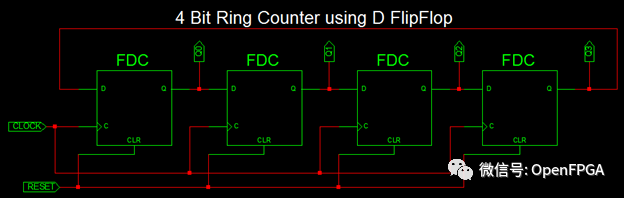

FPGA 上的環形計數器

環形計數器是一種由連接到移位寄存器的觸發器組成的計數器,最后一個觸發器的輸出饋送到第一個觸發器的輸入,形成“循環”或“環形”結構。在硬件設計(例如,ASIC 和FPGA 設計)中,環形計數器也用于構造有限狀態機。二進制計數器將需要一個比環形計數器復雜得多的加法器電路,并且隨著位數的增加具有更顯著的傳播延遲,而無論代碼的位數如何,環形計數器的傳播延遲幾乎都是恒定的。在這個FPGA項目中,在FPGA上實現了一個環形計數器,由一系列正連接的觸發器組成。該電路是一種特殊類型的移位寄存器,其中最后一個觸發器的輸出被反饋到第一個觸發器輸入。

圖6:FPGA 上的環形計數器

基于 AES 的加密處理器的 FPGA 實現

對數據安全的需求增加是不可否認的事實。為了實現更高的安全性,加密算法在保護數據免遭未經批準的使用方面發揮著至關重要的作用。在這個 FPGA 項目中,我們展示了一個使用高級加密標準 (AES) 的加密處理器。AES 集成了一個 32 位通用 5 級流水線 MIPS 處理器。集成的AES模塊是一個全流水線模塊,遵循內圓和外圓流水線設計。結果表明,所呈現的 AES 算法流水線版本和 MIPS 處理器優于傳統方法。在 553 MHz 的工作頻率下,所提出的設計可以實現 58 Gbps 的吞吐量、240 ns 的延遲和 76 MW 的功耗。

設計是這樣實現的,即使加密協處理器同時運行,加密指令也不會阻塞處理器的指令獲取周期。默認情況下,如果指令是為處理器設計的,則每條指令都從指令內存單元中取出并在 MIPS 處理器上完成其所有周期。然而,如果獲取指令不是MIPS指令,它將在解碼階段后的下一個時鐘周期被發送到密碼協處理器。我們將加密協處理器與 MIPS 合并并進行這種集成,以便加密協處理器由 MIPS 運行而不會干擾流水線階段。

審核編輯:劉清

-

FPGA設計

+關注

關注

9文章

428瀏覽量

26512 -

接收器

+關注

關注

14文章

2468瀏覽量

71875 -

FIR

+關注

關注

4文章

146瀏覽量

33155 -

RGB

+關注

關注

4文章

798瀏覽量

58461 -

多相濾波器

+關注

關注

0文章

6瀏覽量

7309

原文標題:IP庫新增10多個功能IP

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

新增加和更新下面的ASIC IP cores

IP核簡介

IP核簡介

Ethernet/IP(EIP)簡介

IP地址及性能操作

IP over WDM原理簡介

Nimu如何修改成支持多個MAC IP

IP庫新增10多個功能IP簡介

IP庫新增10多個功能IP簡介

評論