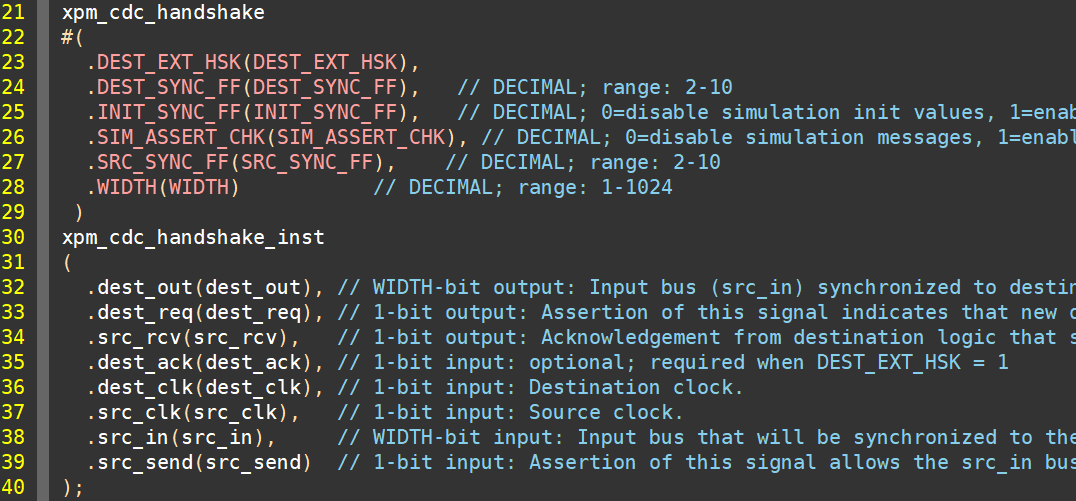

對于多位寬數(shù)據(jù),我們可以采用握手方式實(shí)現(xiàn)跨時鐘域操作。該方式可直接使用xpm_cdc_handshake實(shí)現(xiàn),如下圖所示。xpm_cdc_handshake提供了6個參數(shù)。

其中DEST_EXT_HSK用于決定握手信號是內(nèi)部生成還是來自于該模塊的外部;DEST_SYNC_FF決定了目的端控制信號對應(yīng)的級聯(lián)觸發(fā)器個數(shù);INIT_SYNC_FF決定了仿真時是否使用觸發(fā)器的初始值;SIM_ASSERT_CHK用于判定是否檢查仿真過程中可能的潛在問題;SRC_SYNC_FF決定了源端控制信號對應(yīng)的級聯(lián)觸發(fā)器個數(shù);WIDTH決定了傳輸數(shù)據(jù)的位寬。

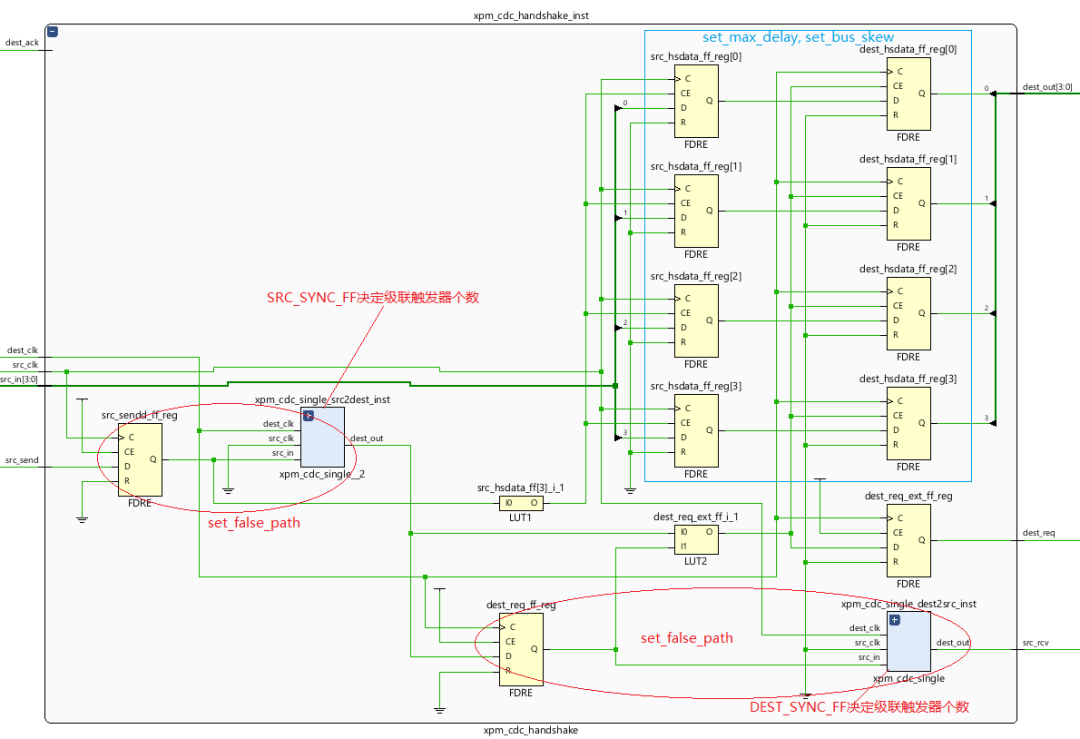

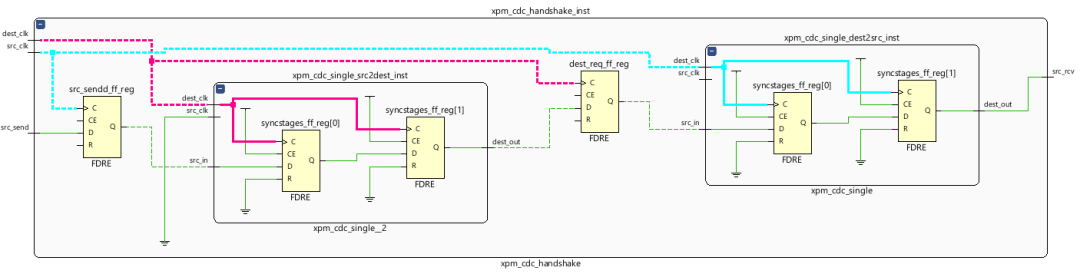

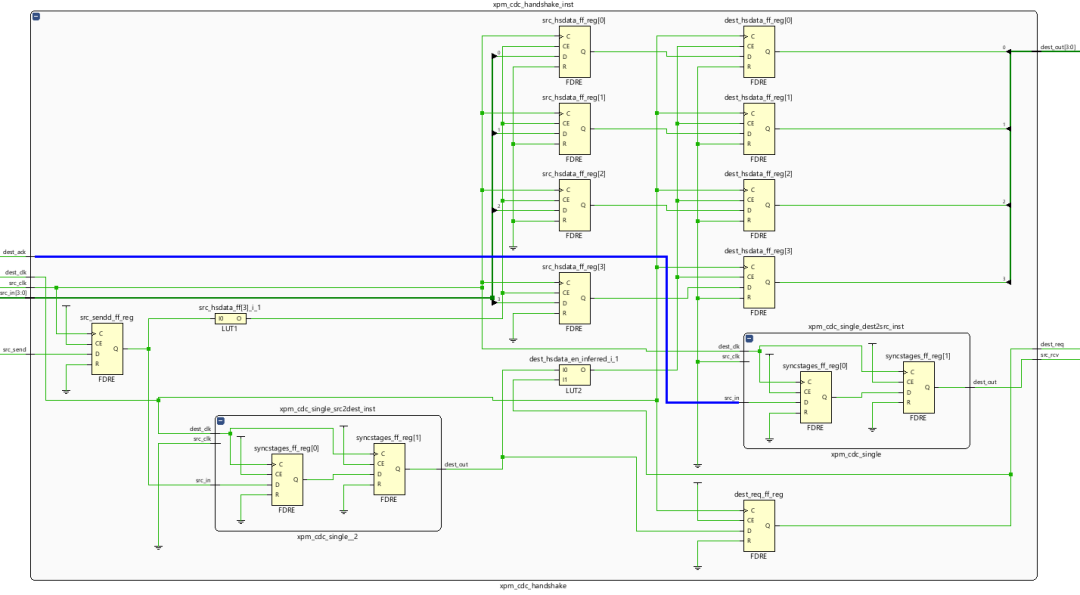

假定DEST_EXT_HSK為0(握手信號由內(nèi)部生成),DEST_SYNC_FF和SRC_SYNC_FF均為2,WIDTH為4,綜合后的電路結(jié)果如下圖所示。可以看到設(shè)計(jì)使用了xpm_cdc_single,用于實(shí)現(xiàn)控制信號src_send的跨時鐘域操作,這也就意味著src_send為高有效時要確保可以被接收端時鐘穩(wěn)定地采樣到至少兩次。

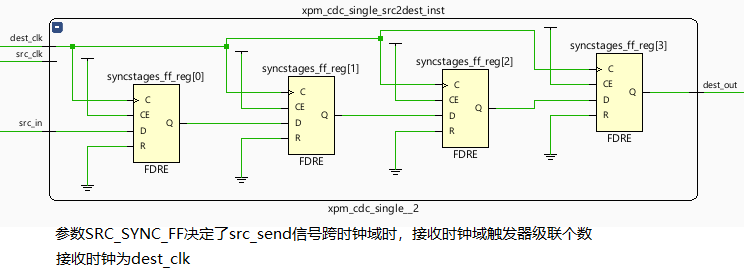

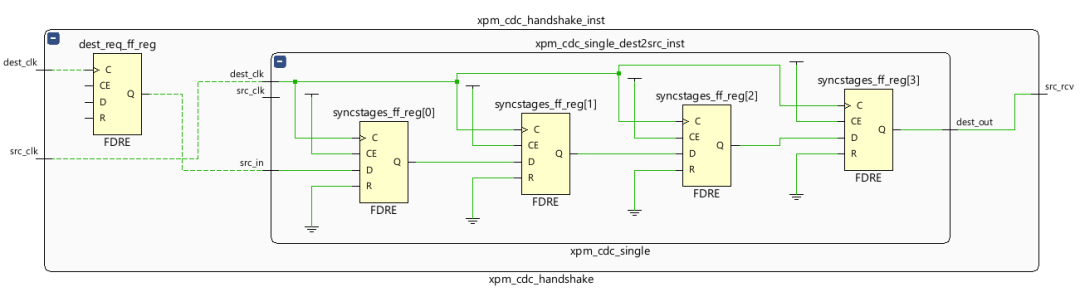

同時也不難理解SRC_SYNC_FF決定了src_send從發(fā)送時鐘域到接收時鐘域所需的級聯(lián)觸發(fā)器個數(shù)。下面第二張圖片就顯示了SRC_SYNC_FF為4時的電路。下面第三章圖顯示了DEST_SYNC_FF為4時的電路。

我們單獨(dú)把控制信號src_send提取出來,看看src_send是如何從發(fā)送時鐘域到接收時鐘域然后又回到發(fā)送時鐘域生成src_rcv信號,如下圖所示。圖中淡紫色為接收時鐘,淺藍(lán)色為發(fā)送時鐘,src_send從輸入到最終產(chǎn)生src_rcv信號共經(jīng)歷了6個觸發(fā)器,兩次跨時鐘域操作。src_send為高時,表明發(fā)送端有待發(fā)送數(shù)據(jù),src_rcv為高時表明接收端已接收到數(shù)據(jù),意味著跨時鐘域操作完成。

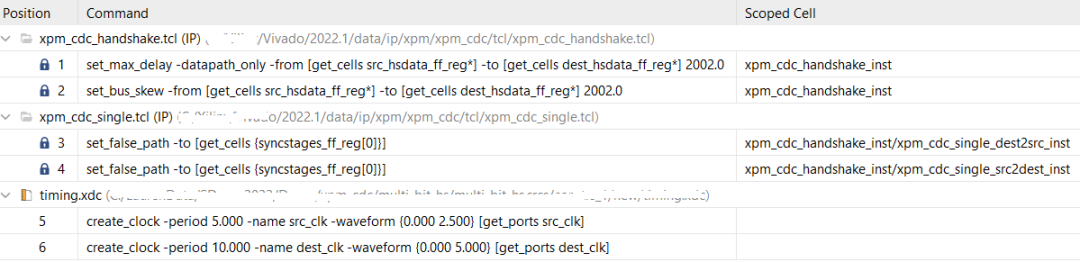

從約束層面看,該模塊使用了set_false_path,set_max_delay和set_bus_skew三種約束,如下圖所示。但其實(shí)set_max_delay和set_bus_skew的延遲值都很大,所以可以認(rèn)為與set_max_delay等效。

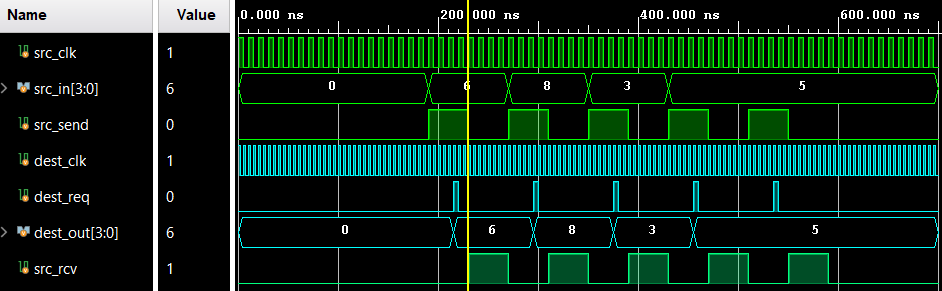

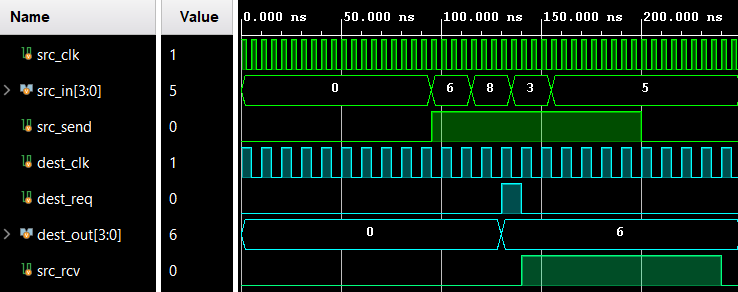

從仿真角度看,我們先看從慢時鐘域到快時鐘域,如下圖所示。這里需要注意的是dest_req輸出脈寬為一個接收時鐘域脈寬,故該信號可用于最終數(shù)據(jù)(跨時鐘域之后)的有效標(biāo)記信號。

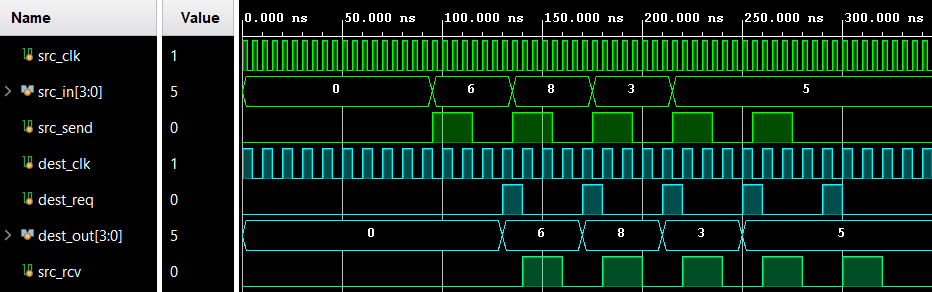

同樣,該模塊也支持從快時鐘域到慢時鐘域的跨時鐘域的操作,如下圖所示。

既然是握手方式,那么就意味著每發(fā)送一個數(shù)據(jù),就要發(fā)送一個與之同步的有效標(biāo)記信號(src_send),當(dāng)接收端接收到該信號時,開始處理,接收完畢發(fā)送src_rcv給發(fā)送端,表明數(shù)據(jù)被接收到。這樣看來,握手方式因?yàn)椤拔帐帧钡拇嬖诙荒苓B續(xù)發(fā)送數(shù)據(jù),如下圖所示,可以看到連續(xù)發(fā)送造成數(shù)據(jù)丟失。

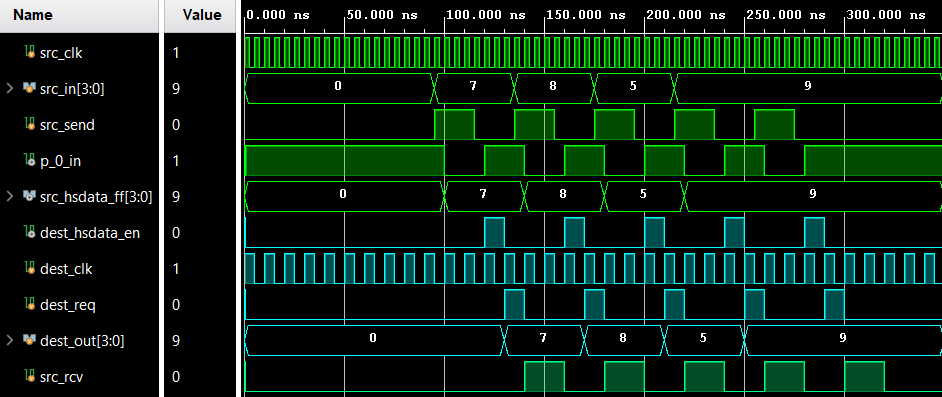

從綜合后的仿真來看,進(jìn)一步理解“握手”,如下圖所示,我們將數(shù)據(jù)路徑上發(fā)送端和接收端觸發(fā)器的使能信號添加到波形窗口里。其中p_0_in為發(fā)送端使能信號,對應(yīng)的輸出數(shù)據(jù)為src_hsdata_ff,dest_hsdata_en為接收端使能信號。

如果參數(shù)DEST_EXT_HSK為1,表明外部提供接收應(yīng)答信號,綜合結(jié)果如下圖所示。圖中藍(lán)色高亮為信號dest_ack,該信號經(jīng)跨時鐘域處理輸出src_rcv給接收端,這正是與內(nèi)部產(chǎn)生握手信號電路的區(qū)別。

綜上所述,可以看到“握手”方式需要發(fā)送端和接收端通過握手信號src_send和src_rcv或dest_ack來表明發(fā)送端有數(shù)據(jù)等待發(fā)送或接收端已接收到數(shù)據(jù),“握手”一來一回就意味著發(fā)送端不能每個時鐘周期都發(fā)送數(shù)據(jù),發(fā)送數(shù)據(jù)率必然低于時鐘頻率。同時,握手方式也無法對待發(fā)送數(shù)據(jù)進(jìn)行緩存。好處是這種方式僅僅消耗觸發(fā)器和查找表資源,資源用量比較少,電路比較簡單。

審核編輯:劉清

-

FPGA

+關(guān)注

關(guān)注

1635文章

21837瀏覽量

608348 -

時鐘

+關(guān)注

關(guān)注

11文章

1758瀏覽量

132183 -

觸發(fā)器

+關(guān)注

關(guān)注

14文章

2024瀏覽量

61495 -

SRC

+關(guān)注

關(guān)注

0文章

61瀏覽量

18133 -

時鐘域

+關(guān)注

關(guān)注

0文章

52瀏覽量

9613

原文標(biāo)題:跨時鐘域電路設(shè)計(jì)(6):多位寬數(shù)據(jù)通過握手方式跨時鐘域

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術(shù)驛站】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

如何處理好FPGA設(shè)計(jì)中跨時鐘域問題?

三種跨時鐘域處理的方法

如何處理好FPGA設(shè)計(jì)中跨時鐘域間的數(shù)據(jù)

單位寬信號如何跨時鐘域

FPGA跨時鐘域處理方法(一)

跨時鐘域電路設(shè)計(jì):單位寬信號如何跨時鐘域

多位寬數(shù)據(jù)通過握手方式跨時鐘域

多位寬數(shù)據(jù)通過握手方式跨時鐘域

評論