電信設備,服務器和數據中心的FPGA具有多個電源軌,需要正確排序才能安全地為這些系統上下供電。高可靠性DC-DC穩壓器和FPGA電源管理的設計人員需要一種簡單的方法來安全地放電大容量電容器,以避免損壞系統。

FPGA電源排序

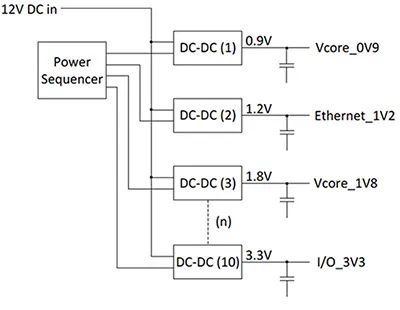

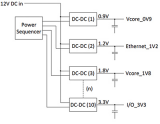

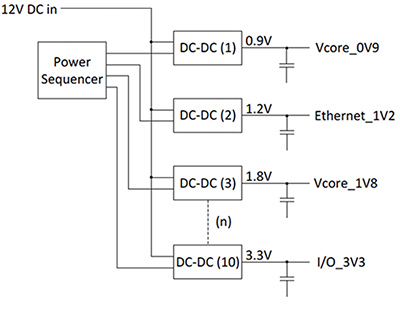

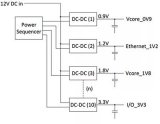

在生成片上系統FPGA的過程中,它們可以提供十個獨立的電源軌,為Vcore,存儲器總線電源,I/O控制器,以太網等提供電源。如圖1所示,每個電源軌由DC供電。直流轉換器可調節3.3 V,2.5 V,1.8 V,0.9 V等所需的電壓。為了給系統加電,遵循特定的順序以確保安全操作并避免損壞系統。同樣在系統關閉期間,電源序列的順序相反,確保在下一個電源軌關閉之前禁用每個電源軌。該指令通過電源序列發生器芯片控制,該芯片可啟用每個DC-DC穩壓器,如圖1所示。

圖1:典型FPGA系統電源軌每個服務的供電。

考慮存儲在各種電源軌上的去耦電容中的電荷時會出現問題。例如,在0.9 V Vcore電源軌上,總去耦電容可以在10到20 mF的數量級,并且存儲在電容器組中的剩余電荷需要在斷電期間主動放電,在下電源關閉之前序列被禁用。這樣可以避免違反掉電序列并保護FPGA系統。因此,建議在每個DC-DC穩壓器輸出端使用有源放電電路。

有源電容放電開關

通過了解電容器組的大小,可以采用開放式方法對RC時間常數進行放電。一旦電壓小于充電狀態的95%(在3×RC時間常數下發生),則假設電容器放電。

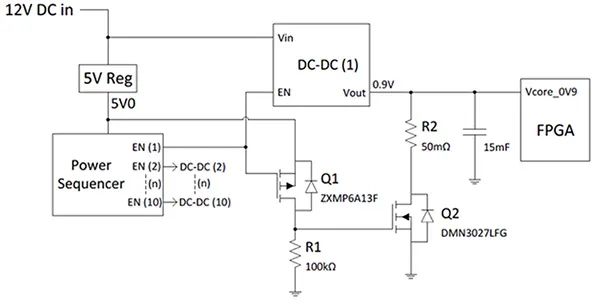

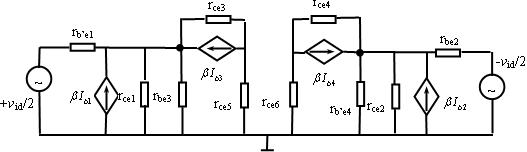

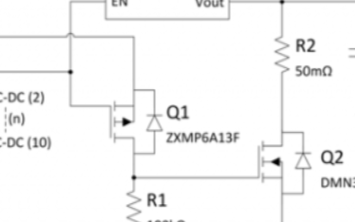

這樣做的一個簡單方法是通過一個具有已知接地電阻的開關,當需要放電時可以接通該開關。參考圖1,電源序列發生器啟用每個DC-DC穩壓器的輸出。然后可以使用該相同的使能(EN)信號來饋送并聯連接到電容器組的開關。通過反轉使能信號來驅動開關,當DC-DC穩壓器的輸出被禁止時,它將使電容器放電。對于開關,N溝道功率MOSFET,因為它很容易從以地為參考的邏輯信號驅動。所選電路如圖2所示,Q2為N溝道功率MOSFET,Q1為P溝道MOSFET,反轉電源序列發生器的EN邏輯信號。

圖2:有源放電電路。

有源電容放電電路操作

參見圖2 - 電源序列發生器的EN輸出為DC-DC穩壓器上的使能引腳供電以及電容器放電電路。當邏輯“0”發出關閉信號時,P溝道MOSFET(Q1)將信號反相,然后接通N溝道MOSFET(Q2)以對電容器組放電。

放電電路假設一旦關閉信號施加,DC-DC穩壓器就無法繼續產生輸出。如果在關閉命令激活后,DC-DC穩壓器的輸出有電,則必須在放電電路激活之前引入延遲。這是為了確保放電MOSFET不會試圖吸收DC-DC穩壓器的全部輸出電流能力。

為了從邏輯“0”信號增強N溝道功率MOSFET(Q2),P溝道MOSFET(Q1)將信號反相為5 V,以施加在Q2柵極源上。選擇P溝道MOSFET(Q1)不具有低柵極閾值電壓(VGS(th))。這是因為VGS(th)相對于溫度下降并且Q1在邏輯“1”狀態期間需要處于OFF狀態以避免Q2的錯誤接通。需要選擇適合5 V操作的值以及Power Sequencer。

當電源序列發生器輸出邏輯“1”時,DC-DC穩壓器在ON狀態下使能,Q2必須處于OFF狀態。采用邏輯“1”輸出,高電平輸出電壓為4.19 V(電源序列發生器的EN引腳輸出規格),則在環境工作溫度為60°C時,Q1 VGS(th)需要大于0.9 V 。此外,Q2的柵極需要通過100kΩ的R1電阻下拉至源極電位,以避免誤導通。

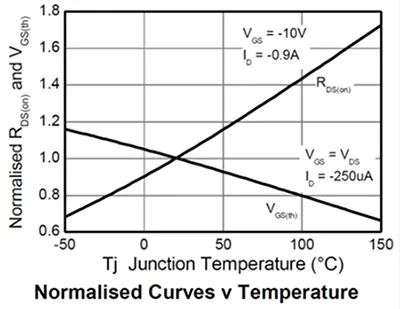

溫度的VGS(th)變化在典型的電氣曲線中找到。MOSFET數據表。例如,圖3中給出了來自Diodes Incorporated的ZXMP6A13F的歸一化VGS(th)與溫度的關系.ZXMP6A13F是器件,因為保證VGS(th)在室溫下為1 V,在60℃時降至約0.9 V °C。

圖3:ZXMP6A13F的溫度標準化RDS(on)和VGS(th)曲線。

當電源序列發生器使能輸出變為邏輯'0'時,則存在0.270 V的低電平輸出,Q1需要保證通過該5 V - 0.270 V信號增強通道,以確保Q2導通并放電電容器組。因此,Q1需要在VGS = -4.5 V時具有導通狀態。

為了對電容器組放電,選擇N溝道功率MOSFET(Q2)具有導通電阻(RDS(開) ))適合于在10 ms內對電容組放電,以確保在不到100 ms的時間內完成10個通道的完全關閉順序。必須提供輔助電源,以在關閉電源后至少100 ms驅動關閉電路(電源序列發生器)。

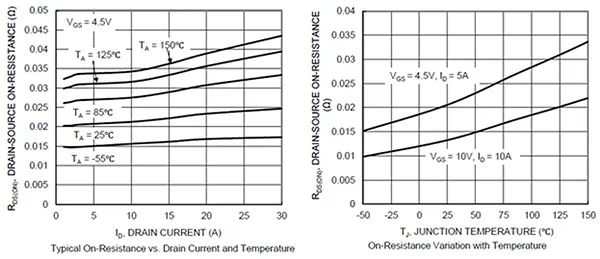

放電計算的時間

使用3 x RC時間常數,其中R是電容器組的ESR的組合電阻(假設<5mΩ),寄生走線電阻(假設為為<5mΩ),串聯漏極電阻(R2)和功率MOSFET Q2 RDS(on)。還包括功率MOSFET導通電阻的溫度依賴性,可以高達Tamb =25?C時RDS(on)的1.5倍,同時假設結已達到額定溫度(典型TJ(值) )= 150°C) - 參見圖5.

要在不到10 ms的時間內對15 mF電容器組放電,需要3 x RC = 8 ms:

電容器

因此,功率MOSFET Q2在VGS = 4.5 V,Tamb =25?C時需要RDS(on)<80mΩ。假設一個50mΩ的串聯漏極電阻(在圖2中稱為R2)與MOSFET一起使用。

安全工作區和瞬態熱應力

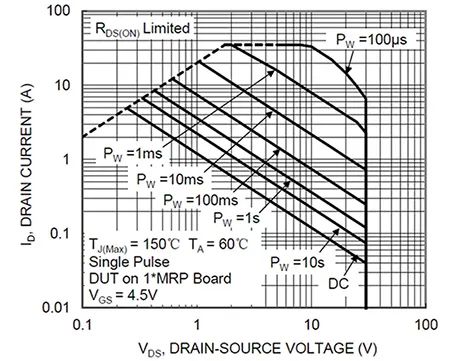

選擇功率MOSFET Q2的額定功率能夠處理放電電流的瞬態功耗。通過仿真計算峰值功率,并根據功率MOSFET數據表的瞬態功率容量圖檢查該值。由于功率MOSFET將隨時間消耗電容器的能量作為電流和電壓的函數,因此需要檢查數據表中的安全工作區(SOA)曲線。這將提供功率MOSFET可以安全處理的單脈沖,同時確保結溫不超過額定值,典型TJ(值)= 150°C。SOA應該基于應用的環境工作溫度和所需的MOSFET柵極驅動,在這種情況下為4.5V。在放電0.9 V充電電容器組的情況下,然后檢查SOA曲線,以獲得1 V時的單脈沖峰值電流能力在1 ms和10 ms之間的脈沖寬度曲線。SOA應該針對典型的應用環境溫度(假設為60°C),同時安裝在PCB上,散熱,也稱為推薦焊盤(MRP)布局。在這些條件下,請參考圖4了解DMN3027LFG的SOA。

圖4:DMN3027LFG的安全工作區(SOA)

需要在實際電路中測量電容器組的峰值浪涌電流,以確保足夠的電阻減慢響應速度,以避免可能導致EMI問題的急劇上升電流峰值以及N通道上的瞬態熱應力功率MOSFET和電容器組。在圖2中,將一個50mΩ串聯電阻添加到Q2的漏極,以確保固定的已知值(與溫度無關)在放電路徑中的總電阻中占主導地位。

MOSFET導通電阻變化

請注意MOSFET的導通電阻隨溫度變化,如圖5所示,在4.5 V柵極驅動的預期工作溫度范圍內變化高達15mΩ。除此之外,您還將在零件到零件和批次之間進行RDS(on)變化。典型的RDS(on)為22mΩ,在室溫下DMN3027LFG上4.5 V柵極驅動的規格限制為26mΩ。

圖5:DMN3027LFG的導通電阻溫度響應。

因此,為確保已知電阻在放電路徑中占主導地位,做法是使用R2系列電阻,該電阻約為RDS(on)的兩倍在選定的門驅動器上。當R2為50mΩ且RDS(on)在15mΩ至40mΩ(典型值為22mΩ)之間變化時,95%的放電時間為3.9至5.4 ms(3 x RC)。這是差情況下電容器組大小為20 mF。

功耗

計算功率MOSFET Q2和串聯電阻R2的功耗取決于占空比和Q2導通的時間。

如果在Q2導通時DC-DC穩壓器上的0.9 V輸出使能,那么Q2和R2之間可以達到11 W。假設結溫達到150°C,典型的RDS(on)穩定在35mΩ,如圖5所示。不應允許這種情況,因為它違反了DMN3027LFG的功耗并導致結點溫度超過額定值。因此,必須禁用DC-DC穩壓器輸出,同時啟用Q2。

這意味著壞的情況是由電容器短時間充電和放電引起的。假設電源序列發生器進入連續循環啟用,然后每隔20 ms禁用DC-DC穩壓器(10 ms啟用+ 10 ms禁用),那么這將導致Q2和R2上的功率約為0.5 W.這是通過知道存儲在電容器組中的總能量將每20 ms放電來計算的:

P = E/t =?CV2/20 ms = 500 mW,電容器組的C = 20 mF充電至1 V.

壞情況下,RDS(on)為40mΩ,26mΩx1.5,VGS = 4.5 V,TJ(值)= 150°C(圖3)。因此,Q2和R2的功耗分別為222 mW和278 mW。15mΩ的RDS(on)會使R2的功耗增加到385 mW;意味著需要0.5 W額定值的表面貼裝電阻。

在典型應用中,環境溫度預計達到60°C,DMN3027LFG在推薦焊盤布局上的RθJA= 130°C/W,當耗散222 mW時,TJ達到90°C 。這為TJ()= 150°C提供了充足的空間。

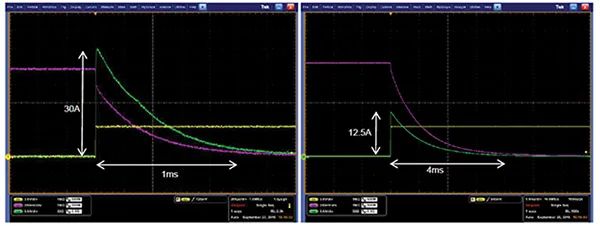

電容器組放電測量

使用DMN3027LFG和ZXMP6A13F組裝使用6 x 2,200 uF電解電容器(13.2 mF)的電容器組,如圖2所示.ZXMP6A13F用5 V手動觸發信號。

使用和不使用50mΩ串聯電阻進行測量,然后在室溫,零下和高溫下進行測量,以觀察峰值電流和放電時間的變化。僅通過DMN3027LFG通道RDS(on)電阻(不帶50mΩ)放電會產生觀察峰值電流的壞情況。請注意以下曲線中的時間尺度不同 - 200μs/div和1 ms/div通道1(C1)為黃色= DMN3027LFG柵極引腳上的電壓通道3 (C3)為品紅色=電容器組上的電壓

通道4(C4)為綠色=來自DMN3027LFG源引腳的電流探頭

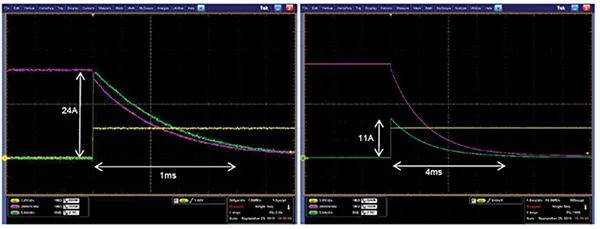

圖6:室溫測量(約Ta = 20°C)。左曲線= 30 A峰值電流僅通過DMN3027LFG通道電阻放電(200μs/div)右曲線= 12.5通過DMN3027LFG和50mΩ串聯電阻放電的峰值電流(1 ms/div)參見圖6,圖7和圖8 - 僅通過DMN3027LFG對13.2 mF電容器組放電,產生的峰值電流從24 A變化到35 A,具體取決于MOSFET RDS(on)的溫度響應。通過添加50mΩ串聯電阻,可將峰值電流限制在<15 A,溫度變化僅限于11 A至14 A.請注意,隨著溫度升高,峰值電流會相對于RDS(on)增加而下降。

即使溫度變化,放電時間至初始1 V充電狀態的95%也會在約3至4 ms內發生。這與3 x RC時間常數的預期相同,SPICE建模此電路可以復制類似的結果。模擬一個13.2 mF電容器組在27°C(默認),加入50mΩ串聯電阻,然后峰值電流約為13 A,并在3 ms內放電至95%。

圖7:高溫測量(大約Ta = 70°C)。左曲線= 24僅通過DMN3027LFG通道電阻的峰值電流放電(200μs/div)右曲線= 11通過DMN3027LFG和50mΩ串聯電阻(1 ms/div)放電的峰值電流

圖8:零下溫度測量(約Ta = -20°C)。左曲線= 35僅通過DMN3027LFG通道電阻的峰值電流放電(200μs/div)右曲線= 14通過DMN3027LFG和50mΩ串聯電阻(1 ms/div)放電的峰值電流結論

已經證明了一種基于已知RC時間常數對大電容器組放電的安全且簡單的方法。這種開放式技術可以根據電容大小進行縮放。選擇了以下器件:

Q1 = SOT23中的ZXMP6A13F P溝道MOSFET

Q2 = PowerDI3333-8中的DMN3027LFG N溝道MOSFETR2 = 50mΩ表面貼裝電阻能夠耗散500 mW。

通過在放電路徑中添加50mΩ串聯電阻,可以限制峰值放電電流并穩定溫度變化。測量結果和模擬結果均吻合良好;讓設計師有信心對不同的電容器組尺寸進行建模。

審核編輯:湯梓紅

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603017 -

控制器

+關注

關注

112文章

16334瀏覽量

177815 -

電源管理

+關注

關注

115文章

6180瀏覽量

144452 -

電路設計

+關注

關注

6673文章

2451瀏覽量

204169 -

DC-DC

+關注

關注

30文章

1943瀏覽量

81604

原文標題:FPGA系統中有源電容放電電路設計需注意哪些問題

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

FPGA系統有源電容放電電路怎么避免損壞系統?

集成運放電路中有源負載放大電路的分析與計算方法

FPGA的有源電容放電電路考慮

關于設計FPGA系統中有源電容放電電路的方法和需要注意的問題

如何結合晶振的負載電容計算外匹配電容容值以及在晶振振蕩電路設計時需注意哪些事項?資料下載

有源放電電路的原理和注意事項

FPGA系統中有源電容放電電路設計需注意哪些問題

FPGA系統中有源電容放電電路設計需注意哪些問題

評論