本節講一下硬件系統中常用的濾波電路,主要包括芯片的濾波電路,一些模擬芯片的濾波電路,模擬電路的濾波電路。

基本上是項目中遇到的一些實際情況。

SoC常用的濾波電路有這么幾類:儲能電容,旁路電容,RC濾波,LC濾波,pi型濾波等。

儲能電容

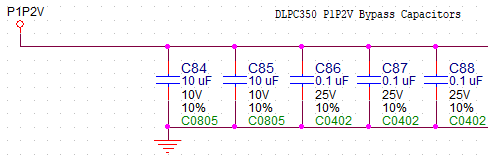

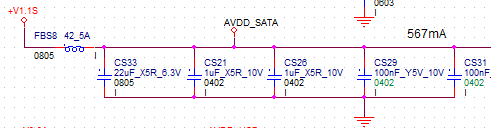

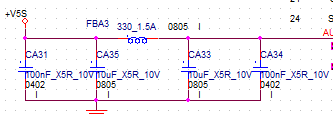

下圖2個10uF的電容就是儲能電容。

一般電路系統中的電源輸出端是DCDC或者LDO,那么從電源輸出端到用電器件/SoC管腳還會有一段不短的距離,而儲能電容都是靠近用電器件/SoC管腳擺放。否則的話,過長的供電路徑會造成電量抽載時供電不穩。

儲能電容的大小,主要依賴于用電消耗,不同的用電器件需求不同,要根據規格書/設計指導/參考電路來選擇。

深入到芯片內部來說,主要是動態消耗部分所決定的,這個和電路原理(IP核),制程工藝都相關,一般來說,IP復雜度越高,芯片制程工藝越落后,動態功耗就會越大。

儲能電容的數量,一般要求SoC的每個功能塊至少一個,不同的功能塊之間最好不要共用。

儲能電容的容值選擇,從100~470UF的電解電容,到22uF,10uF,2.2uF,1uF的陶瓷電容都會出現。

一般是沿用參考設計的,而參考設計則是從芯片模型電源完整性仿真,實際測試最終形成的——這部分一般來說只有SoC廠商有能力做,甚至很多也沒有仿真能力。而下游的產品研發/生產商沒有這個能力,所以很難做改動。

下圖是TI的某投影SoC所用

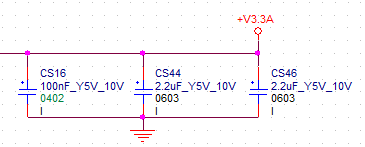

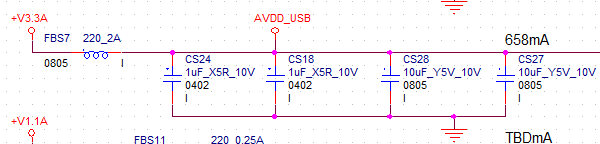

下面兩圖是英特爾的某筆電平臺所用(22uF,2.2uF,1uF)

如果參考設計用的儲能電容比較多,實際產品中由于PCB面積受限等,無法實現,必須縮減的情況下,縮減到多少為好呢?

嚴格來說,這要通過電源仿真來確認。但是,一般情況下芯片模型數據,公司技術能力等都有限,沒辦法去做這樣的仿真,主要是依據經驗和產品實測決定。

迫于成本/體積壓力等,必須減少的情況下,那么可以根據實際測量情況來修改,即測量各種工作模式/負載情況下,紋波的頻率,依據這些數據來設計。思路上有兩種,一是逐步減少,即逐個減少后看測量數據;二是根據經驗一次性減少若干個之后,再根據測量數據加回來一些。保障電源紋波不超過芯片要求的情況下,最終形成一種方案。

由于測量不充分(很難模擬到所有工作模式/可能性等),修改是比較容易產生問題的。筆者曾做過的一款安防產品(DVR)就遇到過這樣的問題,原廠參考設計是6層PCB,且儲能電容比較豐富,而實際產品所用的PCB是4層板,儲能電容也縮減了一些,導致出現了老化過程中死機的問題,最終在SoC的core電源上增加了一顆22uF的儲能電容才解決。

旁路電容

上圖中0.1uF的幾個電容就是旁路電容;

芯片一般要求每個管腳旁邊放置一顆。如果SoC管腳比較緊密,無法保障每個管腳旁邊放置一顆的話,可以適當減少,比如23個管腳共用一顆,距離要靠近,不能太遠。或者25個管腳共用2可旁路電容。

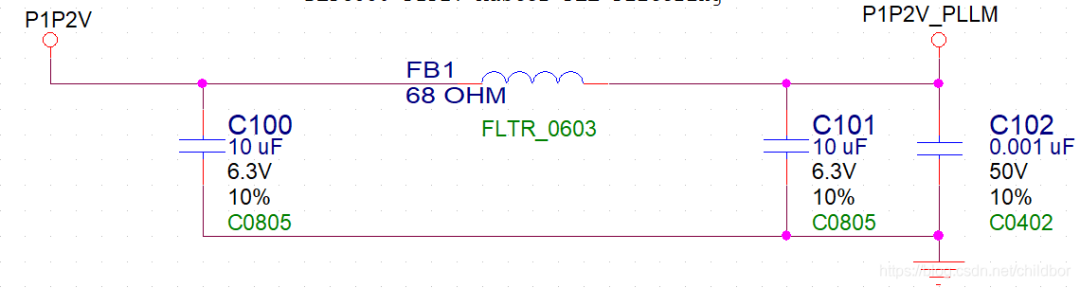

LC濾波

LC濾波在SoC的需求,一般是磁珠+電容的方式,不是電感+電容的方式。

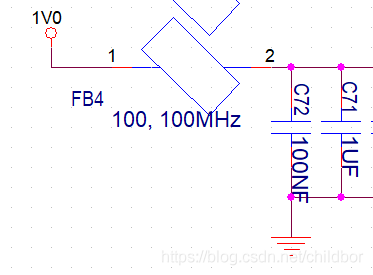

比如下圖,就是海思3521芯片的PLL部分的參考電路。可以看到,是用100R/100MHz磁珠+1uF+0.1uF的電容構成。

通常,LC濾波用于一些要求略高的功能模塊,模擬部分,PLL部分等。純數字部分一般用儲能電容+旁路電容的方式就能滿足需求。

下圖是海思3521芯片的PLL部分

下面兩圖是英特爾的某筆電平臺所用(22uF,2.2uF,1uF)

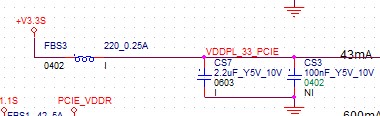

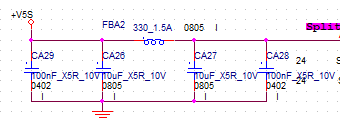

pi型濾波

pi型濾波是SoC對電源要求更高的情況下才會使用的。

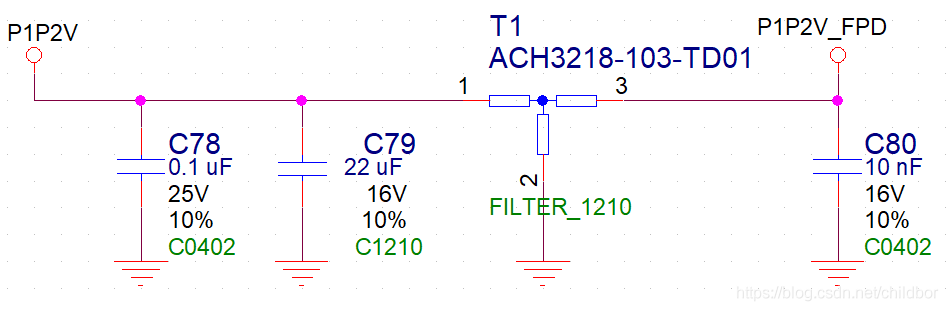

下圖是英特爾某筆電平臺的Audio Codec所用;

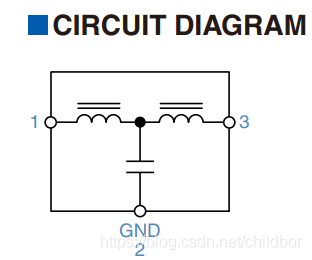

如果要求更高的話,還會用到三端濾波器,如下圖所示。

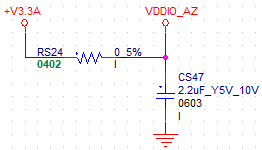

RC濾波

RC濾波一般用的比較少,實在沒辦法才會用到。一般是用個幾歐姆的電阻,比如5.1歐姆,后面是儲能電容和旁路電容。一般來說,SoC工作的情況下,等效電阻也就是幾歐姆,到十幾歐姆,所以這種LC濾波雖然能有效減小紋波,但是也會容易導致壓降比較大,芯片無法工作。

下圖是英特爾某筆電平臺所用,此處是0R,根據情況會做調整,一般不超過5.1R。

-

ldo

+關注

關注

35文章

1944瀏覽量

153530 -

soc

+關注

關注

38文章

4177瀏覽量

218464 -

電路系統

+關注

關注

0文章

70瀏覽量

12939 -

DCDC

+關注

關注

29文章

820瀏覽量

71361

發布評論請先 登錄

相關推薦

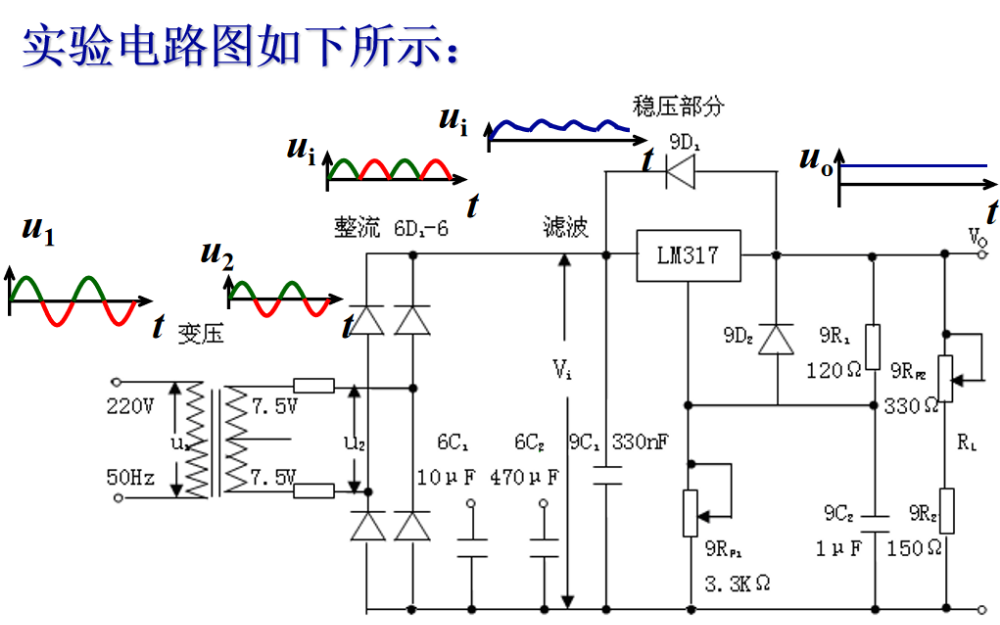

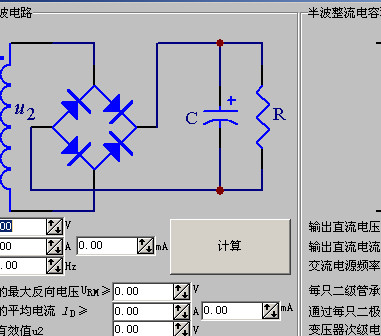

模擬電路實驗之整流濾波與穩壓電路的詳細資料說明

電源濾波電路淺析

電路中濾波電容和退耦電容_詳解電源濾波電路中的高頻濾波電容電路

電源設計之濾波電路

電源設計之濾波電路

評論