一、電源噪聲重要性

芯片內(nèi)部有成千上萬個晶體管,這些晶體管組成內(nèi)部的門電路、組合邏輯、寄存器、計數(shù)器、延遲線、狀態(tài)機、以及其他邏輯功能。隨著芯片的集成度越來越高,內(nèi)部晶體管數(shù) 越來越大。芯片的外部引腳數(shù)有限,為一個晶體管提供單獨的供電引腳是不現(xiàn)實的。芯 片的外部電源引腳提供給內(nèi)部晶體管一個公共的供電節(jié)點, 因此內(nèi)部晶體管狀態(tài)的轉(zhuǎn)換必 然引起電源噪聲在芯片內(nèi)部的傳遞。

??對內(nèi)部各個晶體管的操作通常由內(nèi)核時鐘或片內(nèi)外設(shè)時鐘同步, 但是由于內(nèi)部延時的 差別,各個晶體管的狀態(tài)轉(zhuǎn)換不可能是嚴格同步的,當某些晶體管已完成了狀態(tài)轉(zhuǎn)換,另 一些晶體管可能仍處于轉(zhuǎn)換過程中。芯片內(nèi)部處于高電平的門電路會把電源噪聲傳遞到其 他門電路的輸入部分。如果接受電源噪聲的門電路此時處于電平轉(zhuǎn)換的不定態(tài)區(qū)域,那么電 源噪聲可能會被放大,并在門電路的輸出端產(chǎn)生矩形脈沖干擾,進而引起電路的邏輯錯誤。芯片外部電源引腳處的噪聲通過內(nèi)部門電路的傳播,還可能會觸發(fā)內(nèi)部寄存器產(chǎn)生狀態(tài)轉(zhuǎn)換。

??除了對芯片本身工作狀態(tài)產(chǎn)生影響外,電源噪聲還會對其他部分產(chǎn)生影響。比如電源噪 聲會影響晶振、PLL、DLL 的抖動特性,AD 轉(zhuǎn)換電路的轉(zhuǎn)換精度等。由于最終產(chǎn)品工作溫度的變化以及生產(chǎn)過程中產(chǎn)生的不一致性,如果是由于電源系統(tǒng)產(chǎn)生的問題,電路將非常難調(diào)試,因此最好在電路設(shè)計之初就遵循某種成熟的設(shè)計規(guī)則,使電源系統(tǒng)更加穩(wěn)健。

二、電源噪聲產(chǎn)生的原因

第一,穩(wěn)壓電源芯片本身的輸出并不是恒定的,會有一定的波紋。這是由穩(wěn)壓芯片自身決定的,一旦選好了穩(wěn)壓電源芯片,對這部分噪聲我們只能接受,無法控制。

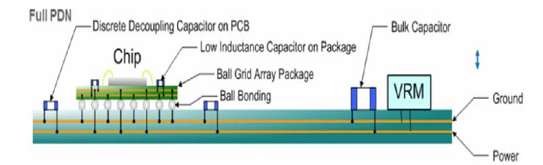

??第二,穩(wěn)壓電源無法實時響應(yīng)負載對于電流需求的快速變化。穩(wěn)壓電源芯片通過感知其輸出電壓的變化,調(diào)整其輸出電流,從而把輸出電壓調(diào)整到額定輸出值。多數(shù)常用的穩(wěn)壓源調(diào)整電壓的時間在 ms~us 級。因此,對于負載電流變化頻率在直流到幾百 KHz 之間時,穩(wěn)壓源可以很好的做出調(diào)整,保持輸出電壓的穩(wěn)定。當負載瞬態(tài)電流變化頻率超出這一范圍時,穩(wěn)壓源的電壓輸出會出現(xiàn)跌落,從而產(chǎn)生電源噪聲。現(xiàn)在,微處理器的內(nèi)核及外設(shè)的時鐘頻 率已超過了 600 MHz,內(nèi)部晶體管電平轉(zhuǎn)換時間下降到 800 ps以下。這要求電源分配系統(tǒng)必須在直流到 1GHz 范圍內(nèi)都能快速響應(yīng)負載電流的變化,但現(xiàn)有穩(wěn)壓電源芯片不可能滿足這一苛刻要求。我們只能用其他方法補償穩(wěn)壓源這一不足,這涉及到后面要講的電源去耦。

??第三,負載瞬態(tài)電流在電源路徑阻抗和地路徑阻抗上產(chǎn)生的壓降。PCB板上任何電氣 路徑不可避免的會存在阻抗,不論是完整的電源平面還是電源引線。對于多層板,通常提供 一個完整的電源平面和地平面,穩(wěn)壓電源輸出首先接入電源平面,供電電流流電源平面,到達負載電源引腳。地路徑和電源路徑類似,只不過電流路徑變成了地平面。完整平面的阻抗很低,但確實存在。如果不使用平面而使用引線,那么路徑上的阻抗會更高。另外,引腳及焊盤本身也會有寄生電感存在,瞬態(tài)電流流此路徑必然產(chǎn)生壓降,因此負載芯片電源引腳處的電壓會隨著瞬態(tài)電流的變化而波動,這就是阻抗產(chǎn)生的電源噪聲。在電源路徑表現(xiàn)為負載芯片電源引腳處的電壓軌道塌陷, 在地路徑表現(xiàn)為負載芯片地引腳處的電位和參考地電位不同 (注意,這和地彈不同,地彈是指芯片內(nèi)部參考地電位相對于板級參考地電位的 跳變)。

三、退耦電容使用

對于電容的安裝,首先要提到的就是安裝距離。容值最小的電容,有最高的諧振頻率, 去耦半徑最小,因此放在最靠近芯片的位置。容值稍大些的可以距離稍遠,最外層放置容值 最大的。但是,所有對該芯片去耦的電容都盡靠近芯片。

??在放置時,最好均勻分布在芯片的四周,對一個容值等級都要這樣。通常芯片在設(shè)計的時候就考慮到了電源和地引腳的排列位置,一般都是均勻分布在芯片的四個邊上的。因此,電壓擾動在芯片的四周都存在,去耦也必須對整個芯片所在區(qū)域均勻去耦。

??在安裝電容時,要從焊盤拉出一小段引出線,然后通過過孔和電源平面連接,接地端也 同樣。這樣流電容的電流回路為:電源平面->過孔->引出線->焊盤->電容->焊盤->引出>過孔->地平面(放置過孔的基本原則就是讓這一環(huán)路面積最小,進而使總的寄生電感最小)。

??由于印制線越寬,電感越小,從焊盤到過孔的引出線盡加寬,如果可能,盡和焊盤寬度相同。這樣即使是 0402 封裝的電容,你也可以使用 20mil 寬的引出線。

??需要強調(diào)一點:有些工程師為了節(jié)省空間,有時讓多個電容使用公共過孔。任何情況下都不要這樣做。最好想辦法優(yōu)化電容組合的設(shè)計,少電容數(shù)。

四、總結(jié)

電源系統(tǒng)去耦設(shè)計要把引腳去耦和電源平面去耦結(jié)合使用已達到最優(yōu)設(shè)計。時鐘、 PLL、 DLL 等去耦設(shè)計要使用引腳去耦,必要時還要加濾波網(wǎng)絡(luò),模擬電源部分還要使用磁珠等進 行濾波。針對具體應(yīng)用選擇退耦電容的方法也很流行,如在電路板上發(fā)現(xiàn)某個頻率的干擾較 大,就要專門針對這一頻率選擇合適的電容,改進系統(tǒng)設(shè)計。總之,電源系統(tǒng)的設(shè)計和具體 應(yīng)用密切相關(guān),不存在放之四海皆準的具體方案。關(guān)鍵是掌握基本的設(shè)計方法,具體情況具 體分析,才能很好的解決電源去耦問。

審核編輯黃宇

-

芯片

+關(guān)注

關(guān)注

456文章

51060瀏覽量

425702 -

電源完整性

+關(guān)注

關(guān)注

9文章

211瀏覽量

20749

發(fā)布評論請先 登錄

相關(guān)推薦

是德示波器在電源完整性分析中的應(yīng)用

電源完整性分析參考解決方案

高速PCB的信號完整性、電源完整性和電磁兼容性研究

高速電路電源分配網(wǎng)絡(luò)設(shè)計與電源完整性分析

示波器探頭在電源完整性測量上的應(yīng)用

搞定電源完整性,不如先研究PDN

搞定電源完整性,不如先研究PDN!

電源完整性問題是指什么?電源完整性分析

電源完整性分析

電源完整性分析

評論