設(shè)計(jì)流程:

設(shè)計(jì)規(guī)劃--波形繪制--編寫代碼--代碼編譯--編寫testbench--對比波形--綁定管腳--全編譯--上板驗(yàn)證

設(shè)計(jì)規(guī)劃

使用用戶手冊,了解硬件資源,這個示例中需要用到按鍵和LED燈:

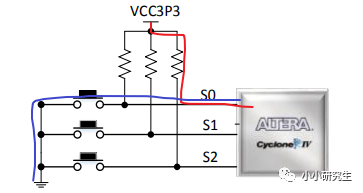

1、按鍵

在沒有按鍵按下時,輸出高電平(紅色); 當(dāng)按鍵按下的時候,被按下的按鍵端會輸出低電平(藍(lán)色)。

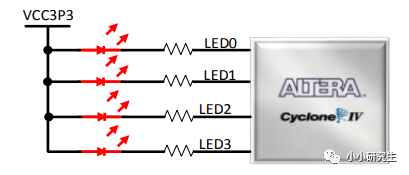

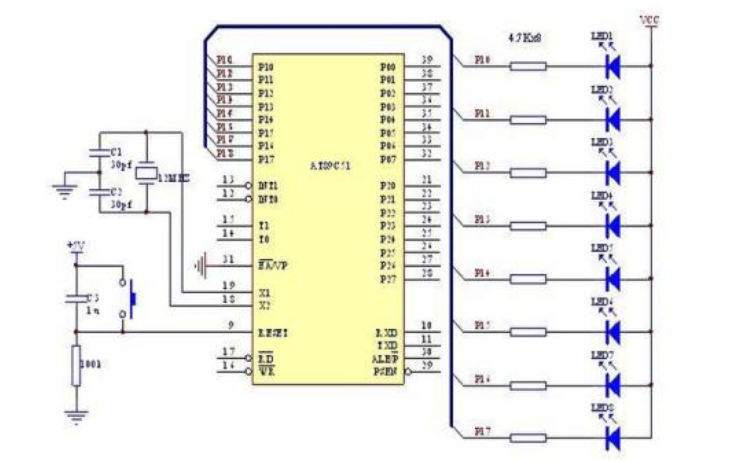

2、LED燈

當(dāng) FPGA 輸出低電平時,LED 點(diǎn)亮,當(dāng) LED 輸出高電平時,沒有電位差,LED 燈熄滅。

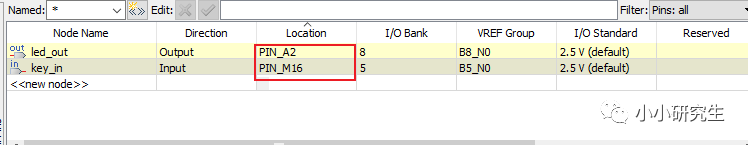

由上可知:需要實(shí)現(xiàn)的功能是,當(dāng)按下按鍵時(key_in=0,PIN_M16管腳),LED燈要被點(diǎn)亮(led_out=0,PIN_A2管腳)。 此處波形非常簡單,省略畫波形的步驟,對于復(fù)雜電路還是需要畫波形來理清思路。 這里波形應(yīng)該是key與led波形一致。

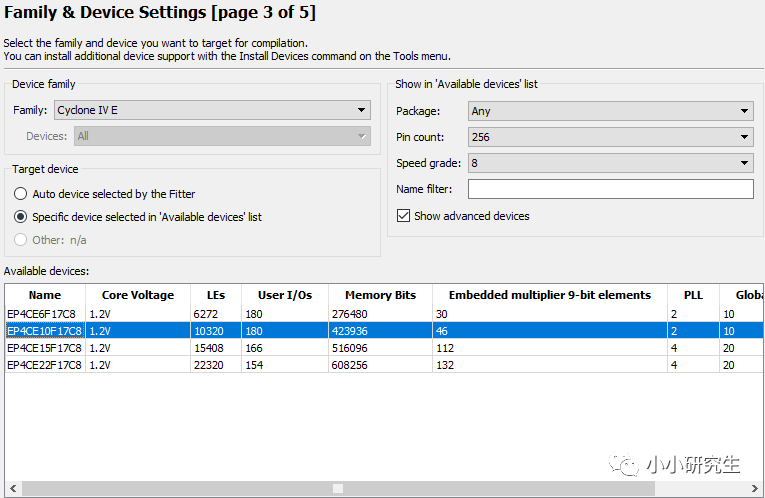

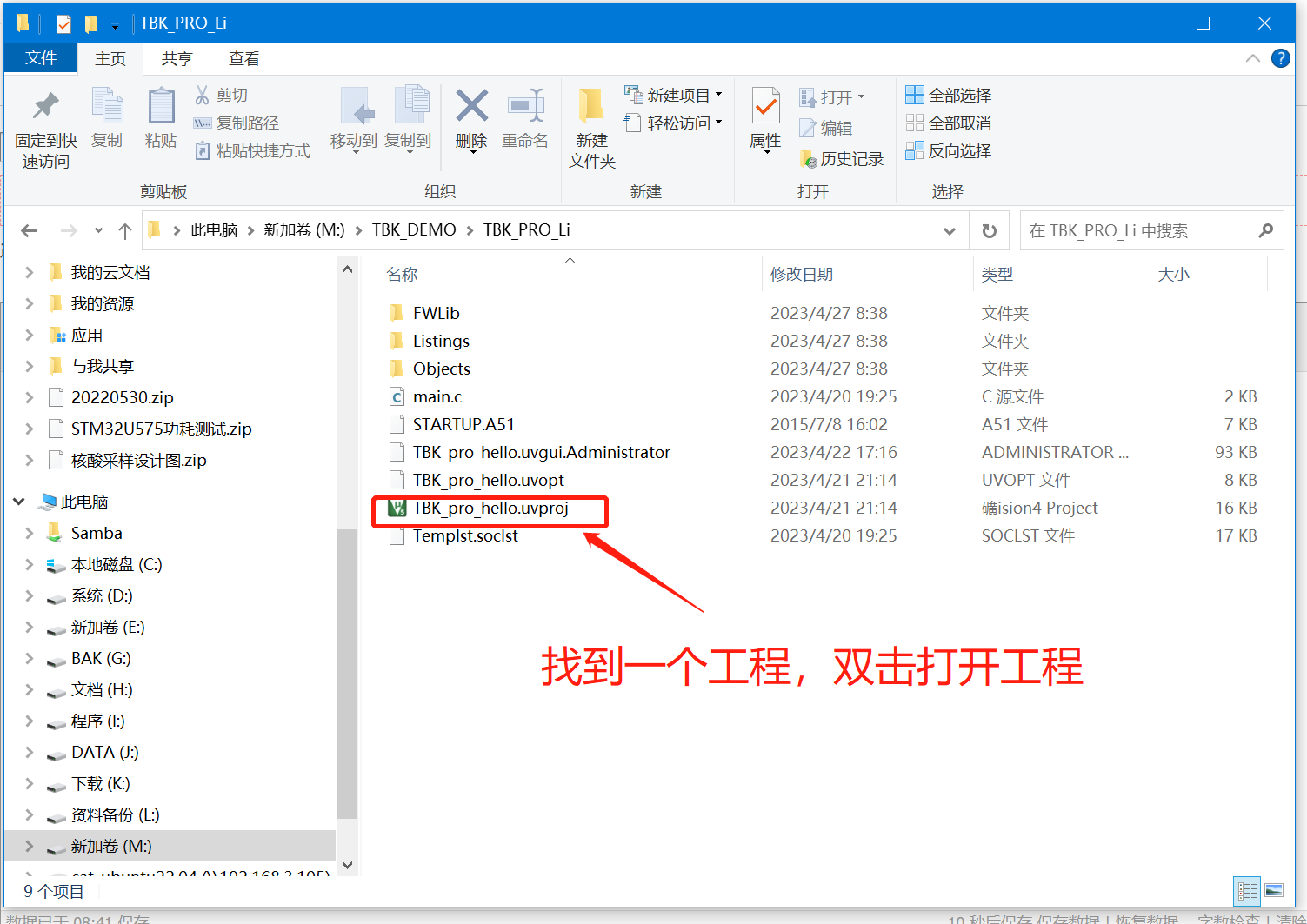

打開quartus,新建工程。

編寫代碼

編寫.v文件,代碼如下:

module led

(

input wire key_in , //輸入按鍵

output wire led_out //輸出控制led燈

);

//led_out:led燈輸出的結(jié)果為key_in按鍵的輸入值

assign led_out = key_in;

endmodule

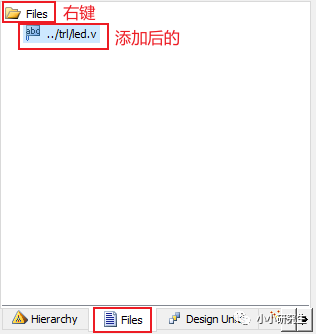

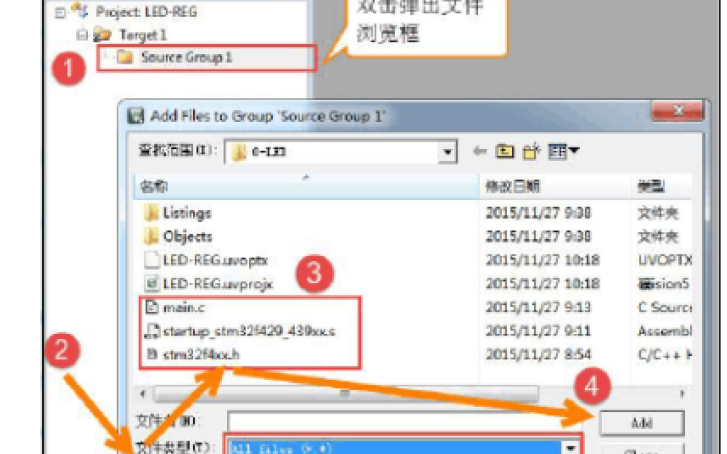

將.v文件添加到文件目錄下,右鍵Files文件夾選擇添加.v文件,添加完成后可以在Files下看到添加的.v文件:

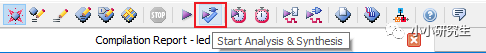

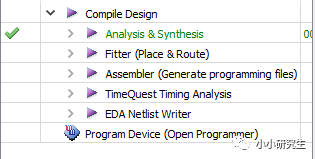

代碼編譯

點(diǎn)擊如圖所示的圖標(biāo),可以檢查語法是否有錯,綜合器將代碼解釋為電路的形式。 綠色表示通過。

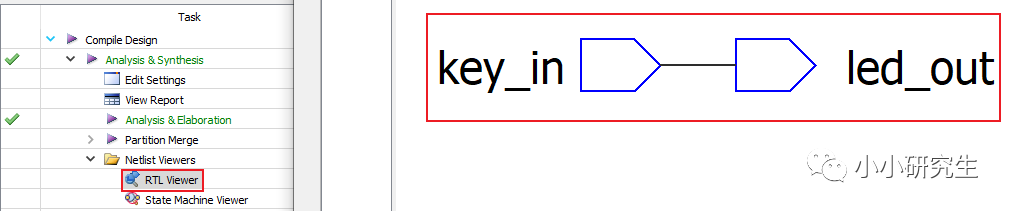

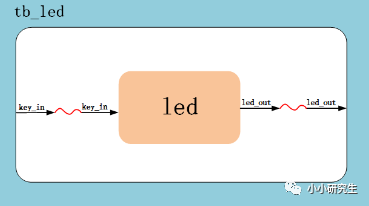

點(diǎn)擊RTL viewer可以查看設(shè)計(jì)的硬件電路結(jié)構(gòu),和我們設(shè)計(jì)所表達(dá)的意思相同

編寫testbench

Testbench是測試電路功能和性能的腳本。 在線邏輯分析雖然好用但是每次修改代碼都需要綜合一次,而使用testbench做仿真的速度就很快,所以一開始就應(yīng)該編寫testbench以便后面大型電路的驗(yàn)證。

testbench就是產(chǎn)生輸入波形,加入到被測模塊上并觀測其輸出,和我們之前畫好的波形進(jìn)行比對。

編寫.v文件

`timescale 1ns/1ns //時間尺度/時間精度,時間精度<=時間尺度

module tb_led();

wire led_out ;

reg key_in ;

//初始化輸入信號

initial key_in <= 1'b0;

//key_in:產(chǎn)生輸入隨機(jī)數(shù),模擬按鍵的輸入情況

always #10 key_in <= {$random} % 2; /*取模求余數(shù),產(chǎn)生非負(fù)隨機(jī)數(shù)0、1

每隔10ns產(chǎn)生一次隨機(jī)數(shù)*/

//\\* Instantiate \\//

led led_inst

(

.key_in (key_in ), //input key_in

.led_out(led_out) //output led_out

);

endmodule

tb_led模塊中,首先定義初始的輸入信號為低電平(一般時序電路使用非阻塞賦值<=),延遲10個時間單位(ns)產(chǎn)生隨機(jī)數(shù)0或1賦值給輸入,就完成了輸入信號的波形設(shè)計(jì)。 根據(jù)上一節(jié)中實(shí)例化的講解,第2-5行和第14-19行完成的功能是將上一個led.v文件中l(wèi)ed模塊與tb_led模塊相連。 這樣隨機(jī)生成的輸入信號就被加到led模塊上,并得到輸出led_out,通過驗(yàn)證led_out與我們期望的輸出是否一致,就知道我們的設(shè)計(jì)是否正確。

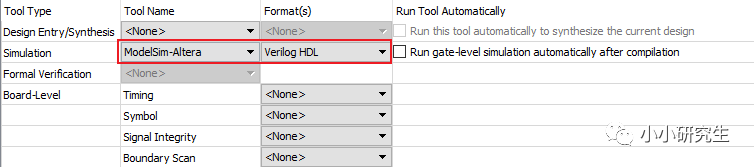

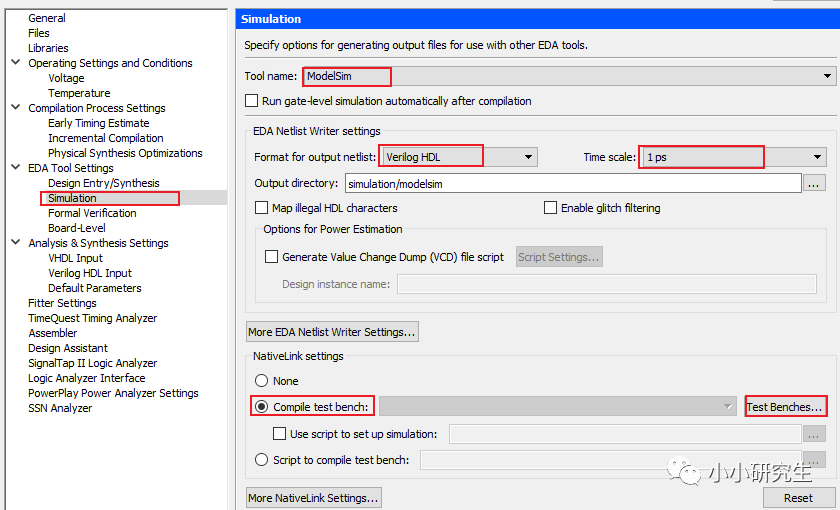

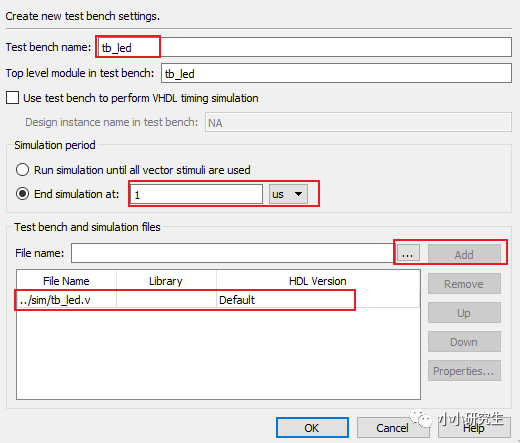

和之前的操作一樣,將這個tb_led.v文件添加到Files文件下。 然后在quartus的菜單欄中找到assignments-setting,如圖所示。

對比波形

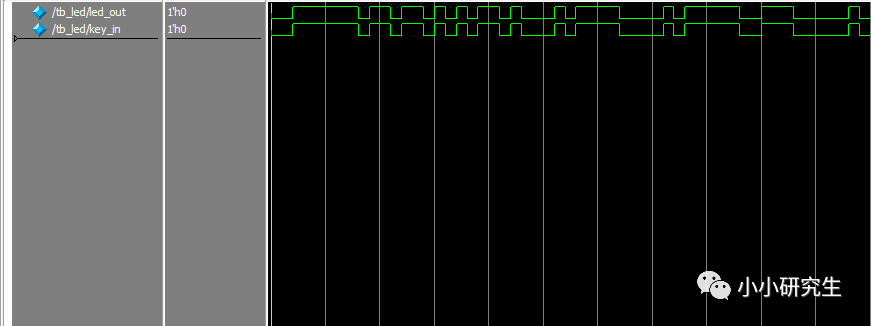

設(shè)置完成后,點(diǎn)擊菜單欄的tools-run simulation tool-RTL simulation,能自動打開modelsim說明之前的關(guān)聯(lián)操作是成功的,如果不成功,在上一節(jié)中看怎么關(guān)聯(lián)。 得到波形如圖,觀察得知led_out波形與key_in波形一致。

分配管腳

在開發(fā)板用戶手冊中就有對應(yīng)管腳,按鍵有三個,我們選擇M16的S0作為key_in,LED有四個,我們選擇A2的LED0作為led_out。

全編譯

全編譯需要進(jìn)行布局布線,管腳綁定后就可以對全局進(jìn)行布局布線了。 沒有錯誤就可以上板了,有錯誤的話根據(jù)提示改。

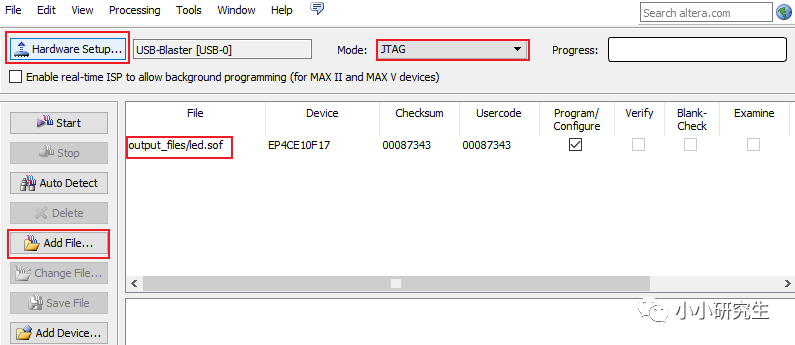

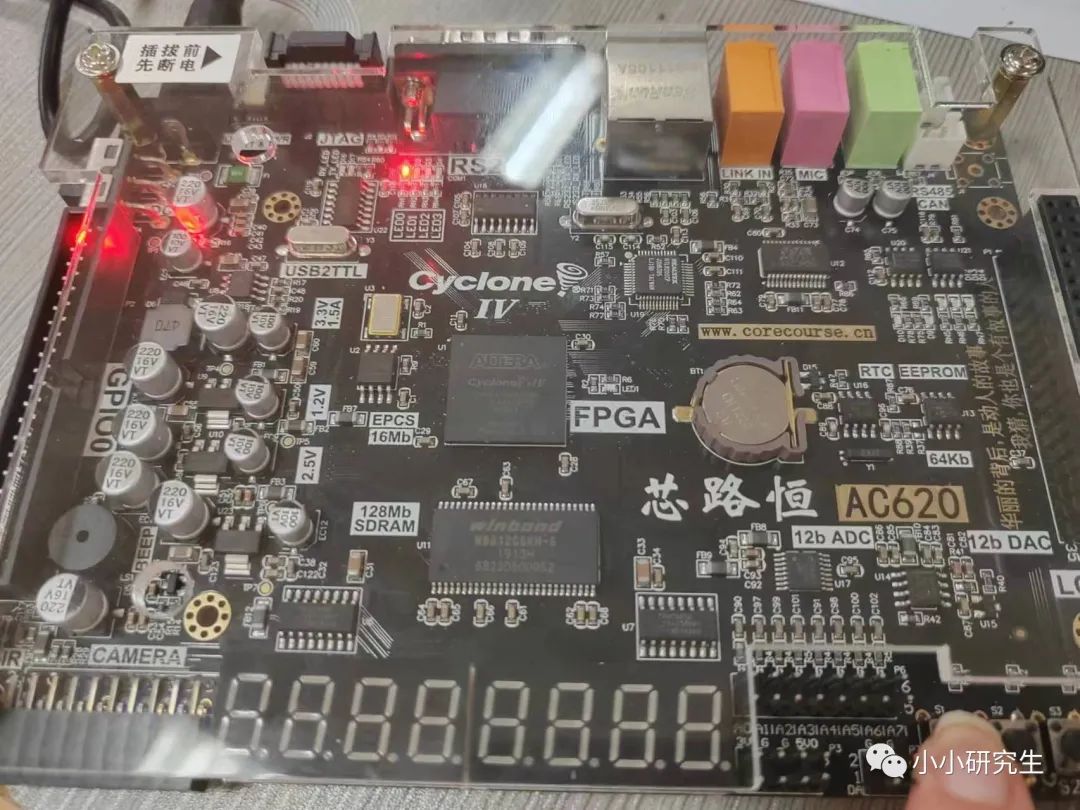

上板驗(yàn)證

上板是需要安裝USB_blaster驅(qū)動的,在設(shè)備管理器中如果USB-blaster有黃色感嘆號需要右鍵更新,文件在安裝文件quartus-drivers-USBblaster或USBblaster ii中。 安裝完成后感嘆號消失。

再點(diǎn)start,右上角的progress到100%,開發(fā)板就下載完成了。

按著按鍵A0不放,LED0一直被點(diǎn)亮,松手就關(guān)閉。

這樣最簡單的小設(shè)計(jì)就實(shí)現(xiàn)了,堅(jiān)持到這里就成功了一半哦。

-

FPGA

+關(guān)注

關(guān)注

1629文章

21754瀏覽量

604234 -

led燈

+關(guān)注

關(guān)注

22文章

1592瀏覽量

108108 -

usb

+關(guān)注

關(guān)注

60文章

7959瀏覽量

265048 -

按鍵

+關(guān)注

關(guān)注

4文章

223瀏覽量

57619 -

開發(fā)板

+關(guān)注

關(guān)注

25文章

5081瀏覽量

97692

發(fā)布評論請先 登錄

相關(guān)推薦

點(diǎn)亮STM32、FPGA和Liunx板子的LED燈

怎樣通過FPGA去點(diǎn)亮開發(fā)板上的LED燈?

使用STM32點(diǎn)亮LED燈的方法

在FPGA開發(fā)板中點(diǎn)亮LED燈實(shí)現(xiàn)時序邏輯電路的設(shè)計(jì)

如何使用單片機(jī)點(diǎn)亮LED燈

點(diǎn)亮LED燈的源代碼免費(fèi)下載

史上最全的LED點(diǎn)燈程序—使用STM32、FPGA、Linux點(diǎn)亮你的LED燈

51單片機(jī)——點(diǎn)亮一個LED燈

基于FPGA點(diǎn)亮LED燈

基于FPGA點(diǎn)亮LED燈

評論