數(shù)電基礎(chǔ)

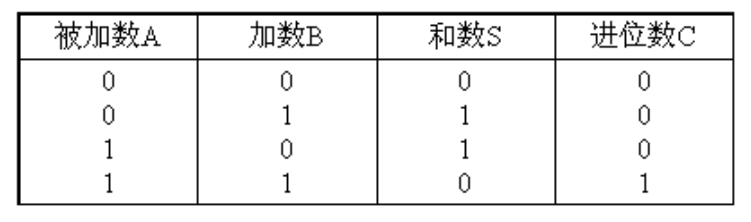

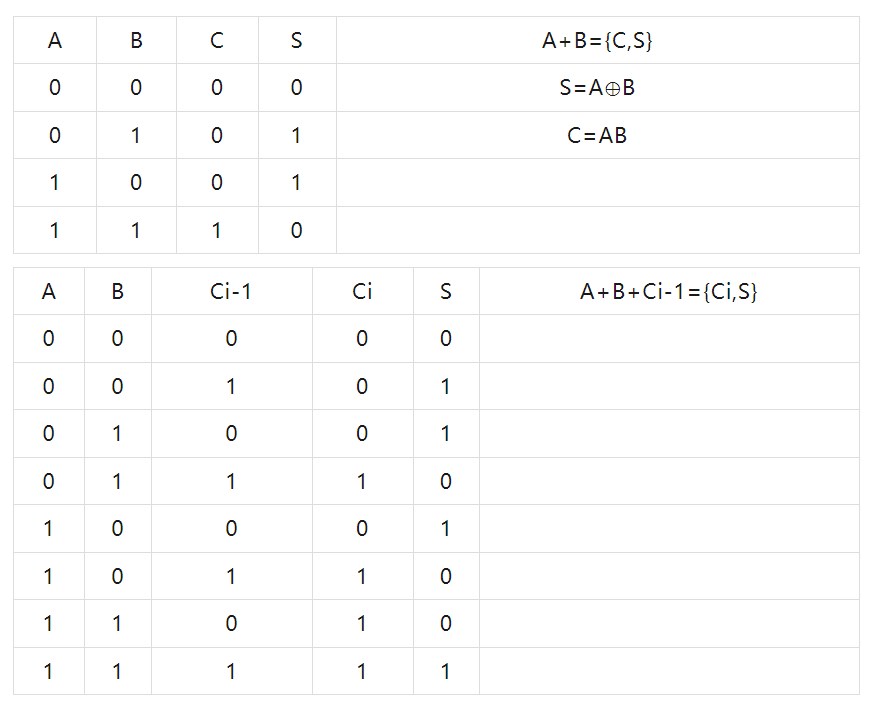

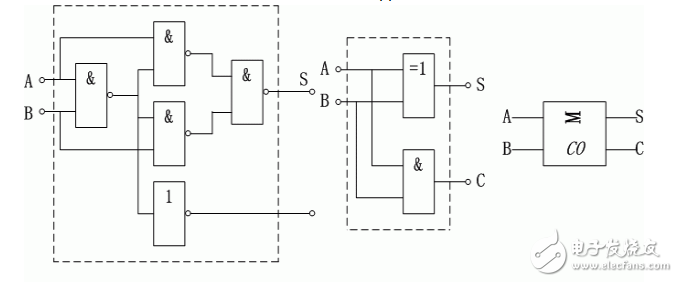

加法器用于兩個(gè)數(shù)或者多個(gè)數(shù)的加和,加法器又分為半加器(half adder)和全加器(full adder)。半加器電路是指對(duì)兩個(gè)輸入數(shù)據(jù)位相加,輸出一個(gè)結(jié)果位和進(jìn)位,沒有進(jìn)位輸入的加法器電路。是實(shí)現(xiàn)兩個(gè)一位二進(jìn)制數(shù)的加法運(yùn)算電路。而全加器除了加數(shù)和被加數(shù)之和外還要加上上一級(jí)傳進(jìn)來的進(jìn)位信號(hào)。如果沒有理解,看真值表和邏輯式就理解了。

| A | B | C | S | A+B={C,S} |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | S=A⊕B |

| 0 | 1 | 0 | 1 | C=AB |

| 1 | 0 | 0 | 1 | |

| 1 | 1 | 1 | 0 |

| A | B | Ci-1 | Ci | S | A+B+Ci-1={Ci,S} |

|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | |

| 0 | 0 | 1 | 0 | 1 | |

| 0 | 1 | 0 | 0 | 1 | |

| 0 | 1 | 1 | 1 | 0 | |

| 1 | 0 | 0 | 0 | 1 | |

| 1 | 0 | 1 | 1 | 0 | |

| 1 | 1 | 0 | 1 | 0 | |

| 1 | 1 | 1 | 1 | 1 |

全加器可看作兩個(gè)半加器和一個(gè)或門組成。

設(shè)計(jì)規(guī)劃

本例中我們實(shí)現(xiàn)最簡(jiǎn)單的半加器。這個(gè)示例中,采用兩個(gè)按鍵作為信號(hào)輸入A和B,兩個(gè)LED燈作為輸出C和S。按下按鍵為低電平,LED燈為低電平時(shí)點(diǎn)亮。需要實(shí)現(xiàn)的功能是,按下AB時(shí)CS點(diǎn)亮,按下其中一個(gè)時(shí)只有C點(diǎn)亮,都不按下時(shí)只有S點(diǎn)亮。

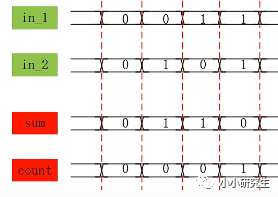

根據(jù)真值表很容易畫出波形。

編寫代碼

module half_adder

(

input wire in1 ,

input wire in2 ,

output wire sum ,

output wire cout

);

assign {cout, sum} = in1 + in2;

endmodule

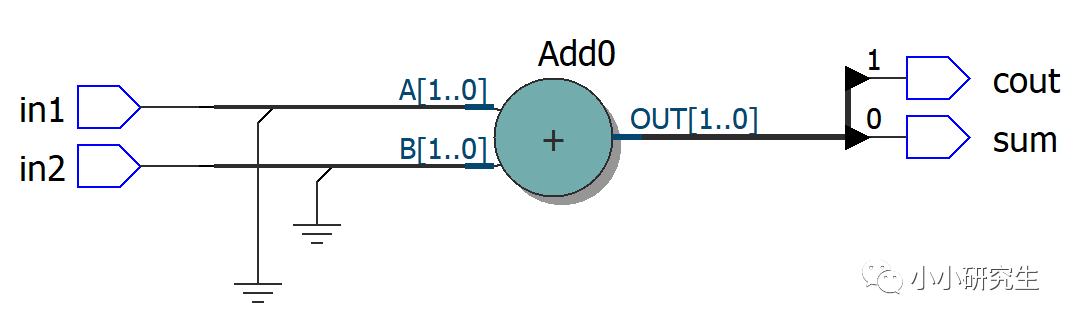

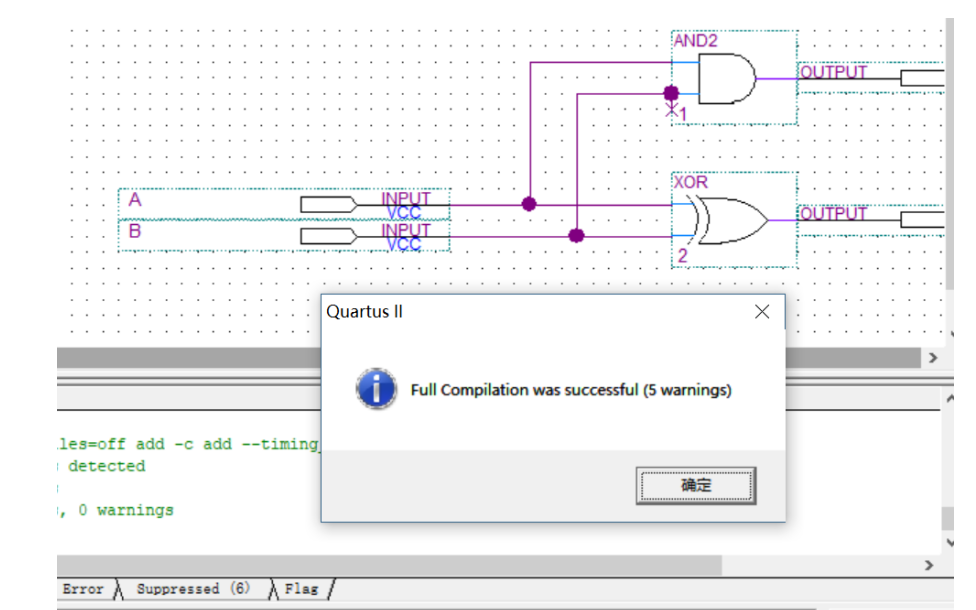

添加.v文件后編譯通過。點(diǎn)擊RTL viewer可以查看設(shè)計(jì)的硬件電路結(jié)構(gòu),和我們?cè)O(shè)計(jì)所表達(dá)的意思相同。

編寫testbench

`timescale 1ns/1ns

module tb_half_adder();

reg in1;

reg in2;

wire sum;

wire cout;

initial begin

in1 <= 1'b0;

in2 <= 1'b0;

end

always #10 in1 <= {$random} % 2;

always #10 in2 <= {$random} % 2;

//--------------------half_adder_inst-----------------

half_adder half_adder_inst

(

.in1 (in1 ), //input in1

.in2 (in2 ), //input in2

.sum (sum ), //output sum

.cout (cout ) //output cout

);

endmodule

又是超級(jí)熟悉的testbench。

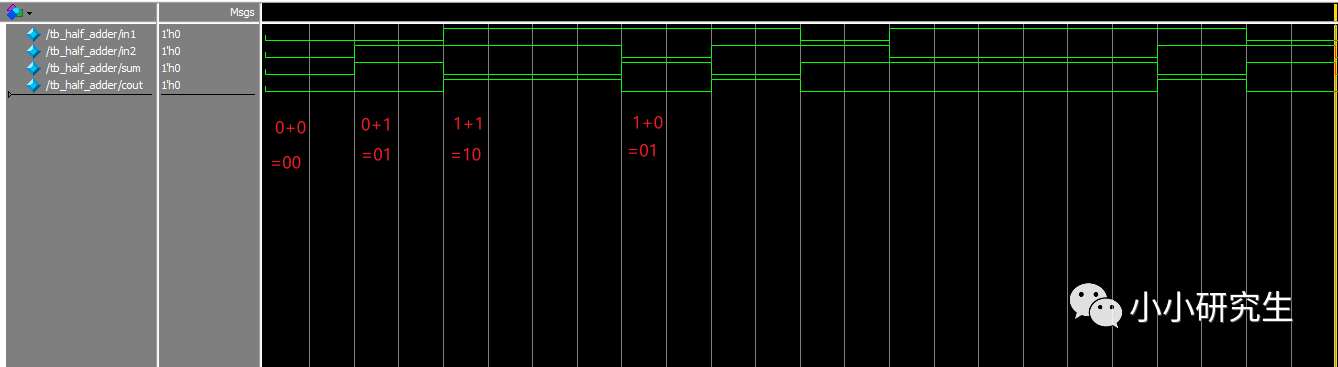

對(duì)比波形

波形與預(yù)想的一致。

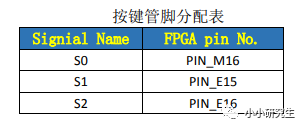

分配管腳

按照設(shè)計(jì)規(guī)劃:采用S0和S1作為信號(hào)輸入A和B,LED0和LED1作為輸出C和S。按下AB(0+0)時(shí)CS(=00)都亮,按下其中一個(gè)(0+1)時(shí)只有C(01)亮,都不按下(1+1)時(shí)只有S(=10)亮。

全編譯后上板驗(yàn)證

都不按時(shí)LED1亮

任意按一個(gè)時(shí),LED0亮。

兩個(gè)都按下時(shí),LED0和LED1都亮。

在完成這幾個(gè)實(shí)例的過程中,遇到了很多錯(cuò)誤,但是只要會(huì)上網(wǎng),把報(bào)錯(cuò)信息進(jìn)行檢索,都能圓滿解決。

-

FPGA

+關(guān)注

關(guān)注

1635文章

21837瀏覽量

608346 -

加法器

+關(guān)注

關(guān)注

6文章

183瀏覽量

30336 -

全加器

+關(guān)注

關(guān)注

10文章

62瀏覽量

28609 -

數(shù)電

+關(guān)注

關(guān)注

15文章

63瀏覽量

30124 -

半加器

+關(guān)注

關(guān)注

1文章

29瀏覽量

8844

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

半加器

最小邏輯電路 單電子半加器成功研制

全加器是什么?全加器和半加器的區(qū)別?

半加器電路原理圖資料免費(fèi)下載

基于CPLD/FPGA的半整數(shù)分頻器設(shè)計(jì)方案

半加器 半加器真值表

如何去實(shí)現(xiàn)一個(gè)半加器電路的設(shè)計(jì)呢?

基于FPGA的半加器設(shè)計(jì)

基于FPGA的半加器設(shè)計(jì)

評(píng)論