前言

本系列整理數(shù)字系統(tǒng)設(shè)計(jì)的相關(guān)知識(shí)體系架構(gòu),為了方便后續(xù)自己查閱與求職準(zhǔn)備。對(duì)于FPGA和ASIC設(shè)計(jì)中,D觸發(fā)器是最常用的器件,也可以說是時(shí)序邏輯的核心,本文根據(jù)個(gè)人的思考?xì)v程結(jié)合相關(guān)書籍內(nèi)容和網(wǎng)上文章,聊一聊D觸發(fā)器與亞穩(wěn)態(tài)的那些事。

D觸發(fā)器結(jié)構(gòu)

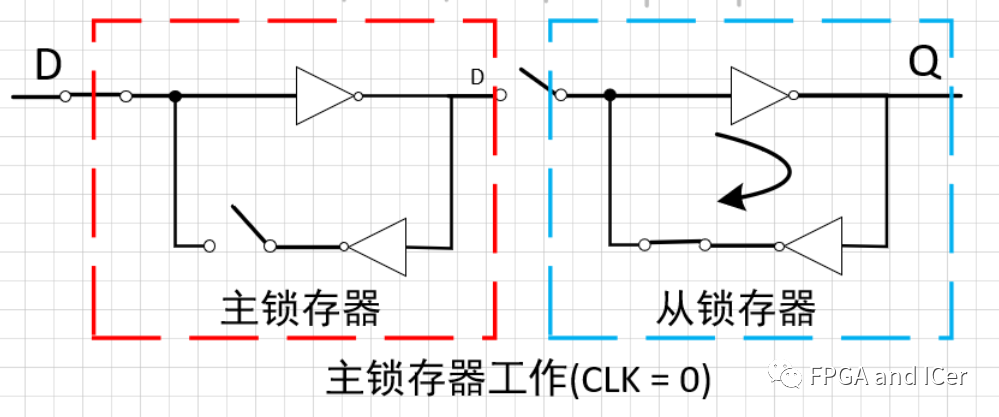

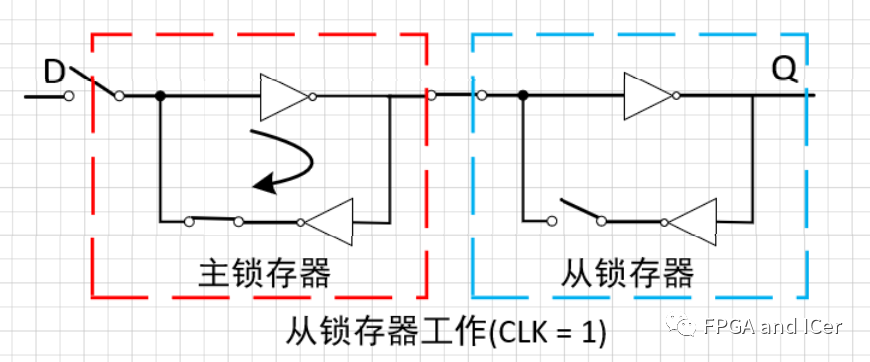

由傳輸門和兩個(gè)反相器組成一個(gè)循環(huán)電路(鎖存器),再由前后兩級(jí)鎖存器按主從結(jié)構(gòu)連接而成。分別用兩個(gè)反相時(shí)鐘控制 , 觸發(fā)器在時(shí)鐘有效沿的短期時(shí)間 “ 窗口” 采樣數(shù)據(jù)。傳輸門起開關(guān)的作用,隨著CLK的狀態(tài)變化切換開關(guān)。從輸出來看的話,前級(jí)的鎖存器的值會(huì)有序傳送給后級(jí)(隨著時(shí)鐘輸入)。

D-FF電路結(jié)構(gòu)

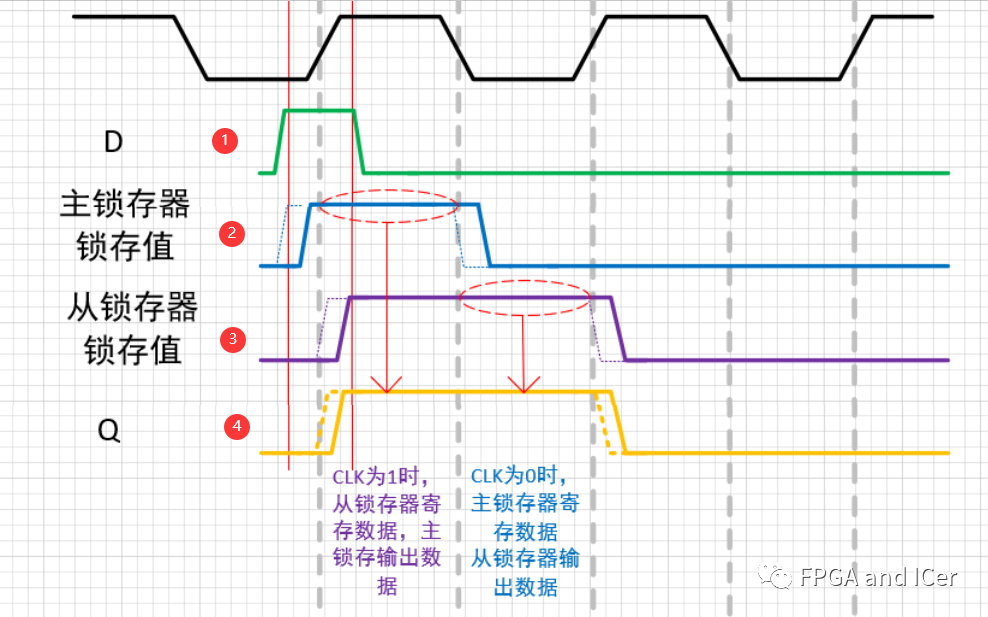

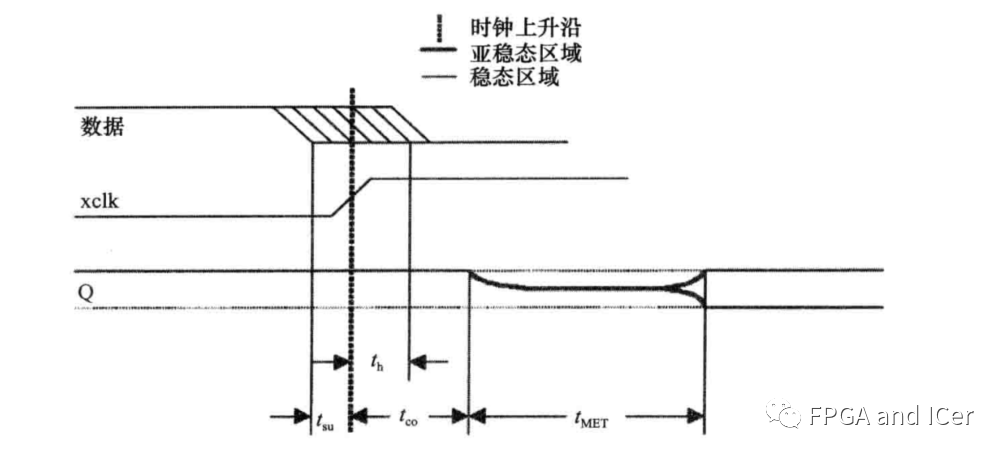

D觸發(fā)器的工作時(shí)序如下圖,圖中的D為上圖D觸發(fā)器輸入端,Q為D觸發(fā)器輸出端。此處分析并不考慮時(shí)鐘存在抖動(dòng)偏移的情況,認(rèn)為時(shí)鐘是理想的,沒有抖動(dòng)偏移的。

D觸發(fā)器工作流程

時(shí)鐘為低電平時(shí),也即主鎖存器工作時(shí),D觸發(fā)器的主鎖存器進(jìn)行鎖存,在圖中標(biāo)號(hào)1為輸入的信號(hào)。主鎖存器經(jīng)過傳輸門和反相器進(jìn)行數(shù)據(jù)寄存;此時(shí)后級(jí)的從鎖存器和前級(jí)隔開;從鎖存器輸出上一個(gè)時(shí)鐘周期的數(shù)據(jù)。

主鎖存器工作

時(shí)鐘為高電平時(shí),也即從鎖存器工作時(shí),D輸入端和主鎖存器斷開,確保數(shù)據(jù)穩(wěn)定,然后主鎖存器將數(shù)據(jù)傳輸給從鎖存器,然后輸出到Q端。

從鎖存器工作

標(biāo)號(hào)2的虛線表示理想條件下(無延時(shí))主鎖存器的鎖存邊沿,實(shí)際上主鎖存器穩(wěn)定鎖存需要時(shí)間,所以相比理想條件需要延時(shí)一段時(shí)間。標(biāo)號(hào)3的虛線表示理想條件下(無延時(shí))從鎖存器的鎖存邊沿,實(shí)際上從鎖存器穩(wěn)定鎖存需要時(shí)間,所以相比理想條件需要延時(shí)一段時(shí)間。根據(jù)主從鎖存器的輸出結(jié)果,可得到D觸發(fā)器輸出Q的波形。圖中的標(biāo)號(hào)4中的虛線表示理想條件下(無延時(shí))從鎖存器的鎖存邊沿,這里的延時(shí)是經(jīng)過傳輸門 TG3 和反相器到輸出端 Q 的延遲。

同時(shí),當(dāng)時(shí)鐘由低電平變?yōu)楦唠娖綍r(shí),涉及到了兩組傳輸門的切換,因?yàn)閷?shí)際的物理模型開關(guān)切換都是需要時(shí)間的,并且每個(gè)開關(guān)進(jìn)行開斷時(shí)都有一定的時(shí)間偏差,所以在此時(shí)D端的輸入改變就容易造成從鎖存器的鎖存錯(cuò)誤,從而造成從鎖存器的反相器環(huán)路想后級(jí)傳遞值時(shí),給出錯(cuò)誤的數(shù)據(jù)值,進(jìn)而影響功能。

與主鎖存器相關(guān)的建立時(shí)間

此時(shí)再回顧建立時(shí)間的定義,建立時(shí)間 (通常表示為tsu)指在時(shí)鐘上升沿來臨之前信號(hào)保持穩(wěn)定的最小時(shí)間。結(jié)合前面的分析,建立時(shí)間的存在意義也就是于此。在時(shí)鐘電平跳變前,主鎖存器需要穩(wěn)定鎖存我們想要的數(shù)據(jù),由于實(shí)際物理電路的延遲,需要提前一段時(shí)間進(jìn)行將數(shù)據(jù)進(jìn)行穩(wěn)定。因此,建立時(shí)間,實(shí)質(zhì)上是主鎖存器鎖存需要的時(shí)間,。

與從鎖存器相關(guān)的保持時(shí)間

再回顧保持時(shí)間的定義, 保持時(shí)間 (通常表示為th)指在時(shí)鐘上升沿來臨之后信號(hào)保持穩(wěn)定的最小時(shí)間。結(jié)合前面的分析,保持時(shí)間的存在意義也就是于此。當(dāng)時(shí)鐘進(jìn)入高電平后,由于傳輸門關(guān)斷需要一定的時(shí)間,因此輸入D必須繼續(xù)穩(wěn)定一段時(shí)間才能夠保證數(shù)據(jù)被穩(wěn)定鎖存。因此,保持時(shí)間,實(shí)質(zhì)上是傳輸門切換至從鎖存器鎖存數(shù)據(jù)需要的時(shí)間。

簡(jiǎn)單來說, 主鎖存器決定了D觸發(fā)器的建立時(shí)間,從鎖存器決定了D觸發(fā)器的保持時(shí)間 ,從上面的例子中可以很容易看到,同時(shí)說明一點(diǎn)上面的分析均基于理想時(shí)鐘的情況下,同樣的道理,時(shí)鐘的抖動(dòng)也會(huì)影響,數(shù)據(jù)正常鎖存。

亞穩(wěn)態(tài)理論引入

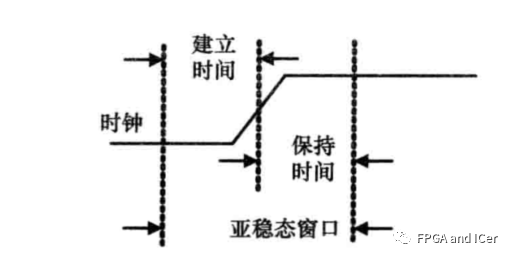

所以,根據(jù)前文D觸發(fā)器模型的分析可知,當(dāng)信號(hào)沒有滿足兩個(gè)鎖存器的鎖存時(shí)間時(shí)(也即違背了觸發(fā)器的建立和保持時(shí)間),就沒法正常的讓系統(tǒng)工作。設(shè)計(jì)中任何一個(gè)觸發(fā)器都有特定的建立和保持時(shí)間,在時(shí)鐘上升沿前后的這段時(shí)間窗口內(nèi),數(shù)據(jù)輸入信號(hào)必須保持穩(wěn)定。如果信號(hào)在這段時(shí)期發(fā)生了變化,那么輸出將是未知的。這種有害狀態(tài)的傳播就叫做 亞穩(wěn)態(tài) 。

亞穩(wěn)態(tài)窗口

因此,可以定義觸發(fā)器的建立時(shí)間和保持時(shí)間為 亞穩(wěn)態(tài)窗口 ( Metastability Window)。在亞穩(wěn)態(tài)窗口內(nèi),如果信號(hào)發(fā)生變化,輸出就可能變成亞穩(wěn)態(tài)。建立時(shí)間和保持時(shí)間共同決定亞穩(wěn)態(tài)窗口的寬度。

亞穩(wěn)態(tài)窗口

窗口越大,進(jìn)人亞穩(wěn)態(tài)的概率越高。在大多數(shù)情況下,較新的邏輯器件會(huì)有更小的亞穩(wěn)態(tài)窗口,也就意味著器件進(jìn)入亞穩(wěn)態(tài)的概率會(huì)更小。

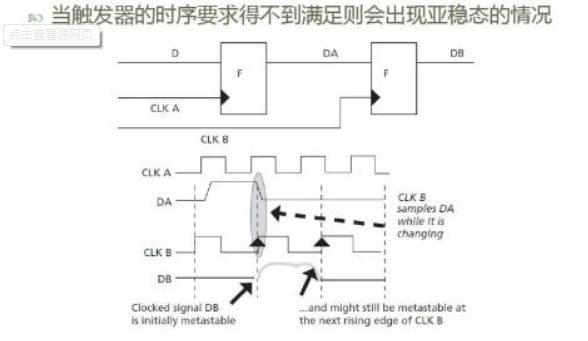

異步系統(tǒng)容易發(fā)生亞穩(wěn)態(tài)

在同步系統(tǒng)中輸入信號(hào)總是滿足觸發(fā)器的時(shí)序要求,所以不會(huì)發(fā)生亞穩(wěn)態(tài)。但是,在異步系統(tǒng)中,由于數(shù)據(jù)和時(shí)鐘的關(guān)系不是固定的,因此有時(shí)會(huì)出現(xiàn)違反建立和保持時(shí)間的現(xiàn)象。此時(shí)觸發(fā)器的輸出會(huì)因此而產(chǎn)生毛刺,或者暫時(shí)保持在不穩(wěn)定狀態(tài)而且需要較長(zhǎng)時(shí)間才能回到穩(wěn)定狀態(tài)。

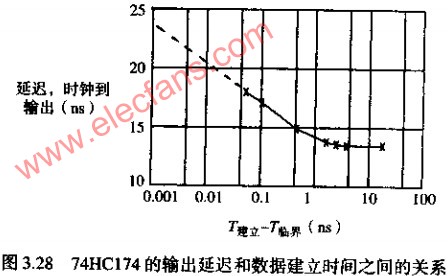

當(dāng)觸發(fā)器處在亞穩(wěn)態(tài)時(shí),輸出會(huì)在高低電平之間波動(dòng),這會(huì)導(dǎo)致延遲輸出轉(zhuǎn)換過程,并超出所規(guī)定的時(shí)鐘到輸出的延遲值(tco)。亞穩(wěn)態(tài)輸出恢復(fù)到穩(wěn)定狀態(tài)所需的超出t的額外時(shí)間部分稱為穩(wěn)定時(shí)間(tMET)。并非所有不滿足建立和保持時(shí)間的輸入變化都會(huì)導(dǎo)致亞穩(wěn)態(tài)輸出。觸發(fā)器是否進(jìn)入亞穩(wěn)態(tài)和返回穩(wěn)態(tài)所需時(shí)間取決于生產(chǎn)器件的工藝技術(shù)與外界環(huán)境。一般來說,觸發(fā)器都會(huì)在一個(gè)或者兩個(gè)時(shí)鐘周期內(nèi)返回穩(wěn)態(tài)。

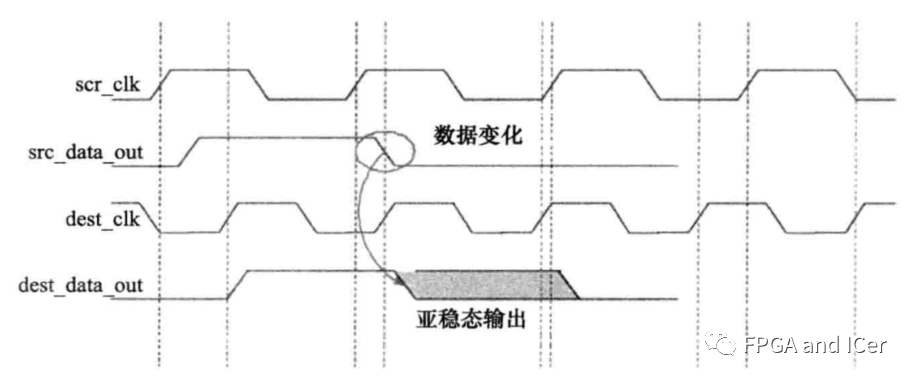

亞穩(wěn)態(tài)示例

當(dāng)信號(hào)在一個(gè)時(shí)鐘域( src_data_out)里變化,在另一個(gè)時(shí)鐘域(dest_data_in)內(nèi)采樣時(shí),就會(huì)導(dǎo)致輸出變成亞穩(wěn)態(tài)。這就是所謂的同步失敗,會(huì)導(dǎo)致邏輯功能的異常。

異步亞穩(wěn)態(tài)

平均無故障時(shí)間(MTBF)

當(dāng)系統(tǒng)的故障率恒定時(shí),MTBF ( Mean/ Average Time Between Failures,平均無故障時(shí)間)就是故障率的倒數(shù)。我們可以從中知道特定觸發(fā)器發(fā)生故障的頻率。

對(duì)于一個(gè)具有給定時(shí)鐘頻率和在該時(shí)鐘周期內(nèi)具有均勻概率密度的異步數(shù)據(jù)信號(hào)邊沿的單級(jí)同步器,亞穩(wěn)態(tài)事件的發(fā)生率可以用建立、保持時(shí)間窗口和時(shí)鐘周期的比值乘以信號(hào)觸發(fā)頻率來計(jì)算。

常數(shù)W和τ跟觸發(fā)器的電氣特性有關(guān),會(huì)根據(jù)工藝技術(shù)而改變。所以,相同工藝生產(chǎn)出來的不同器件有著相似的W和τ值。

如何盡量避免亞穩(wěn)態(tài)

每當(dāng)違背建立、保持時(shí)間時(shí),亞穩(wěn)態(tài)就會(huì)出現(xiàn),所以了解在何種情況下容易發(fā)生亞穩(wěn)態(tài),自然也就知道如何更好的避免亞穩(wěn)態(tài)。在以下條件中,信號(hào)可能違背建立時(shí)間和保持時(shí)間的要求:

- 異步信號(hào) :輸入信號(hào)是異步信號(hào)。

- 時(shí)鐘不穩(wěn)定: 時(shí)鐘偏移/擺動(dòng)(上升/下降時(shí)間)高于容限值。

- 跨時(shí)鐘域工作: 信號(hào)在兩個(gè)不同頻率或者相同頻率但是相位和偏移不同的時(shí)鐘域下跨時(shí)鐘域工作。

- 組合延遲過大 使觸發(fā)器的數(shù)據(jù)輸入在亞穩(wěn)態(tài)窗口內(nèi)發(fā)生變化。

亞穩(wěn)態(tài)會(huì)引起過多的傳輸延遲和系統(tǒng)故障,所有的觸發(fā)器和寄存器都存在亞穩(wěn)態(tài)可能。

亞穩(wěn)態(tài)不能根除,但是可以減小亞穩(wěn)態(tài)發(fā)生的概率。

在最簡(jiǎn)單的情況下,設(shè)可以通過確保時(shí)鐘周期足夠長(zhǎng)來避免亞穩(wěn)態(tài)(也即降低時(shí)鐘頻率),但這種方法很難再滿足性能的要求。另一種避免亞穩(wěn)態(tài)的方法就是使用同步器,這種同步器最好在單Bit信號(hào)的情況下使用。

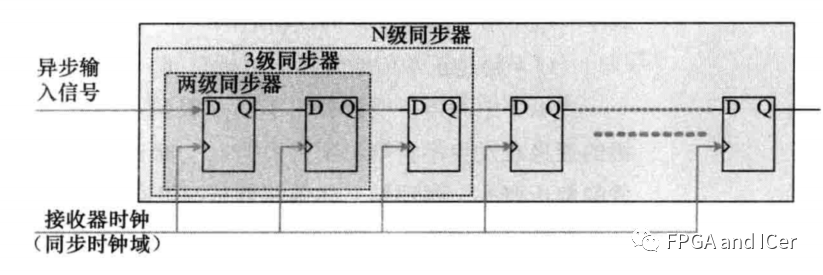

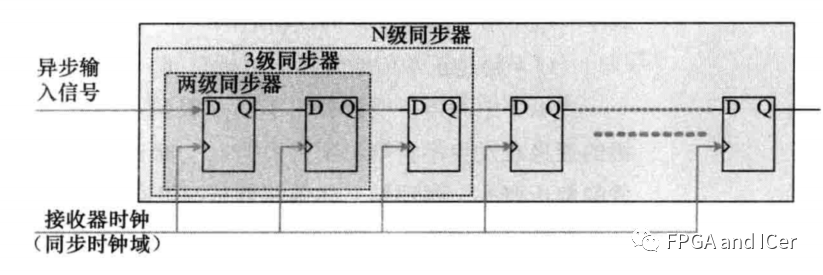

使用多級(jí)同步器

避免亞穩(wěn)態(tài)最常見的方法是在跨時(shí)鐘域的信號(hào)上加上一個(gè)或者多個(gè)同步觸發(fā)器,如下圖所示。這種方法用一個(gè)完整的時(shí)鐘周期來解決第一級(jí)同步觸發(fā)器的亞穩(wěn)態(tài)問題(不包括第二級(jí)觸發(fā)器的建立時(shí)間)。但是這種方式增加了同步邏輯輸入的延遲。

N級(jí)同步器

簡(jiǎn)而言之就是對(duì)于異步信號(hào)進(jìn)行打拍處理,這個(gè)在數(shù)字系統(tǒng)設(shè)計(jì)中很常用。

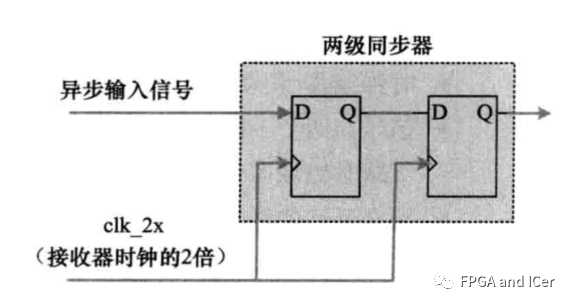

使用時(shí)鐘倍頻電路的多級(jí)同步器

多級(jí)同步器的一個(gè)局限就是系統(tǒng)需要花費(fèi)較長(zhǎng)的時(shí)間去響應(yīng)異步輸入。 解決這個(gè)問題的辦法就是使用倍頻時(shí)鐘作為兩個(gè)同步觸發(fā)器的時(shí)鐘輸入。 Altera的FPGA中具有這項(xiàng)稱為時(shí)鐘倍頻的技術(shù)。

時(shí)鐘倍頻電路的多級(jí)同步器

這種方法不僅能夠讓系統(tǒng)在一個(gè)系統(tǒng)時(shí)鐘周期內(nèi)響應(yīng)一個(gè)異步輸入,而且改善了MTBF。 盡管這種倍頻時(shí)鐘能夠降低MTBF,但是這個(gè)影響要超過兩級(jí)觸發(fā)器引起的偏移量。

兩種方法都不能保證同步器阻止亞穩(wěn)態(tài)傳播下去,它們僅僅減少了亞穩(wěn)態(tài)發(fā)生的概率。

同步器的類型

根據(jù)MTBF的計(jì)算公式 ,一個(gè)異步輸入電路的MTBF和用于從亞穩(wěn)態(tài)恢復(fù)的時(shí)間呈指數(shù)關(guān)系。 用同步器構(gòu)成的時(shí)間緩沖器可以幫助從亞穩(wěn)態(tài)中恢復(fù)。 (這里參考的是《硬件架構(gòu)的藝術(shù)》這本書,但是個(gè)人感覺翻譯的筆者可能把這段搞混掉了,如果看了原書的人,可能沒太能搞懂他說的兩種同步器,圖片和內(nèi)容在我看來好像是存在不對(duì)應(yīng)的情況,這里就依據(jù)個(gè)人理解對(duì)書中的內(nèi)容進(jìn)行勘誤)。

在《硬件架構(gòu)的藝術(shù)》這本書中介紹了兩級(jí)同步器的兩種不同的模式:模式A(慢時(shí)鐘域轉(zhuǎn)快時(shí)鐘域)和模式B(快時(shí)鐘域轉(zhuǎn)慢時(shí)鐘域)。

模式A(慢時(shí)鐘域轉(zhuǎn)快時(shí)鐘域)

模式A是一個(gè)標(biāo)準(zhǔn)的電路,當(dāng)異步輸入信號(hào)比時(shí)鐘周期大得多時(shí)最有效。 (這里根據(jù)我的個(gè)人理解他可能想表達(dá)的就是常規(guī)在目的時(shí)鐘域中打兩拍的做同步,所以我這里暫且認(rèn)定前面提到的多級(jí)同步器是他這里說的標(biāo)準(zhǔn)電路)

模式A同步器

使用在目的時(shí)鐘域打兩拍的方式作為兩級(jí)同步器,即使異步輸入在建立時(shí)間區(qū)間之外穩(wěn)定,它仍然需要由時(shí)鐘驅(qū)動(dòng)產(chǎn)生兩個(gè)周期的延遲,否則FF1可能進(jìn)入亞穩(wěn)態(tài)。 如果亞穩(wěn)態(tài)在不到一個(gè)時(shí)鐘周期內(nèi)就解析了,F(xiàn)F2就會(huì)有穩(wěn)定的輸入,否則就需要級(jí)聯(lián)更多的觸發(fā)器作為同步器。

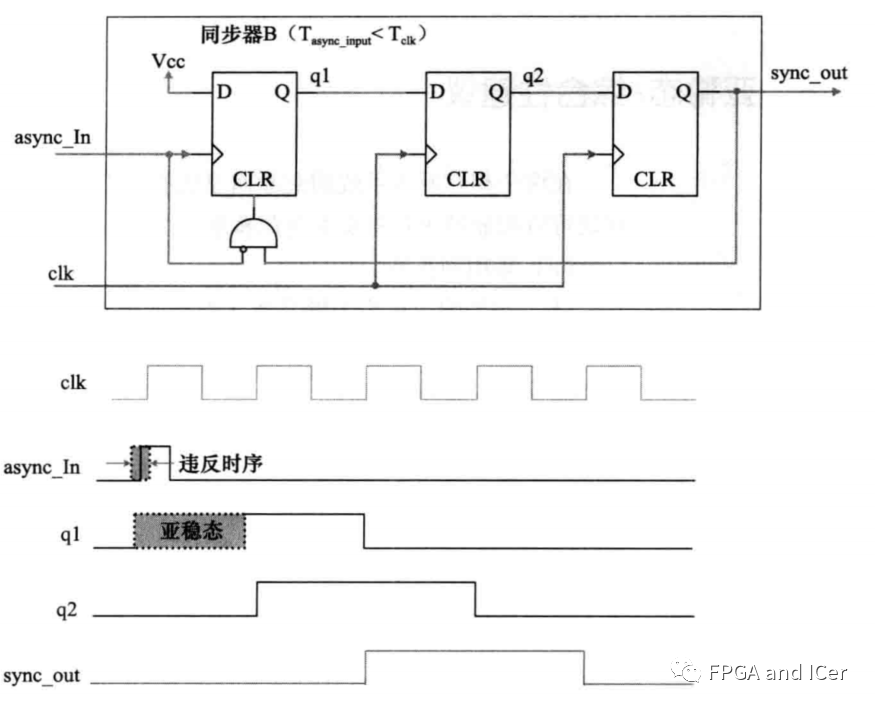

模式B(快時(shí)鐘域轉(zhuǎn)慢時(shí)鐘域)

對(duì)于同步器的模式B,第一級(jí)觸發(fā)器的輸入D與Vcc相連,同時(shí)時(shí)鐘信號(hào)是異步輸入信號(hào)。 另外兩個(gè)觸發(fā)器直接由系統(tǒng)時(shí)鐘(clk)控制。 一個(gè)短脈沖讓q1變成高電平,這個(gè)高電平在經(jīng)過兩個(gè)時(shí)鐘(clk)沿后從sync_out輸出。

模式B同步器

本節(jié)總結(jié):

- 當(dāng)信號(hào)存在跨時(shí)鐘域工作或者為異步信號(hào)時(shí),此時(shí)要采用同步器進(jìn)行同步,確保工作穩(wěn)定。

- 如果是慢時(shí)鐘域轉(zhuǎn)快時(shí)鐘域的場(chǎng)景,可以進(jìn)行打拍處理; 如果是快時(shí)鐘域轉(zhuǎn)慢時(shí)鐘域,就采用同步器的模式B。

面對(duì)亞穩(wěn)態(tài)建議

在兩個(gè)相互異步系統(tǒng)的交界面亞穩(wěn)態(tài)是不可避免的。 下面的幾點(diǎn)建議可以明顯減小亞穩(wěn)態(tài)發(fā)生的概率。

工藝器件角度:

- 采用響應(yīng)更快的觸發(fā)器(縮短亞穩(wěn)態(tài)窗口 Tw )。

- 使用亞穩(wěn)態(tài)硬化觸發(fā)器(專為高寬帶設(shè)計(jì)并且減少為時(shí)鐘域輸入電路而優(yōu)化的采樣時(shí)間)。

設(shè)計(jì)角度:

- 采用同步器。

- 使用級(jí)聯(lián)觸發(fā)器(兩個(gè)或者多個(gè))作為同步器。 如果一個(gè)觸發(fā)器的亞穩(wěn)態(tài)失敗概率為P,那么N個(gè)觸發(fā)器的亞穩(wěn)態(tài)失敗率就是P^{N}。

- 減少采樣速率,或者說降低時(shí)鐘頻率。

- 避免使用dV/dt低的輸入信號(hào)(電壓突變較慢的輸入信號(hào))。

小思與總結(jié)

本文針對(duì)前面D觸發(fā)器的分析沒有進(jìn)行考慮時(shí)鐘的偏移情況,相關(guān)內(nèi)容在后續(xù)介紹時(shí)序約束時(shí)進(jìn)行整理; 同時(shí)本文的同步方法建議在單Bit信號(hào)進(jìn)行使用,多Bit信號(hào)或者單Bit信號(hào)處理的其他方法待后續(xù)進(jìn)行整理。

為什么多Bit信號(hào)不能使用文中的同步器方式呢? 在《硬件架構(gòu)的藝術(shù)》書中提到了這樣一句話:一個(gè)異步信號(hào)不應(yīng)該被兩個(gè)或者多個(gè)同步器所同步,這樣做會(huì)存在多個(gè)同步器輸出產(chǎn)生不同信號(hào)的風(fēng)險(xiǎn)。 這大概也就是這個(gè)問題的答案,具體分析將在后面關(guān)于跨時(shí)鐘處理的文章中進(jìn)行整理解答,筆者水平有限,如有錯(cuò)誤,歡迎討論。

-

FPGA

+關(guān)注

關(guān)注

1643文章

21940瀏覽量

613294 -

FPGA設(shè)計(jì)

+關(guān)注

關(guān)注

9文章

428瀏覽量

27097 -

反相器

+關(guān)注

關(guān)注

6文章

315瀏覽量

43998 -

D觸發(fā)器

+關(guān)注

關(guān)注

3文章

165瀏覽量

48467 -

亞穩(wěn)態(tài)

+關(guān)注

關(guān)注

0文章

47瀏覽量

13459

發(fā)布評(píng)論請(qǐng)先 登錄

xilinx資料:利用IDDR簡(jiǎn)化亞穩(wěn)態(tài)

FPGA觸發(fā)器的亞穩(wěn)態(tài)認(rèn)識(shí)

fpga亞穩(wěn)態(tài)實(shí)例分析

在FPGA復(fù)位電路中產(chǎn)生亞穩(wěn)態(tài)的原因

FPGA--中復(fù)位電路產(chǎn)生亞穩(wěn)態(tài)的原因

新建兩個(gè)D觸發(fā)器的目的是什么

如何測(cè)量亞穩(wěn)態(tài)

關(guān)于FPGA設(shè)計(jì)中的亞穩(wěn)態(tài)及其緩解措施的分析和介紹

什么是單穩(wěn)態(tài)觸發(fā)器_單穩(wěn)態(tài)觸發(fā)器特點(diǎn)以及構(gòu)成

單穩(wěn)態(tài)觸發(fā)器有哪些_單穩(wěn)態(tài)觸發(fā)器工作原理介紹

如何解決觸發(fā)器亞穩(wěn)態(tài)問題?

簡(jiǎn)述FPGA中亞穩(wěn)態(tài)的產(chǎn)生機(jī)理及其消除方法

D觸發(fā)器與亞穩(wěn)態(tài)的那些事

評(píng)論