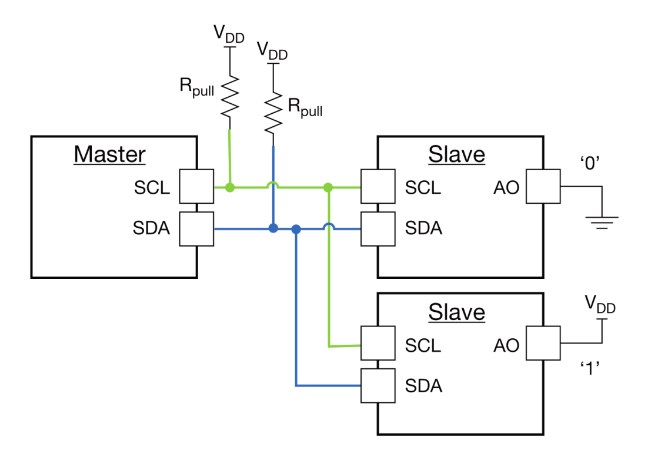

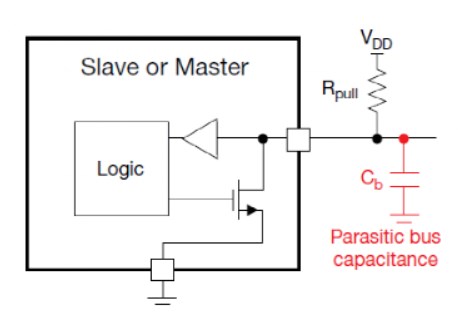

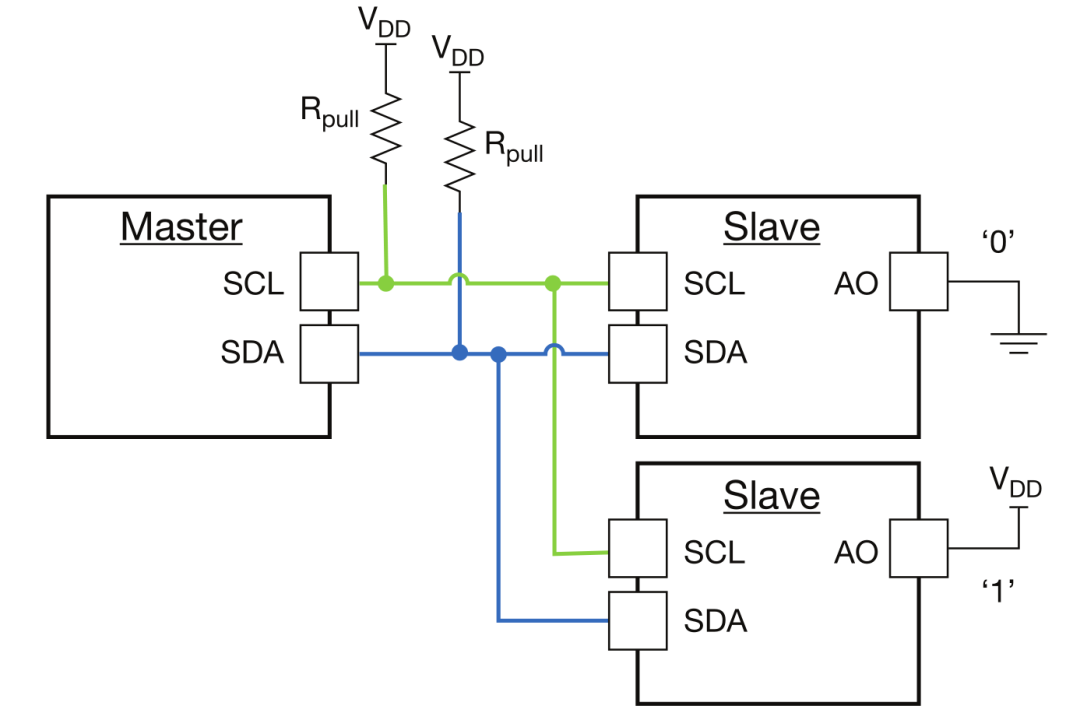

IIC(Inter-Integrated Circuit)的硬件連接

1 對于IIC主機總線上是可以掛1個或者多個從機設(shè)備。

2 每個從機是通過其各自的地址來識別。

IIC的數(shù)據(jù)和控制線(SDA和SCL)

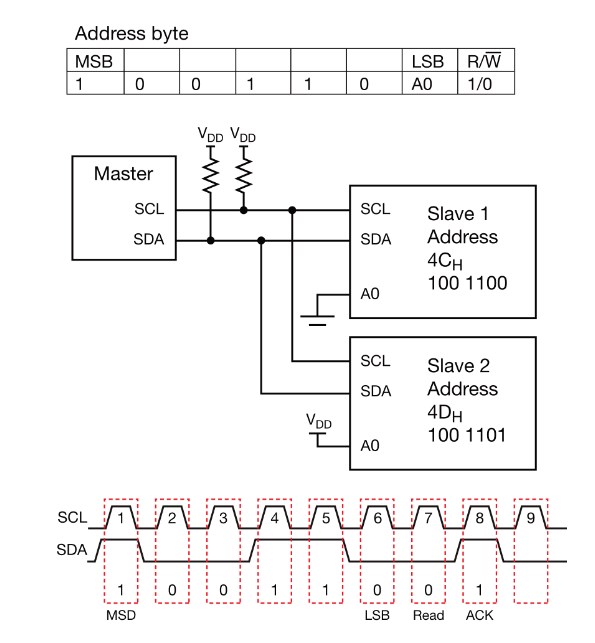

1 SCL(Serial clock),時鐘線,用于同步數(shù)據(jù)傳輸時序,是一個方波,由主機來驅(qū)動,其決定了數(shù)據(jù)傳輸?shù)目炻?/p>

2 SDA(Serial data),數(shù)據(jù)線,用于傳輸數(shù)據(jù),

IIC尋址

1 通常對于一個7bit的地址,包含1個額外的讀寫位。

2 對于IIC總線上的每一個設(shè)備都有一個獨立的地址。

3 重復(fù)的地址會導(dǎo)致通訊錯誤。

4 對于一些設(shè)備會有PIN管腳用來配置不同的IIC地址。

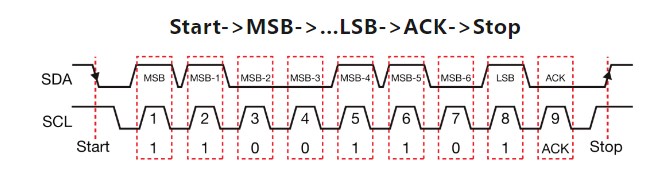

IIC通訊

START,起始位,由主機初始化,SCL高的時候拉低SDA。

STOP,停止位,SCL高的時候,主機釋放SDA PIN腳。

ACK(acknowledge),每一次傳輸一個單字節(jié)或者8bits之后,會跟一個SCL的脈沖,這個acknowledge信號是從機應(yīng)答主機的信號,表示ACK信號之前的那個字節(jié)通訊是成功的。

如下是一個標準的IIC寫時序:

Start->MSB->…LSB->ACK->Stop

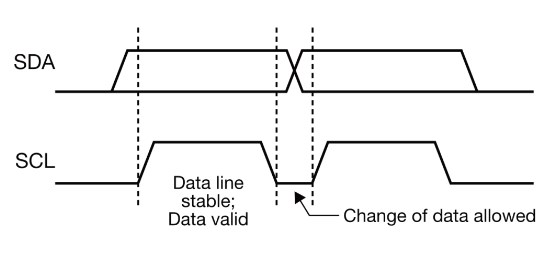

對于有效數(shù)據(jù)傳輸:

1 在時鐘信號SCL為高的整個脈寬內(nèi)SDA必須保持穩(wěn)定。

2 只有在SCL脈沖為低的時候,SDA才被允許高低切換,如果SDA在SCL為高的時候變化,則會被認為是Start/Stop。

IIC的電路設(shè)計

1 對于3.4Mbps速率以下的IIC,是漏極開路(Open Drain)的結(jié)構(gòu),此時需要外部上拉電阻,上拉電阻的選擇需要考慮上拉之后的rise/fall的時間是否滿足其時序要求同時也需要考慮功耗。上拉電阻越大,功耗越小,但rise/fall時間越長,會影響通訊;上拉電阻越小,功耗越大,但rise/fall時間短,會降低通訊的誤碼率。

2 對于3.4Mbps速率以上的IIC,其是推挽(Push Pull)的結(jié)構(gòu),其rise/fall的時間就完全取決于主機/從機設(shè)備內(nèi)部的push/pull的能力。需要注意的是,不同設(shè)備之間的通訊需要選擇同樣結(jié)構(gòu)的IIC。

-

上拉電阻

+關(guān)注

關(guān)注

5文章

363瀏覽量

30680 -

SDA

+關(guān)注

關(guān)注

0文章

124瀏覽量

28195 -

SCL

+關(guān)注

關(guān)注

1文章

239瀏覽量

17121

發(fā)布評論請先 登錄

相關(guān)推薦

關(guān)于MOS管的基礎(chǔ)知識

嵌入式網(wǎng)絡(luò)協(xié)議棧基礎(chǔ)知識

介紹嵌入式網(wǎng)絡(luò)協(xié)議棧基礎(chǔ)知識

CAN協(xié)議基礎(chǔ)知識

網(wǎng)絡(luò)協(xié)議基礎(chǔ)知識

FPGA基礎(chǔ)知識之IIC協(xié)議讀寫解析

講講關(guān)于IIC通訊協(xié)議的基礎(chǔ)知識

講講關(guān)于IIC通訊協(xié)議的基礎(chǔ)知識

評論