一、 說明

以前總是沒有記錄的習慣,導致遇到問題時總得重新回憶與摸索,大大降低了學習效率,從今天開始決定改掉這個壞毛病,認真記錄自己的Verilog學習之路,希望自己能一直堅持下去。

二、 軟件資源與硬件資源

軟件資源說明:

1、UltraEdit:本博客所有的Verilog代碼全部都在UltraEdit中編輯, UltraEdit具有語法高亮與自動補全(設置方法在本文最后面)功能,而且界面美觀,絕對是寫代碼的利器。

2、ISE14.7或Vivado2016.3:本博客的FPGA選擇的是Xilinx的,所以選擇Xilinx集成開發套件,本來之前一直在用7系列的FPGA,但是目前手頭只有一塊Spartan-6系列的二手開發板,所以代碼的驗證都在Spartan-6上驗證,但好在FPGA的結構基本類似,Verilog的代碼基本可以通用。

3、ModelSim-win64-10.4-se:仿真工具使用ModelSim 10.4版本,其他版本也可以,無過多要求。

4、Windows-7 64-bit系統:建議大家在Windows-7 64-bit系統做開發 ,Windows-7 64-bit系統對以上軟件的兼容性都比較好。我的筆記本電腦用的是Windows-8.1系統,安裝ISE14.7以后導入ModelSim仿真庫,選擇庫目錄的時候出現了卡住的情況,這種就是ISE14.7與WIndows-8.1不太兼容導致的,解決辦法如下。

解決Windows-8.1與ISE14.7不兼容的辦法:

找到ISE安裝目錄的中的nt64文件夾,我的ISE的安裝目錄在D盤,所以nt64的路徑如下D:Xilinx14.7ISE_DSISElib t64,然后把nt64文件夾中的libPortability.dll文件名改成libPortability.dll.org,再把libPortabilityNOSH.dll重命名為libPortability.dll。這樣可以有效解決一部分兼容性的問題。

5、更多軟件資源可以關注文末的微信公眾號并輸入關鍵字“軟件安裝包”獲取

硬件資源說明:

1、目前手頭只有一塊二手的黑金AX545開發板,FPGA的型號是:XC6SLX45-2CSG324,所以代碼都會在這個板子上進行驗證。對于其他型號的FPGA只要理解原理了應該也不難上手。

三、 Verilog命名規范與格式說明

Verilog語言并沒有固定的命名規范與編寫格式,每個人根據自己的喜好而定就行了,我自己比較喜歡下面規范與格式。這里先寫一部分,后面如果有補充的在加上。

Verilog命名規范:

1、所有輸入端口以大寫I加下劃線開始,然后后面內容的一律用小寫,信號比較長的話,后面的小寫用下劃線隔開。如:

input I_clk;

input I_led_mode;

如果輸入端口低電平有效的話就在末尾加下劃線和小寫n,如:

input I_rst_n;

2、所有輸出端口以大寫O加下劃線開始,然后后面內容的一律用小寫,信號比較長的話,后面的小寫用下劃線隔開。如:

output O_led;

output O_led_mode;

3、所有reg變量以大寫R加下劃線開始,然后后面內容的一律用小寫,信號比較長的話,后面的小寫用下劃線隔開。如:

reg R_cnt;

reg R_cnt_100ms;

4、所有wire變量以大寫W加下劃線開始,然后后面內容的一律用小寫,信號比較長的話,后面的小寫用下劃線隔開。如:

wire W_cnt;

wire W_led_mode;

5、所有常量(parameter變量)以大寫C加下劃線開始,然后后面內容的一律用大寫以示與變量的區別,信號比較長的話,后面的大寫用下劃線隔開。如:

parameter C_IDLE;

parameter C_FLASH_READ;

6、命名一定要有意義,看著變量名就大概能猜出它的作用,并適當采用縮寫,下面幾個縮寫是寫代碼過程中比較常用的縮寫。

‘rd’代替‘read’

‘wr’代替‘write’

‘cnt’代替‘count’

‘rst’代替‘reset’

‘addr’代替‘address’

Verilog編寫格式:

1、always塊的begin…end換行寫,如:

always @(posedge I_clk or negedge I_rst_n)

begin

…

end

2、if…else if…else語句的begin…end換行并空一個Tab鍵(記得設置一個Tab為4個空格)寫,如果if或者else下面只有一條語句那么就省略begin…end如:

if

begin

…

end

else if

begin

…

end

else

…

3、case…endcase語句中的條件后面如果只有一條語句,則直接在冒號后面寫語句,default一定要寫上,即使里面什么語句也沒有。最好用UltraEdit的列模式功能把那些冒號和分號都上下對齊。如

case(...)

C_IDEL : …… ;

C_FLASH : …… ;

default : ;

endcase

case…endcase語句中的條件后面如果有多條語句,則直接在冒號后面換行加Tab鍵寫begin…end。同樣用UltraEdit的列模式功能把那些冒號和分號都上下對齊。

case(R_state)

C_IDEL :

begin

…… ;

end

C_ FLASH :

begin

…… ;

end

default :

begin

…… ;

end

endcase

4、例化模塊的時候例化名就是在模塊名前面加一個大寫的U和下劃線,并且用UE的列模式功能把括號和逗號都對齊。如:

led_work U_ led_work

(

. I_clk (I_clk ),

. I_rst_n (I_rst_n ),

.O_led_mode (O_led_mode ),

.O_led_out (O_ led_out )

);

附、 UltraEdit設置方法

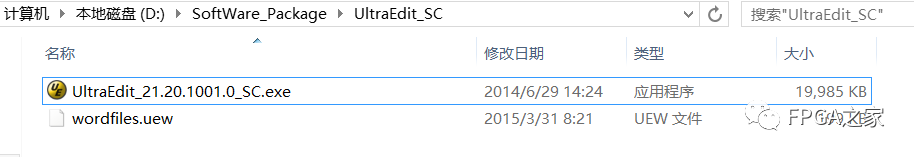

下載上文的UltraEdit壓縮包并解壓,里面有兩個文件,一個是UE的安裝包,一個是語法高亮文件

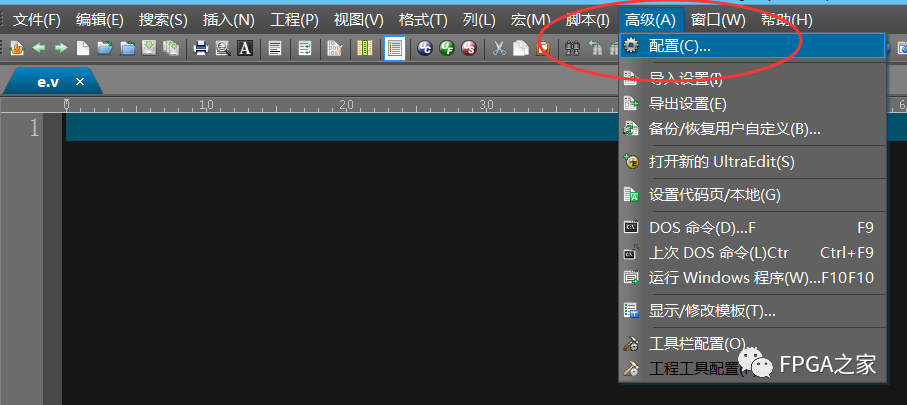

雙擊exe文件安裝好了以后打開UE會提示選擇風格,我比較喜歡黑暗風格,選完風格以后在菜單欄找到高級選項卡,然后在高級選項卡下載找到配置菜單

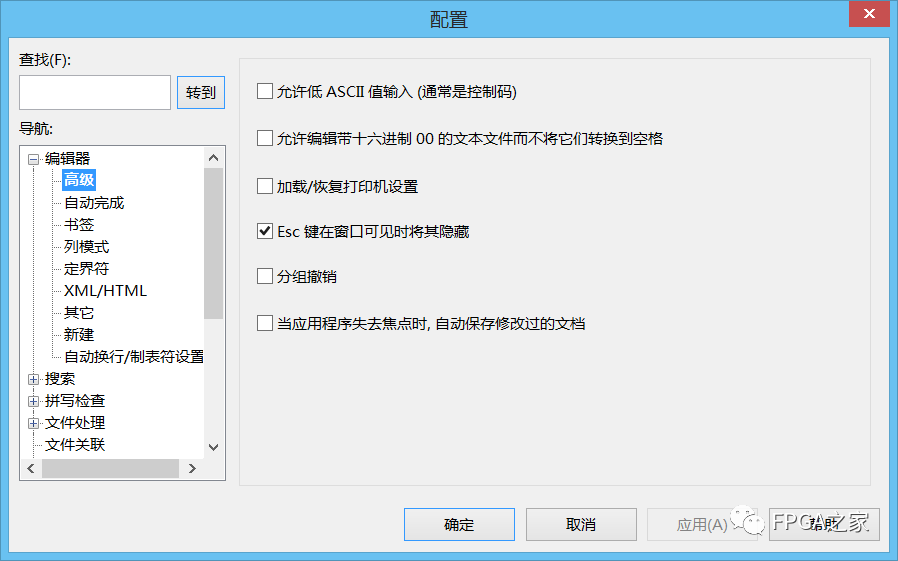

單擊配置菜單,彈出如下界面

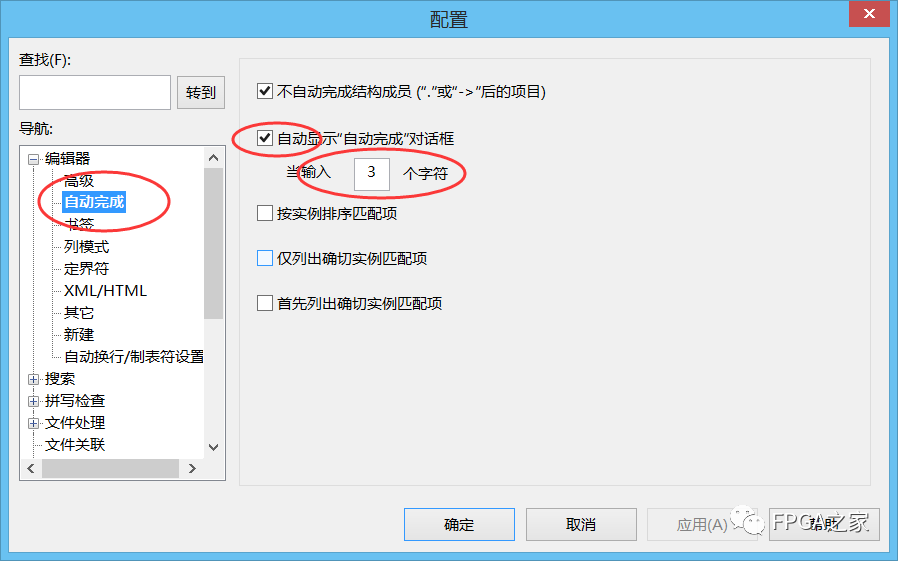

接著在上面的界面中找到自動完成功能并選中,然后按照下圖進行設置

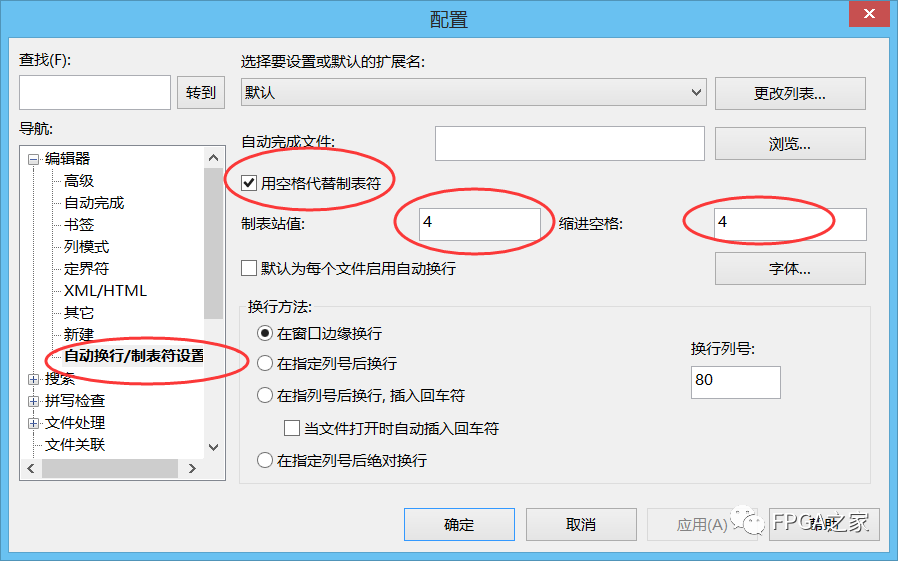

接著在找到自動換行/制表符設置,按照如下方式設置

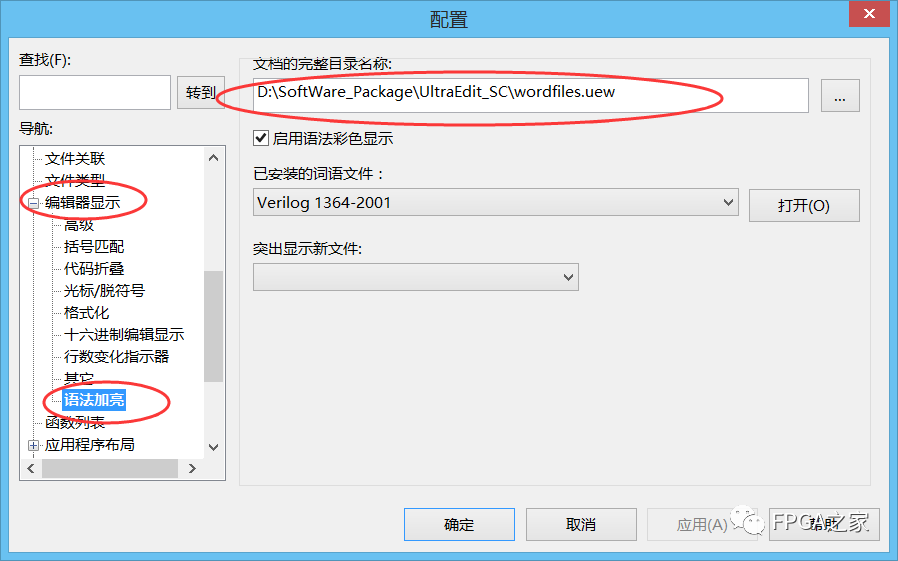

最后找到編輯器顯示下面的語法加亮,選擇安裝包中的wordfile.uew配置文件就OK了,如下圖所示

審核編輯:湯梓紅

-

Xilinx

+關注

關注

71文章

2167瀏覽量

121304 -

軟件

+關注

關注

69文章

4921瀏覽量

87398 -

Verilog

+關注

關注

28文章

1351瀏覽量

110074 -

開發板

+關注

關注

25文章

5032瀏覽量

97373 -

代碼

+關注

關注

30文章

4779瀏覽量

68524

原文標題:【接口時序】1、軟件與Verilog基本格式規范說明

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

軟件與Verilog基本格式規范說明

軟件與Verilog基本格式規范說明

評論