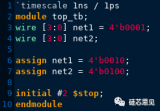

寫(xiě)過(guò)Verilog和systemverilog的人肯定都用過(guò)系統(tǒng)自定義的函數(shù)$display,這是預(yù)定好的,可以直接調(diào)用的功能。但是當(dāng)Verilog中的task和function不能滿足仿真需求時(shí),這就需要自定義一些任務(wù)和函數(shù)。

Verilog中使用編程語(yǔ)言接口PLI(Program Language Interface)編程語(yǔ)言接口來(lái)和C語(yǔ)言程序交互,它提供了一套C語(yǔ)言函數(shù),我們可以調(diào)用這些集成函數(shù)編寫(xiě)軟件C程序。RTL代碼編譯的時(shí)候,這些軟件C程序也會(huì)集成到仿真環(huán)境中。仿真運(yùn)行后,使用系統(tǒng)任務(wù)調(diào)用的方式,就可以去訪問(wèn)仿真中的數(shù)據(jù)結(jié)構(gòu),也就是說(shuō)PLI提供一個(gè)使得用戶自帶C函數(shù)能夠在運(yùn)行時(shí)間訪問(wèn)仿真數(shù)據(jù)結(jié)構(gòu)的接口。

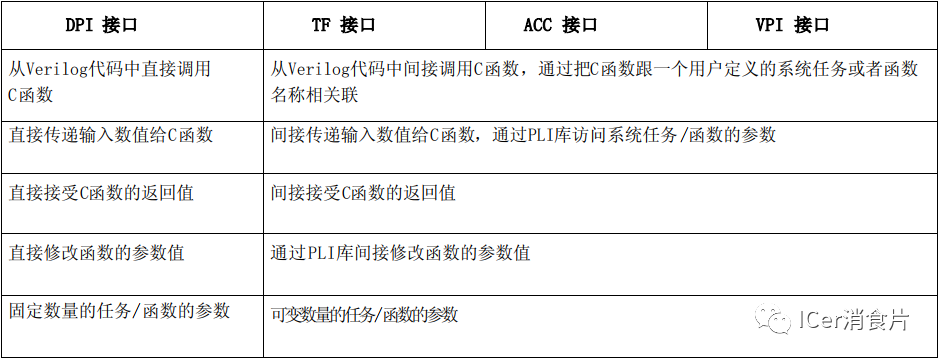

PLI先后經(jīng)歷了3代的發(fā)展: 1985年TF Task/Function interface,第一代VerilogPLI。包含一整套C語(yǔ)言函數(shù)庫(kù),函數(shù)定義在verisuer.h文件中,一般稱為TF子程序,主要作用是把任務(wù)/函數(shù)參數(shù)傳遞給C函數(shù)。TF的缺點(diǎn)是它定義系統(tǒng)任務(wù)/函數(shù),函數(shù)返回值以及需要關(guān)聯(lián)任務(wù)/函數(shù)名稱到C函數(shù)的機(jī)制。該機(jī)制并不是標(biāo)準(zhǔn)化的, 這就意味著每個(gè)仿真器有不同的PLI接口機(jī)制。TF的一個(gè)缺點(diǎn)是定義系統(tǒng)任務(wù)/函數(shù)名稱、函數(shù)返回類型以及與任務(wù)/函數(shù)名稱相關(guān)聯(lián)的 C函數(shù)的機(jī)制。這種機(jī)制不是標(biāo)準(zhǔn)化的,這意味著每個(gè)模擬器都有不同的 PLI 接口機(jī)制。 1

989年ACC Access interface,第二代VerilogPLI。引入了訪問(wèn)程序庫(kù)的C函數(shù),即ACC函數(shù)庫(kù),由單獨(dú)的acc_user.h定義,函數(shù)均以acc_作為前綴。它是作為TF的附加庫(kù)。只是增加了搜索仿真數(shù)據(jù)結(jié)構(gòu)的功能,但是不能訪問(wèn)RTL和行為級(jí)的設(shè)計(jì)部分。此外,復(fù)雜的,因仿真器而異的接口機(jī)制也是ACC接口的一大缺點(diǎn)。

1995年VPI Verilog Programming Interface,第三代Verilog PLI。VPI是TF和ACC的超集擴(kuò)展庫(kù)。VPI庫(kù)定義在C函數(shù)庫(kù)文件vpi_user.h。使用VPI, 用戶能夠訪問(wèn)整個(gè)仿真數(shù)據(jù)結(jié)構(gòu), 包括系統(tǒng)任務(wù)/函數(shù)的參數(shù)(替換TF) 以及設(shè)計(jì)的層次結(jié)構(gòu)單元(替換ACC)。

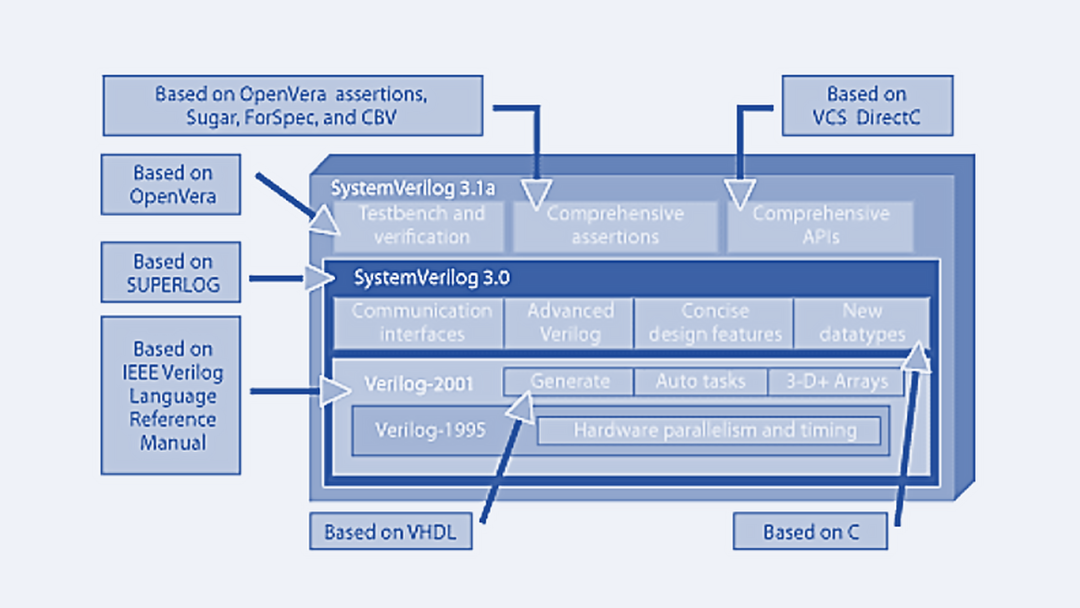

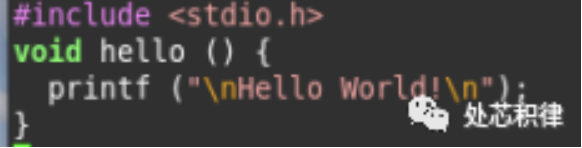

DPI的發(fā)展相對(duì)來(lái)說(shuō)比較緩慢 Accellera在2003年4月發(fā)布了包括DPI在內(nèi)的SystemVerilog 3.1標(biāo)準(zhǔn),隨后在3.1A版本中進(jìn)一步對(duì)DPI進(jìn)行了加強(qiáng)。systemverilog中使用DPI(Direct Programming Interface),更加簡(jiǎn)單地連接C、C++或者其他的非Verilog語(yǔ)言。你只需要使用import語(yǔ)句把C函數(shù)導(dǎo)入到,就可以像調(diào)用systemverilog的子程序一樣來(lái)使用它。使用DPI, 用戶無(wú)需再像Verilog PLI那樣, 事先編寫(xiě)系統(tǒng)任務(wù)/函數(shù)名稱,然后通過(guò)復(fù)雜的PLI庫(kù)間接傳遞數(shù)值回C函數(shù)。但是DPI不能直接訪問(wèn)仿真數(shù)據(jù)結(jié)構(gòu)的內(nèi)部,這限制了DPI的應(yīng)用。

SystemVerilog DPI和Verilog PLI的比較

DPI絕不是為了替代PLI,而是彌補(bǔ)PLI中的不足,相信不久的未來(lái)能出現(xiàn)一個(gè)新的PI標(biāo)準(zhǔn)更好得結(jié)合兩者的優(yōu)點(diǎn)。

審核編輯:劉清

-

Verilog

+關(guān)注

關(guān)注

28文章

1351瀏覽量

110077 -

C語(yǔ)言

+關(guān)注

關(guān)注

180文章

7604瀏覽量

136705 -

RTL

+關(guān)注

關(guān)注

1文章

385瀏覽量

59763 -

DPI

+關(guān)注

關(guān)注

0文章

36瀏覽量

11509

原文標(biāo)題:從Verilog PLI到SystemVerilog DPI的演變

文章出處:【微信號(hào):處芯積律,微信公眾號(hào):處芯積律】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

buck電路原理圖講解 buck電路的演變過(guò)程

數(shù)字式稱重傳感器的功能演變過(guò)程

【視頻分享】降壓電路的演變過(guò)程

The Verilog PLI Handbook

Verilog手冊(cè)的公眾責(zé)任

從產(chǎn)品的演變過(guò)程看KVM行業(yè)的發(fā)展

定位技術(shù)的演變過(guò)程

升壓變換器二種結(jié)構(gòu)的演變過(guò)程資料下載

使用Verilog/SystemVerilog硬件描述語(yǔ)言練習(xí)數(shù)字硬件設(shè)計(jì)

解碼國(guó)產(chǎn)EDA數(shù)字仿真器系列之二 | 如何實(shí)現(xiàn)全面的SystemVerilog語(yǔ)法覆蓋?

談?wù)?b class='flag-5'>Verilog/System Verilog和C的幾種交互模式

verilog/systemverilog中隱藏的初始化說(shuō)明

buck電路的演變過(guò)程

淺析can技術(shù)的演變過(guò)程

從Verilog PLI到SystemVerilog DPI的演變過(guò)程

從Verilog PLI到SystemVerilog DPI的演變過(guò)程

評(píng)論