一.封裝

前幾期曾經講過,對封裝后的芯片進行CDM測試,大量非平衡載流子會通過金線集聚到封裝框架中。所以封裝也是影響CDM的關鍵因素之一,恰宜的封裝能大幅度提升芯片的CDM防護等級。(筆者對于封裝還是才疏學淺,這里就不多做筆墨了。)

二.片內防護

CDM是一種自發性的,從內到外的ESD事件。所以其波形參數并不固定,雖然CDM的瞬態電流峰值很高,但是持續時間短,脈沖能量低。其防護電力路的設計思路與HBM還是有一定差異。CDM與HBM防護設計的主要區別有:

因為放電機理不同,CDM防護設計與HBM防護設計的側重點不一,HBM側重于過電流能力,同時需要設計合理的Design Window,而CDM側重于瞬態特性,CDM很少關注Design Window和過電流能力。

防護部位不一,HBM會對MOS的源,漏,柵;隔離環;輸入電阻等都會造成損壞,而CDM的只會對MOS管的柵極造成破壞。

失效機理差異,HBM波形雖然峰值電流低,但是其持續時間長,放電功率大,HBM設計需要將電學特性與熱電特性相結合。反觀CDM,因為其總能量很低,只需要關注其高頻脈沖特性。

相較于HBM,CDM防護的設計目標更加明確,但是因為其較高的頻率和由內而外的機制,所以設計難度也高一些(越先進的制程CDM設計越難)。本文針對CDM的設計從全片ESD策略,布局布線,器件特性的角度進行分析。

2.1 全片防護策略

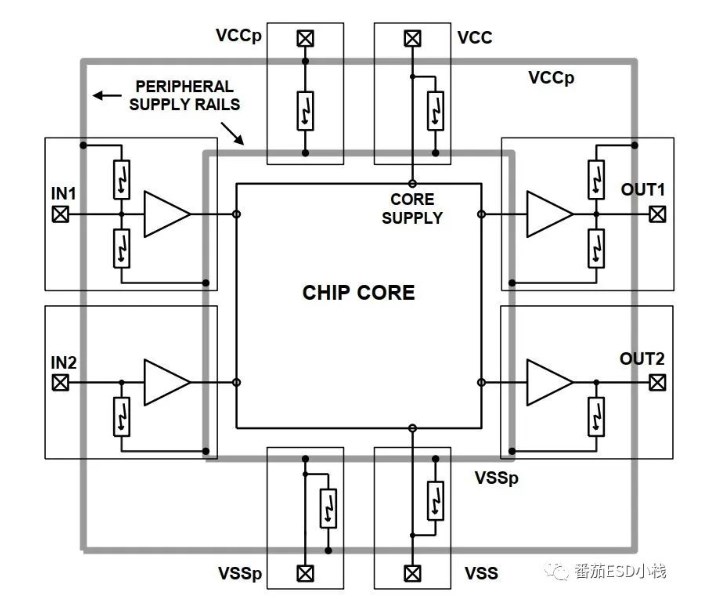

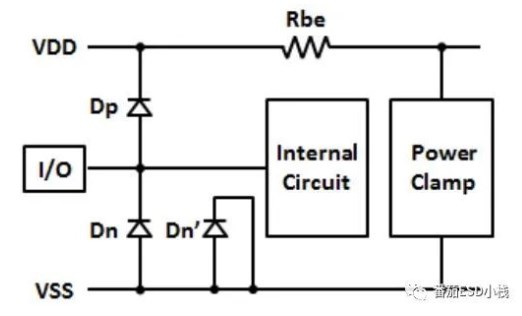

目前全片ESD防護策略大致分為兩種:一種是Pad-Based;一種是Rail-Based。兩種策略的區別在于觸發機制,Pad-Based是利用寄生器件的反向擊穿/正向導通特性,構建從Pad到Power Rail的雙向ESD通路,在Pad端實現ESD泄放,所以Pad-Based策略屬于電壓觸發。GGNMOS,SCR,二極管串,都屬于Pad-Based型ESD防護器件。

圖一.Pad-Based 電路結構。

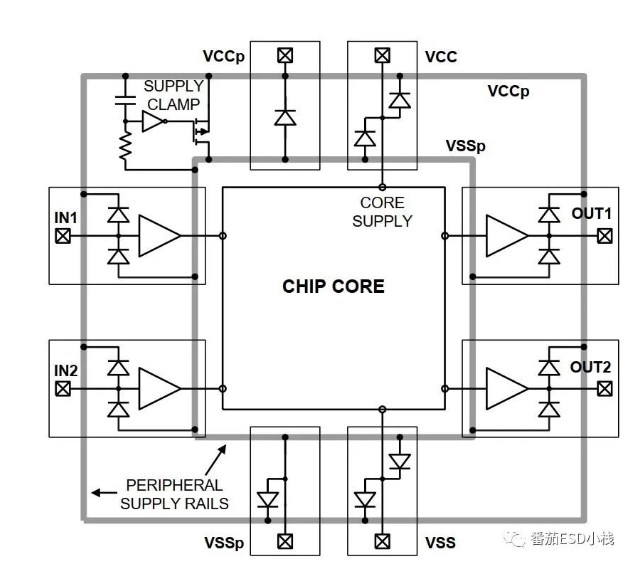

Rail-Based是利用二極管的正向導通特性,將ESD電流先行從端口轉移到Power Rail,再利用RC電路的頻率觸發特性,利用響應柵壓開啟BigMOS,將Power Rail上的ESD電流通過MOS泄放。實現了Rail to Rail的ESD泄放。

圖二.Rail-Based 電路結構。

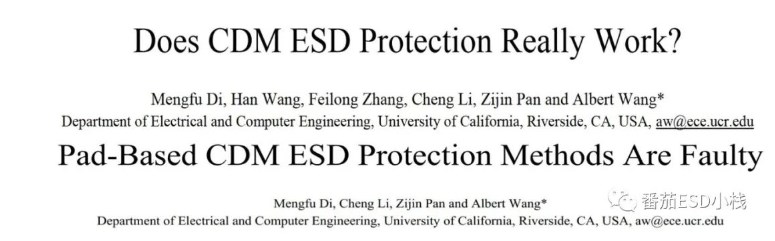

兩種策略各有千秋,適用于不同的場景。但是目前學術界對Pad-Based全片防護策略針對CDM的性能與機制產生了質疑。學者認為Pad-Based全片防護策略可能并不適合于CDM防護。

圖三.Pad-Based 電路結構對CDM防護乏力。

Pad-Based電路結構無法有效對CDM進行防護,主要因為Pad-Based結構多利用寄生器件的反向擊穿電壓或者正向導通累積電壓實現正常工作與ESD的區別,也就是Design Window的設置。而該類器件因為異質結,普遍具有較大的寄生電容參數,對高頻CDM的開啟響應緩慢,瞬態電壓高,阻礙CDM泄放,很難實現令人滿意的CDM保護效果。而Rail-based電路結構則是利用ESD的頻率特性,只要Power Rail上的特征頻率滿足要求,MOS就會開啟,通過MOS管的溝道實現ESD泄放。由于RC-detector電路具有特征頻率的向下兼容性,RC電路能對HBM和CDM都產生響應。

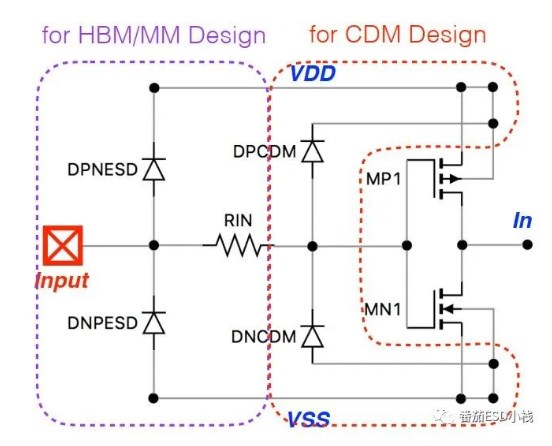

2.2 端口防護策略

目前大多數芯片的IO端口都會采用端口二級防護策略。一級防護針對HBM和MM波形,器件面積大,寄生電容大,開啟速度慢,適合泄放大電流。二級防護針對CDM波形,面積小,寄生電容小,開啟速度快,能快速對CDM進行響應。兩級保護之間的電阻R一方面提高柵極的魯棒性,一方面限制HBM進入二級保護電路。

圖四.CDM的端口防護。

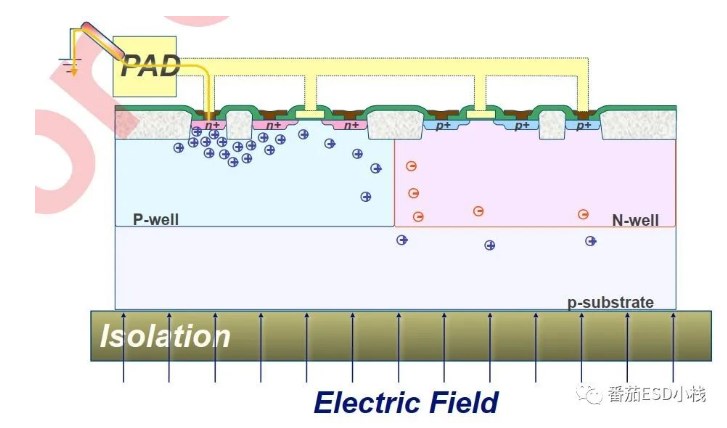

根據前幾章的闡述,CDM源于半導體材料內部。所以二級保護器件需要盡可能的靠近被保護的電路元件,同時還需要和被保護的器件位于同一襯底內,需要其盡可能快的泄放襯底中的非平衡載流子。

圖五.CDM防護示意圖。

如圖所示,襯底中的非平衡載流子通過同一襯底中的N+/P-WeLL二極管和P+/N-WeLL二極管流出體系,避免了柵極所面臨的失效風險。

2.3 布局布線

CDM是一種未經調制的高頻波形,其能量主要集中在高頻波段,而高頻波對電容電感較為敏感。所以布局布線對CDM防護也有一定影響。

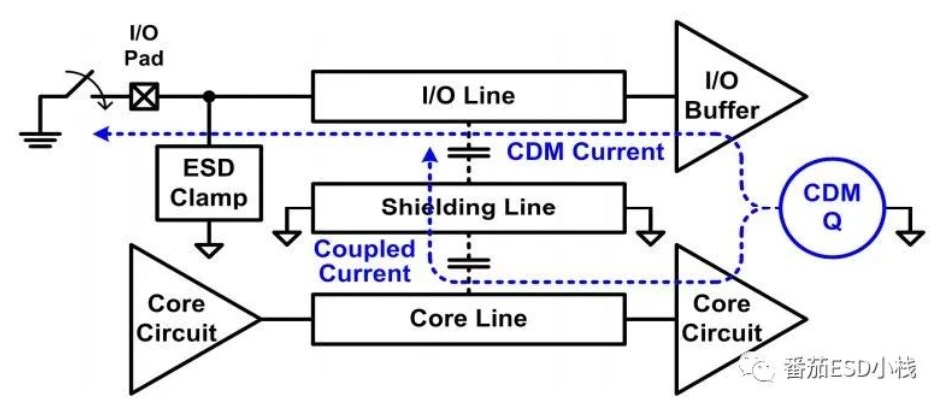

圖六.屏蔽線對CDM的影響。

如圖所示為屏蔽線對CDM的影響,某些設計會在IO線纜旁放置一條接地屏蔽線,但是該屏蔽線會降低體系對CDM的防護能力。屏蔽線會與IO線纜發生耦合作用,在IO上產生耦合電流,降低CDM魯棒性。

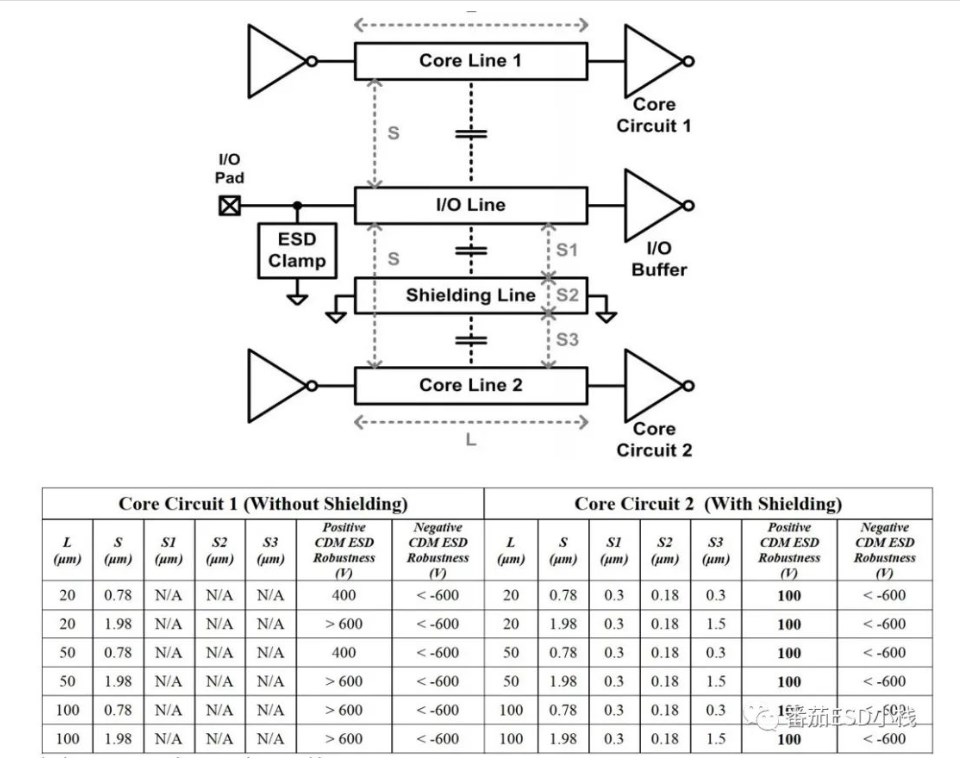

圖七.布局布線對CDM的影響。

如圖所示,布線細節也會對CDM能力產生影響。平行走線長度越長、走線與走線之間的間隔距離越大,防護效果越好。根據傳輸線模型,線纜會對高頻信號造成衰減,而CDM能量主要集中在高頻波段,平行走線長度越長,線纜造成的高頻衰減越大,能略微提升CDM防護效果。CDM作為一種物理現象,波形頻譜分布極其復雜。線纜間的耦合作用更加難以預測,所以增加關鍵IO線纜間的距離,降低耦合作用,也能提高CDM的防護效果。同時IO端口的走線也不要頻繁跳線,避免CDM波形在金屬線中發生反射與折射。

2.4 特殊元器件

為了降低CDM所帶來的破壞,針對CDM的定制化器件也逐漸步入視野。筆者所列之一是前文已經提到過的Ploy-diode(淺談ESD防護—二極管的應用),另一種是LCSCR(Low-Capacitance SCR)。

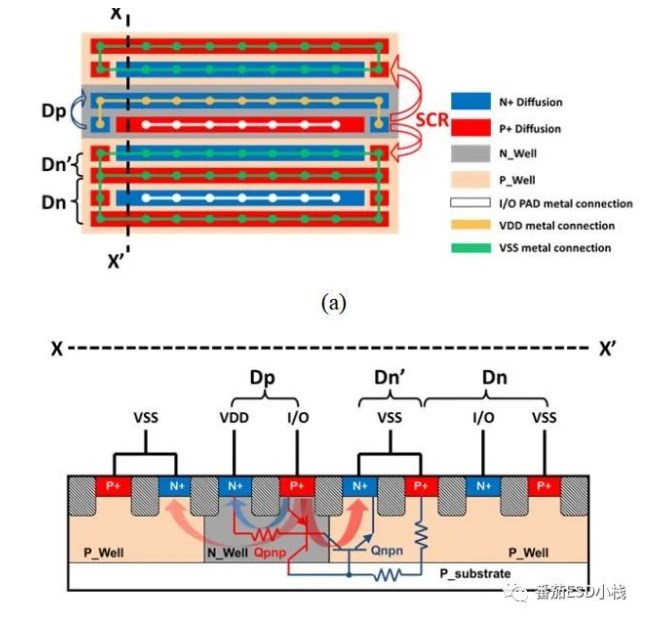

LCSCR器件的版圖與剖面圖如下,該結構中有寄生二極管Dp,Dn也有寄生三極管Qpnp和Qnpn。

圖八.LCSCR版圖與剖面圖。

LCSCR是將IO到VDD和VSS的ESD器件進行了集成。該器件的ESD通路如下:

VDD—GND:通過Power Clamp(RC+GCNMOS)泄放。

GND—VDD:通過Power Clamp 并聯二極管泄放。

IO—VDD:通過寄生二極管(P+/N-WeLL)Dp進行泄放。

VDD—IO:VDD上的靜電流先通過Power Clamp(RC+GCNMOS)進入GND軌,然后通過寄生二極管Dn到達IO。

GND—IO:通過寄生二極管(P-WeLL/N+)Dn進行泄放。

IO—GND:首先靜電流通過Dp進入VDD后,又通過Power Clamp泄放到GND,因為N-WeLL阱電阻的存在,寄生三極管Qpnp的柵極會有壓降,該寄生三極管會開啟,同時靜電流經過P-WeLL也會產生壓降,寄生三極管Qnpn在柵壓下也會開啟。寄生三極管Qpnp和Qnpn相互正反饋,從而建立新的ESD泄放通道,取代Dp—Power Clamp的泄放路徑。相較于傳統SCR,因為該ESD防護網絡采用Rail-Based策略,所以靜電流通過Dp進入VDD后,Power Clamp會快速開啟,電壓降很低。所以基本不會影響VDD—IO,IO—GND路徑的導通電壓和Trigger Voltage。

圖九.LCSCR電路圖。

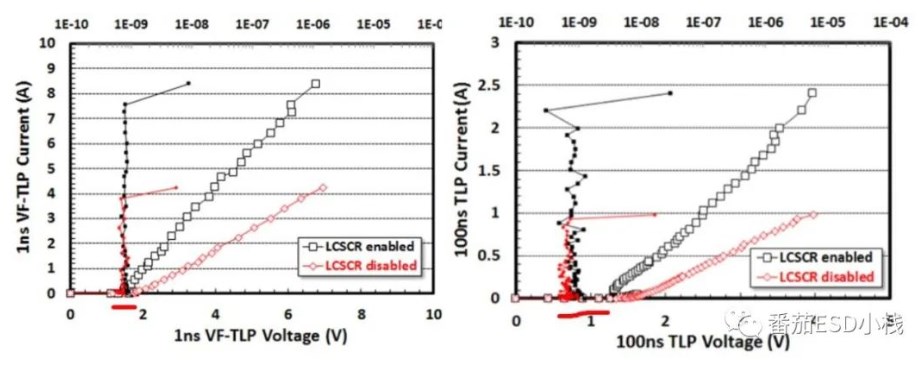

LCSCR的ESD性能如下圖所示:

圖十.LCSCR的TLP和VF-TLP曲線對比。

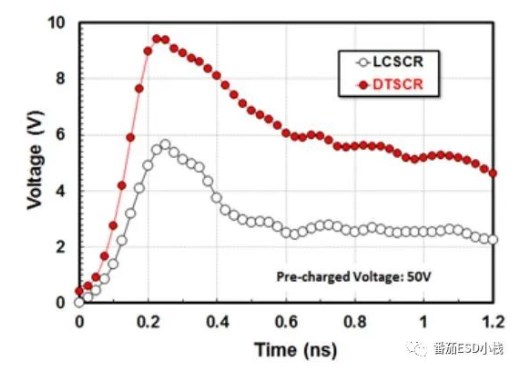

如圖為LCSCR與傳統二極管的ESD性能對比,可以看出無論是TLP還是VF-TLP,新型LCSCR器件的性能都更加優異。其過沖電壓也比二極管串觸發的DTSCR優異。該器件具有良好的CDM防護性能。

圖十一.LCSCR的瞬態過沖電壓。

兩種結構中,Ploy-Diode已經在某些產品中得到了大規模應用,具有良好的前景。而LCSCR結構簡單,性能優異但是還需要更多的驗證。

-

二極管

+關注

關注

148文章

10104瀏覽量

171829 -

ESD

+關注

關注

50文章

2294瀏覽量

175887 -

MOS管

+關注

關注

109文章

2629瀏覽量

70923 -

CDM

+關注

關注

0文章

30瀏覽量

12440 -

RC電路

+關注

關注

2文章

165瀏覽量

30946

發布評論請先 登錄

雷擊浪涌防護方案基本設計思路

ESD有哪幾種防護措施?

靜電防護措施在電視機生產中的應用

手機的輻射和防護措施

通信系統過電壓產生的原因與防護

基于多屬性決策的DDoS防護措施遴選方法

油船腐蝕的類型及防護措施

靜電的危害及防護措施

電氣設備的外殼應有什么防護措施

bnc接頭3通怎樣做好防護措施

評論