大俠好,歡迎來到FPGA技術江湖,江湖偌大,相見即是緣分。大俠可以關注FPGA技術江湖,在“闖蕩江湖”、"行俠仗義"欄里獲取其他感興趣的資源,或者一起煮酒言歡。

今天給大俠帶來基于FPGA的CAN總線控制器的設計,由于篇幅較長,分三篇。今天帶來第一篇,上篇,CAN 總線協議解析以及CAN 通信控制器程序基本框架。話不多說,上貨。

為了方便參考學習,后兩篇這里也放上超鏈接:

基于FPGA的CAN總線控制器的設計(中)

基于FPGA的CAN總線控制器的設計(下)

導讀

CAN 總線(Controller Area Network)是控制器局域網的簡稱,是 20 世紀 80 年代初德國 BOSCH 公司為解決現代汽車中眾多的控制與測試儀器之間的數據交換而開發的一種串行數據通信協議。目前,CAN 總線已經被列入 ISO 國際標準,稱為 ISO11898。CAN 總線已經成為工業數據通信的主流技術之一。

CAN 總線作為數字式串行通信技術,與其他同類技術相比,在可靠性、實時性和靈活性方面具有獨特的技術優勢,主要特點如下:

CAN 總線是一種多主總線,總線上任意節點可在任意時刻主動地向網絡上其他節點發送信息而不分主次,因此可在各節點之間實現自由通信。

CAN 總線采用非破壞性總線仲裁技術。當多個節點同時向總線發送信息時,優先級低的節點會主動退出發送,而最高優先級的節點可以不受影響地繼續傳輸數據,從而大大節省總線沖突的仲裁時間。即使在網絡負載很重的情況下也不會發生網絡癱瘓情況。

CAN 總線的通信介質可以是雙絞線、同軸電纜或光導纖維,選擇靈活。

CAN 總線的通信速率可達 1Mbit/s(此時通信距離最長為 40 米),通信距離最遠可達 10km(速率在 5kbit/s 以下)。

CAN 總線上的節點信息分成不同的優先級,可以滿足不同級別的實時要求,高優先級的數據可以在 134μs 內得到傳輸。

CAN 總線通過報文濾波即可實現點對點、一點對多點及全局廣播等幾種方式傳送數據,無需專門的調度。

CAN 總線的數據采用短幀結構,傳輸時間短,受干擾概率低,具有極好的檢錯效果。

CAN 總線采用 CRC 檢驗并可提供相應的錯誤處理功能,保證了數據通信的可靠性。

CAN 總線上的器件可被置于無任何內部活動的睡眠方式,相當于未連接到總線上,可以有效降低系統功耗。

CAN 總線上的節點在錯誤嚴重的情況下具有自動關閉輸出的功能,以使總線上其他節點的操作不受影響。CAN 總線卓越的特性、極高的可靠性和獨特的設計,特別適合工業過程中監控設備的互連,因此,越來越受到工業界的重視,并被公認為是最有前途的現場總線之一。另外,CAN 總線協議已被國際標準化組織認可,技術比較成熟,控制的芯片已經商品化,性價比高,特別適用于分布式測控系統之間的數通訊。

CAN 總線插卡可以任意插在 PC AT XT 兼容機上,方便地構成分布式監控系統。因此,用 FPGA 實現 CAN 總線通信控制器具有非常重要的應用價值。本篇將通過一個實例講解利用 FPGA 實現 CAN 總線通信控制器的實現方法。

第一篇內容摘要:本篇會介紹CAN 總線協議解析,包括CAN 總線通信模型、CAN 總線協議中的基本概念、報文的數據結構、位時序(Bit Timing)、同步(Synchronization)等相關內容。還會介紹CAN 通信控制器程序基本框架,包括SJA1000CAN 通信控制器、CAN 通信控制器程序框架等相關內容。

一、CAN 總線協議解析

在講解實現 CAN 總線的實例以前,讀者需要具備有關 CAN 總線的基本知識。為此,將在這里簡要介紹與實例相關的基礎知識。

1.1 CAN 總線通信模型

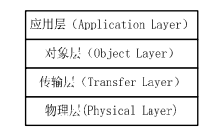

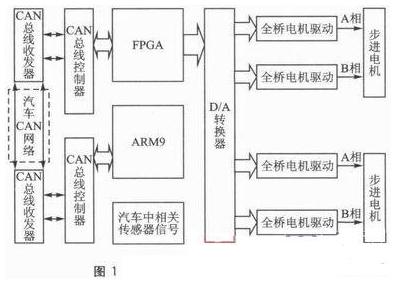

參照 ISO/OSI 標準模型,CAN 總線的通信參考模型如圖 1 所示。

圖 1 CAN 總線通信模型

這 4 層結構的功能如下:

? 物理層規定了節點的全部電氣特性,在一個網絡里,要實現不同節點間的數據傳輸,所有節點的物理層必須是相同的。

? 傳輸層描述了 CAN 總線協議的內核,它負責位時序(bit timing)、同步、仲裁、應答、錯誤探測等。

? 對象層負責報文的過濾、狀態和控制。

? 應用層完成用戶指定的數據傳輸任務。

CAN 總線的物理層為數據通信提供了物理連接,而實際的數據通信在其他 3 層中完成。

1.2 CAN 總線協議中的基本概念

在講解 CAN 總線協議之前,需要介紹有關協議中的基本概念。

1.報文(Messages)

在 CAN 總線傳輸的數據具有固定的格式和有限的長度,稱為報文。

2.發送器(Transmitter)和接收器(Receiver)

在 CAN 總線的數據傳輸過程中,發出報文的節點稱為發送器。節點在總線進入空閑狀態前或丟失仲裁前為發送器。如果一個節點不是報文發送器,并且總線不處于空閑狀態,則該節點為接收器。

3.比特率(bit rate)

CAN 總線的輸出速度以單位時間內傳輸的位來衡量,稱為比特率。CAN 總線在不同的系統中可以有不同的比特率。但是在給定的系統中,比特率是統一的和固定的。

4.優先級(Priorities)

優先級表示總線傳輸中一個報文的優先級別。

5.遠程數據請求(Remote Data Request)

當一個節點向另一個節點請求數據時,需要首先發送一個遠程幀(Remote Frame),然后發送一個和遠程幀相符的數據幀(Data Frame)。遠程幀和數據幀具有相同的標識符。

6.位流(Bit Stream)

CAN 總線通信過程中的數據流。

7.編碼方式CAN 總線通信協議規定,報文中的位流按照非歸零(Non-Return to Zero)碼的方法編碼,一個完整的電平要么是顯性,要么是隱性。

8.非歸零編碼(Non-Return to Zero encoding,簡稱 NRZ)

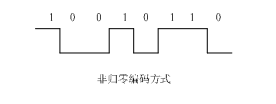

非歸零編碼是一種用在低速通信接口中的編碼方式,同時提供同步和非同步兩種方式。在非歸零編碼方式中,邏輯“1”在傳輸過程中用一位高電平表示,邏輯“0”用一位低電平表示。非歸零編碼方式如圖 2 所示。

圖 2 非歸零編碼方式

9.總線數值

在數據傳輸時,CAN 總線有兩種邏輯值:顯性值(dominant)和隱性值(recessive)。如果同時傳輸顯性值和隱性值時,總線上的最終結果是顯性值。在線與(wired-AND)總線連接方式中,顯性值用邏輯“0”表示,隱性值用邏輯“1”表示。

1.3報文的數據結構

CAN 總線的報文傳輸是通過 4 種不同類型的幀(Frame)來表示和控制的:

? 數據幀(Data Frame) 用來在數據傳輸過程中攜帶數據。

? 遠程幀(Remoter Frame) 接收器發送遠程幀來請求發送器發送數據,具有和數據幀同樣的標識符。

? 出錯幀(Error Frame) 用來檢測 CAN 總線數據傳輸過程中的錯誤。

? 超載幀(Overload Frame) 用于提供當前和后續數據幀或遠程幀之間的附加延遲。

a.數據幀

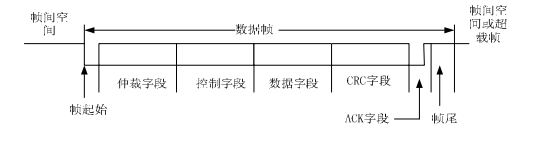

數據幀的具體組成如圖 3 所示。

圖 3 數據幀的具體組成

數據幀由幀起始(Start of Frame,SOF)、仲裁字段、控制字段、數據字段、CRC 字段、ACK 字段(應答字段)和幀尾組成。

幀起始標志數據幀的開始(遠程幀同樣具有幀起始),它僅由一個顯性值組成。只有在總線處于空閑時,才允許節點開始發送。所有節點必須與首先開始發送的那個節點的幀起始位前沿同步。

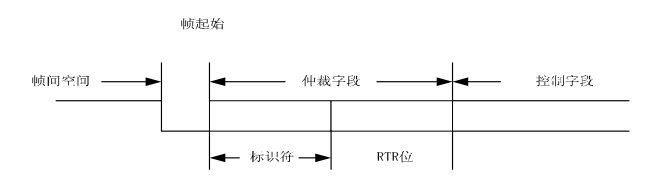

仲裁字段由標識符和遠程發送請求位(RTR 位)組成,如圖 4 所示。標識符的長度為 11位。遠程發送請求位在數據幀中必須是顯性值,在遠程幀中必須是隱性值。

圖 4 仲裁字段的組成

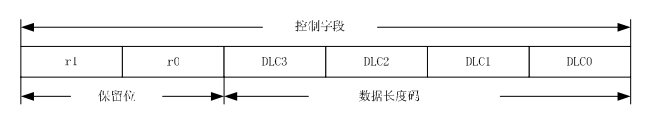

控制字段由保留位和數據長度碼組成,如圖 5 所示。數據長度碼表示數據字段的長度。

圖 5 控制字段的組成

數據字段由數據幀中被發送的數據組成,它可以包括 0~8 個字節,每個字節 8 位。首先發送的是最高有效位。

CRC 字段包括 CRC 序列和 CRC 界定符。CRC 序列用來實現 CRC 計算,CRC 界定符只包括一個隱性值。應答字段為兩位,包括應答間隙和應答界定符。幀尾由 7 個連續的隱性值組成,作為數據幀和遠程幀的結束標志。

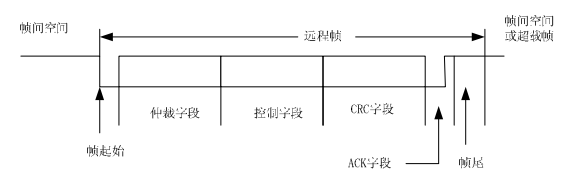

b.遠程幀

作為接收器的節點可以通過向相應的數據源節點發送一個遠程幀來激活該節點,讓它把數據發送給接收器。遠程幀由幀起始、仲裁字段、控制字段、CRC 字段、應答字段和幀尾 6 個不同的字段組成。遠程幀的組成如圖 6 所示。

圖 6 遠程幀的組成

c.出錯幀

出錯幀由出錯疊加標志和錯誤界定符組成。出錯疊加標志包括了多個出錯信息的標志。

d.超載幀

超載幀包括超載標志和超載界定符。超載發生在兩種情況下:一個是接收器因內部條件要求推遲下一個數據幀或者遠程幀的發送;另一個是在間歇字段檢測到顯性值時。

e.幀間空間

數據幀或遠程幀通過幀間空間與前一幀隔開,而不管前一幀是何種類型的幀。而在超載幀與出錯幀前面不需要幀間空間,多個超載幀之間也不需要幀間空間來作分隔。

1.4位時序(Bit Timing)

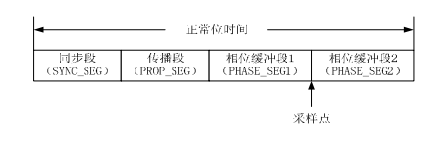

CAN 總線協議規定,報文傳輸的同步或者非同步方式的選擇通過位時序來實現。CAN 總線中位時序包括正常位速率和正常位時間兩個參數。

? 正常位速率(Nominal Bit Rate):在非重同步情況下,借助理想發送器每秒發送的位數。

? 正常位時間(Nominal Bit Time):正常位速率的倒數。正常位時間由幾個不同的時間段組成,它們是同步段(SYNC_SEG)、傳播段(PROP_SEG)、相位緩沖段 1(PHASE_SEG1)、相位緩沖段 2(PHASE_SEG2),如圖 7 所示。

圖 7 正常位時間的組成

? 同步段:在這段時間內,完成總線上各個節點的同步,需要一個跳變沿。

? 傳播段:這個時間段是指網絡上傳輸的延遲時間,它是信號在總線上傳播時間、輸入比較器延遲和輸出驅動器延遲之和的兩倍。

? 相位緩沖段 1 和相位緩沖段 2:它們用于彌補跳變沿的相位誤差造成的影響。通過重同步,這兩個時間段可以被延長或縮短。

? 采樣點:這是讀取總線電平并理解該位數值的時刻,它位于相位緩沖段 1 的終點。

1.5同步(Synchronization)

a.硬同步(Hard Synchronization)

硬同步后,內部位時間從同步段(SYNC_SEG)重新開始,它迫使觸發該硬同步的跳變沿處于新的位時間的同步段(SYNC_SEG)之內。

b.重同步(Resynchronization)

當引起重同步沿的相位誤差小于或等于重同步跳轉寬度編程值時,重同步的作用和硬同步相同。若相位誤差大于重同步跳轉寬度且相位誤差為正時,則相位緩沖段 1(PHASE_SEG1)延長總數為重同步跳轉寬度。若相位誤差大于重同步跳轉寬度且相位誤差為負時,則相位緩沖段2(PHASE_SEG2)縮短總數為重同步跳轉寬度。

c.重同步跳轉寬度(Resynchronization Jump Width)

由于重同步的結果,PHASE_SEG1 可被延長或 PHASE_SEG2 可被縮短。相位緩沖段長度的改變量不應大于重同步跳轉寬度。

d.同步的規則CAN

通信協議規定,同步包括硬同步和重同步兩種形式。它們遵從下列幾條規則:

在一個位時間內僅允許一種同步。

對于一個跳變沿,僅當它前面的第一個采樣點數值與緊跟該跳變沿之后的總線值不相同時,才把該跳變沿用于同步。

在總線空閑期間,若出現一個從隱性值到顯性值的跳變沿,則執行一次硬同步。

符合規則前兩條規則的從隱性值到顯性值的跳變沿都被用于重同步(在低比特率時也可選擇從顯性值到隱性值的跳變沿),例外的情況是具有正相位誤差的隱性值到顯性值的跳變沿將不會導致重同步。

二、CAN 通信控制器程序基本框架

CAN 總線的通信協議由 CAN 通信控制器完成。CAN 通信控制器由實現 CAN 總線協議部分和微控制器部分的電路組成。下面將通過一個實例講解如何用 FPGA 實現 CAN 通信控制器的功能。這個實例從功能和結構上完全參照 SJA 1000 CAN 通信控制器。

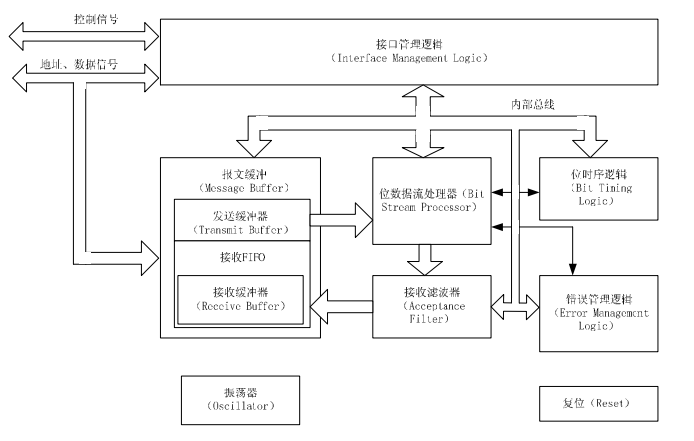

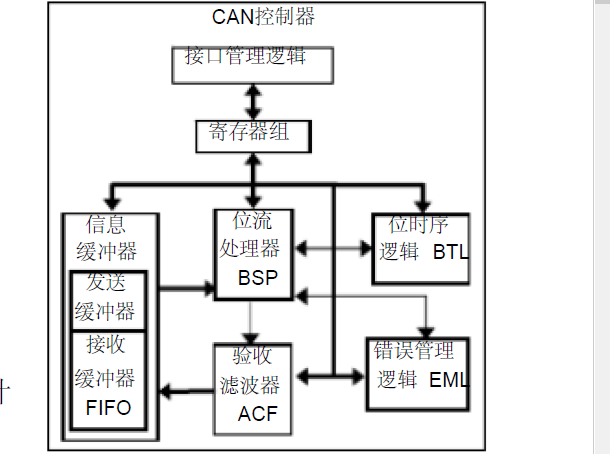

2.1 SJA1000CAN 通信控制器

SJA1000 是 Philips 公司于 1997 年推出的一種獨立 CAN 總線控制器。它實現了 CAN 總線物理層和數據鏈路層的所有功能。SJA 1000 通信控制器的功能框圖如圖 8 所示。

SJA 1000 主要由以下幾部分構成:

? 接口管理邏輯 處理來自主 CPU 的命令,控制 CAN 寄存器的尋址,并為主 CPU 提供中斷和狀態信息。

? 發送緩沖器 它是 CPU 和位數據流處理器(BSP)之間的接口,能存儲一條可發送到 CAN總線上的完整報文。報文由 CPU 寫入,由位數據流處理器讀出。

圖 8 SJA1000 通信控制器功能框圖

? 接收緩沖器 它是接收 FIFO 的一個可被 CPU 訪問的窗口。在接收 FIFO 的支持下,CPU可以在處理當前信息的同時接收總線上的其他信息。

? 接收濾波器 它把收到的報文標識符和接收濾波器寄存器中的內容進行比較,以判斷該報文是否應該被接收。如果符合接收條件,則報文被存入接收 FIFO 中。

? 位數據流處理器 它是一個序列發生器,控制發送緩沖器、接收 FIFO 和 CAN 總線之間的數據流,同時它也執行錯誤檢測、仲裁、位填充和 CAN 總線錯誤處理功能。

? 位時序邏輯 它監視串行 CAN 總線并處理與總線相關的位時序。它在報文開始發送,總線電平從隱性值跳變到顯性值時同步于 CAN 總線上的位數據流(硬同步),并在該報文的傳送過程中,每遇到一次從隱性值到顯性值的跳變沿就進行一次重同步(軟同步)。位時序邏輯還提供可編程的時間段來補償傳播延遲時間和相位漂移(如晶振導致的漂移),還能定義采樣點以及每一個位時間內的采樣次數。

? 錯誤管理邏輯 它按照 CAN 協議完成傳輸錯誤界定。它接收來自位數據流處理器 BSP 的出錯通知,并向位數據流處理器 BSP 和接口管理邏輯提供出錯統計。

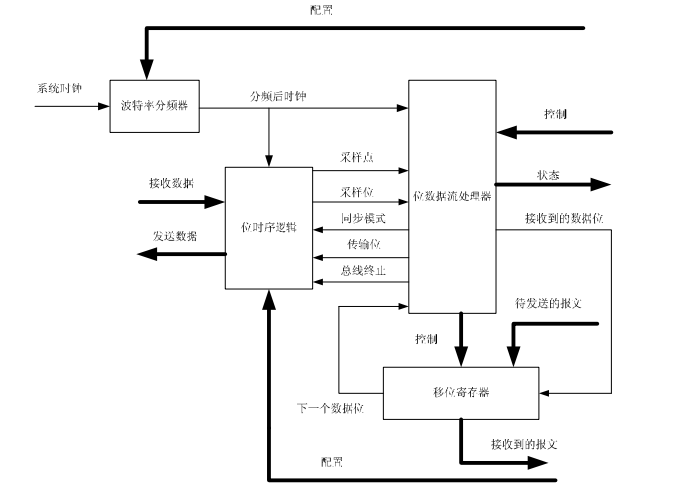

2.2 CAN 通信控制器程序框架

實現的 CAN 通信控制器參照 SJA1000 CAN 通信控制器的結構,程序基本框架如圖 9 所示。

圖 9 CAN 通信控制器結構框圖

本篇到此結束,下一篇帶來基于FPGA的CAN總線控制器的設計(中),會介紹CAN 通信控制器的具體實現,包括頂層控制程序、寄存器控制、位時序邏輯(Bit Timing Logic)、位數據流處理器(BitStream Processor)、CRC 校驗 、FIFO等相關內容。

審核編輯:湯梓紅

-

FPGA

+關注

關注

1629文章

21729瀏覽量

602986 -

控制器

+關注

關注

112文章

16332瀏覽量

177806 -

CAN總線

+關注

關注

145文章

1946瀏覽量

130726 -

CAN

+關注

關注

57文章

2744瀏覽量

463615 -

局域網

+關注

關注

5文章

751瀏覽量

46277

原文標題:基于FPGA的CAN總線控制器的設計

文章出處:【微信號:HXSLH1010101010,微信公眾號:FPGA技術江湖】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

基于FPGA的CAN總線控制器的設計(附代碼)

基于STM32和FPGA的CAN總線運動控制器的設計

基于FPGA和CAN控制器MCP2515設計慣導系統的CAN總線

基于FPGA的CAN總線控制器SJA1000軟核的設計方案解析

如何使用FPGA進行CAN控制器軟核的設計與實現

如何使用FPGA和CAN控制器MCP2515實現慣導系統的CAN總線接口的設計

基于FPGA的CAN總線控制器的設計

基于FPGA的CAN總線控制器的設計

評論