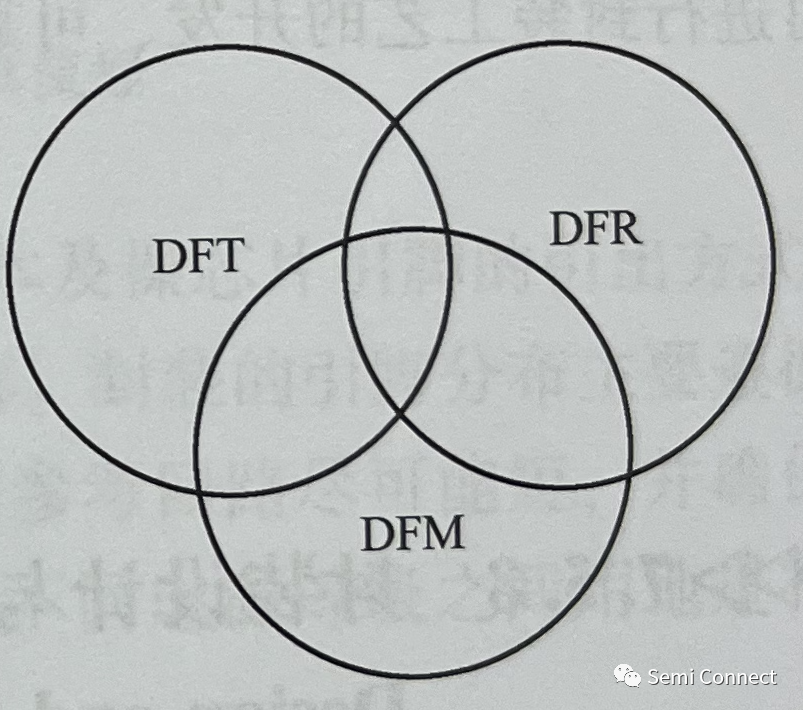

可制造性設計 (Design for Manufacturabiity, DFM)、可靠性設計 (Designfor Reliability, DFR)與可測試性設計 (Design for Testability, DFT)互相交疊密不可分,需要綜合考慮,以實現設計與工藝的迭代優化。DFM/DFR/DFT 協同設計示意圖如圖所示。

(1) DFM:可制造性設計的目的是基于先進封裝工藝能力,綜合封裝性能需求,實現設計與制造工藝的緊密結合。封裝設計首先應考慮封裝工藝的能力,要以大規模生產所需的工藝設計淮則來確定電氣、散熱性能及封裝結構設計,并允許在特殊需求下調整和優化工藝。例如,為了提高散熱性能,QFN 封裝底部中央位置有一個大面積裸露焊盤用于導熱,根據工藝和芯片情況可實現單芯片或多芯片的集成;為滿足高頻應用的需求,可通過優化 OFN封裝工藝縮短引線長度,以此提供射頻(甚至毫米波)信號的傳輸。

芯片堆蠶是一種典型3D封裝形式,芯片堆香工藝對芯片尺寸、引線鍵合的引腳位置都有限制,為提高堆疊芯片的數量,需要進行芯片滅薄和低弧度鍵合工藝的優化。這類由應用需求引起的結構/材料優化和工藝優化需要考慮可靠性性能,因此需要 DFM 與DFR 之間的協同設計。

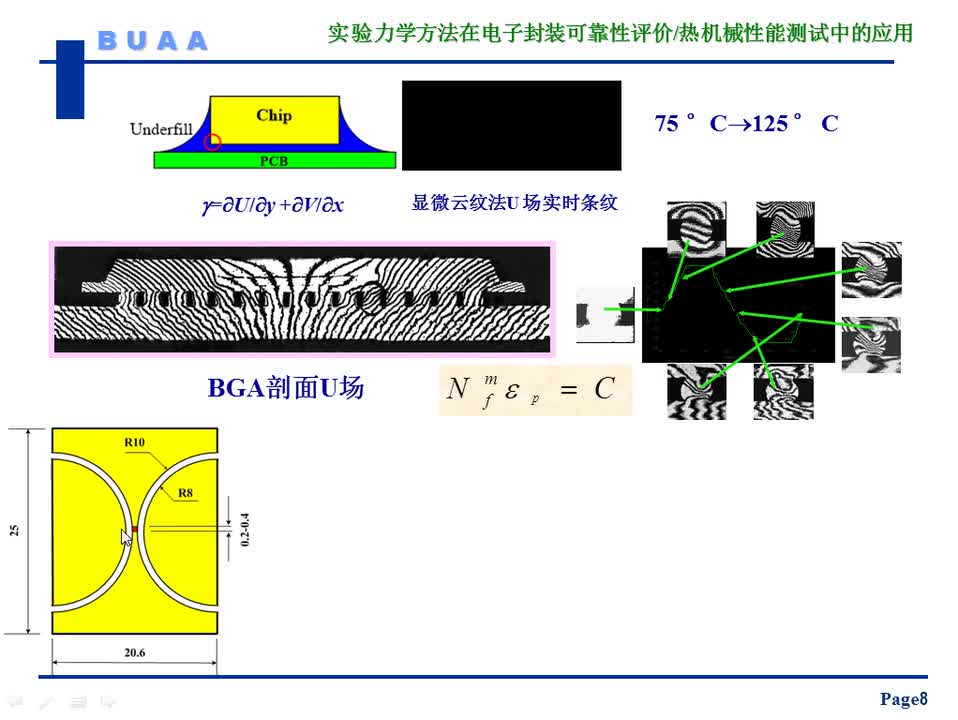

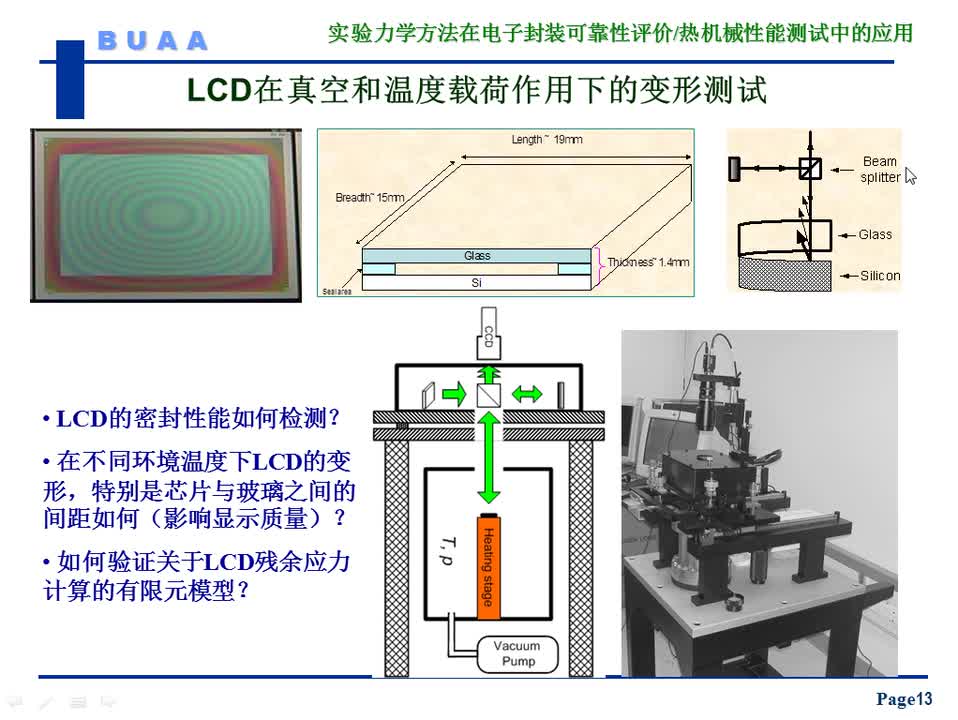

(2) DFR:可靠性設計的目的是為了采用 DOE試驗設計方法實現結構和材料設計的迭代優化,消除可靠性隱患。在設計之初,通過對材料和結構體系的優化,采用份真模擬、理論分析和實驗驗證相結合的方式,對封裝的熱應力/應變、熱疲勞、電遷移等可靠性相關問題進行研究和優化。由于熱應力源自不同封裝材料之間的熱失配,所以設計時應盡量采用對稱的封裝結構,選擇熱膨賬系數匹配、玻璃化溫度(Tg)合適的封裝材料,也可以通過添加底部填料來提高封裝和裝配的可靠性。芯片-封裝交互作用 ( Chip Package Interaction, CPI)也是DFR 的重要內容。

(3)DFT:通常意義上的可測性設計,是指在設計系統和電路的同時,通過增加一定的硬件開銷,從而獲得最大可測性的設計過程,其目的是用于檢測生產故障。例如,數字電路常見的可測性設計方法有掃描測試(SCAN)、內建自測試(Built-In Self-Test, BIST)、邊界掃描測試(Boundary Scan Test)等。這些DFT方法都可應用于常規的封裝形式,如QFN 封裝、BGA封裝等。

對于2.5D 類復雜封裝,在封裝制備過程中也要進行可測性設計。為了檢測TSV 中介轉接層的成品率,除了直接用探針進行接觸式測量,也可設計 TSV 測試電路并配合軟件來進行測試。對于有特殊需求的封裝,如高頻/高速封裝、大功率封裝等,還需制定單項性能測試方案。例如,設計可測性高速測試線路樣品,可對封裝體內典型的互連結構的電學性能進行測量;設計可測性熱阻測試樣品,可事先對封裝體內的結溫和熱阻進行測量;設計基于菊花鏈的測試樣品可進行封裝工藝的開發、可靠性性能的評估等。

審核編輯:湯梓紅

-

封裝

+關注

關注

127文章

8200瀏覽量

144024 -

可制造性

+關注

關注

0文章

22瀏覽量

7009 -

可靠性

+關注

關注

4文章

268瀏覽量

26922 -

DFM

+關注

關注

8文章

469瀏覽量

28764 -

DFR

+關注

關注

0文章

4瀏覽量

2965

原文標題:可制造性、可靠性和可測性協同設計,可製造性、可靠性和可測性協同設計,DFM/DFR/DFT Co-design

文章出處:【微信號:Semi Connect,微信公眾號:Semi Connect】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

評論