1、復位的重要性

數字電路中寄存器和 RAM 在上電之后默認的狀態和數據是不確定的,如果有復位,我們可以把寄存器 復位到初始狀態 0,RAM 的數據可以通過復位來觸發 RAM 初始化到全 0。那可能很多人會問為什么是全 0呢?其實一般邏輯起始都是從 0 開始變化的,這個是根據設計的需要設定的一個值,如果設計需要寄存器 上電復位為 1,也是可以的。還有一種情況是邏輯進入了錯誤的狀態,通過復位可以把所有的邏輯狀態恢復 到初始值,如果沒有復位,那么邏輯可能永遠運行在錯誤的狀態。

因此復位功能是很重要的一個功能。數字電路的復位通常可分為:同步復位與異步復位。

2、同步復位

同步復位:同步復位指的是當時鐘上升沿檢測(有效沿)到復位信號,執行復位操作,有效的時鐘沿是前提。

Verilog代碼:

//*******************同步復位模塊**************************

//-----------端口定義-------------------------------

inputclk,//工作時鐘

inputrst_n,//復位,低電平有效

inputin,//輸入信號

outputregout//輸出信號

);

//-----------輸出模塊-------------------------------

always@(posedge clk )begin

if(!rst_n)

out <= 1'b0;//復位將輸出置零

else

out <= in;//其他時候將輸入賦值給輸出

end

endmodule

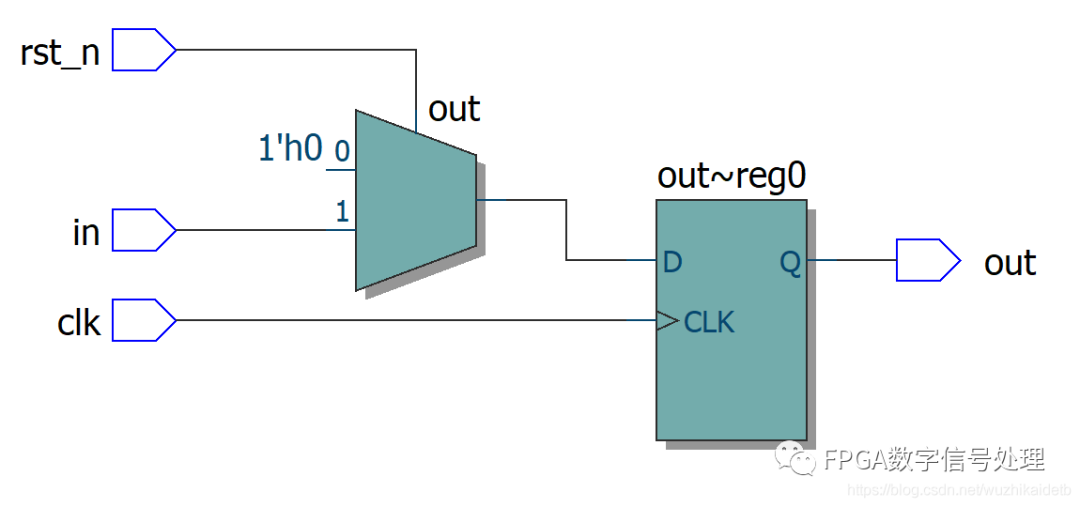

使用Quartus II綜合出的RTL如下:

可以看到,生成的觸發器并沒有復位置位端,而是生成了一個選擇器,同步復位信號rst_n用作了選擇器的使能,從而實現復位清零的作用。

用如下Testbench進行仿真(復位時間不足一個時鐘周期、復位時間超過一個時鐘周期、一個高頻復位毛刺):

//------------------------------------------------

//--同步復位仿真

//------------------------------------------------

`timescale 1ns/1ns//時間單位/精度

//------------<模塊及端口聲明>----------------------------------------

module tb_rst_test();

reg clk;

reg rst_n;

regin;

wireout;

//------------<例化被測試模塊>----------------------------------------

rst_testrst_test_inst(

.clk(clk),

.rst_n(rst_n),

.in(in),

.out (out)

);

//------------<設置初始測試條件>----------------------------------------

initial begin

clk = 1'b0;

rst_n <= 1'b0;

in <= 1'b1;

#5

rst_n <= 1'b1;

#6

rst_n <= 1'b0;?

#18

rst_n <= 1'b1;

#39

rst_n <= 1'b0;

#21

rst_n <= 1'b1;

#25

rst_n <= 1'b0;

#3

rst_n <= 1'b1;?

end

//------------<設置時鐘>----------------------------------------------

always #10 clk = ~clk;//系統時鐘周期20ns

endmodule

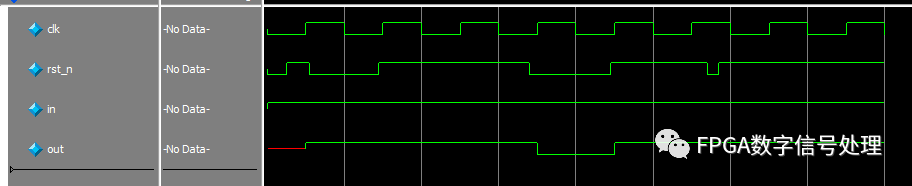

仿真結果如下:

從仿真結果可以看到:

第1個復位時間不足一個時鐘周期,導致復位不成功

第2個復位時間超過一個時鐘周期,復位成功

最后一個復位信號上的高頻毛刺信號沒有對系統造成誤復位

輸出信號在第一個時鐘上升沿到來之前是未知狀態

同步復位電路的優點:

有利于仿真器的仿真

基本上沒有亞穩態問題

可以使所設計的系統成為 100%的同步時序電路,有利于時序分析

由于只在時鐘有效電平到來時才有效,所以可以濾除高于時鐘頻率的復位毛刺

同步復位電路的缺點:

復位信號的有效時長必須大于時鐘周期,才能真正被系統識別并完成復位任務。同時還要考慮延時因素

大多數的FPGA的DFF都只有異步復位端口,采用同步復位的話,綜合器就會在寄存器的數據輸入端口插入組合邏輯,這樣會耗費邏輯資源

3、異步復位

異步復位:異步復位指的是無論時鐘沿是否到來,只要復位信號有效,就對系統進行復位。當時鐘上升沿檢測到復位信號,執行復位操作。

Verilog代碼:

//*******************同步復位模塊**************************

//-----------端口定義-------------------------------

modulerst_test(

inputclk,//工作時鐘

inputrst_n,//復位,低電平有效

inputin,//輸入信號

outputregout//輸出信號

);

//-----------輸出模塊-------------------------------

always@(posedge clk or negedge rst_n)begin

if(!rst_n)

out <= 1'b0;//復位將輸出置零

else

out <= in;//其他時候將輸入賦值給輸出

end

endmodule

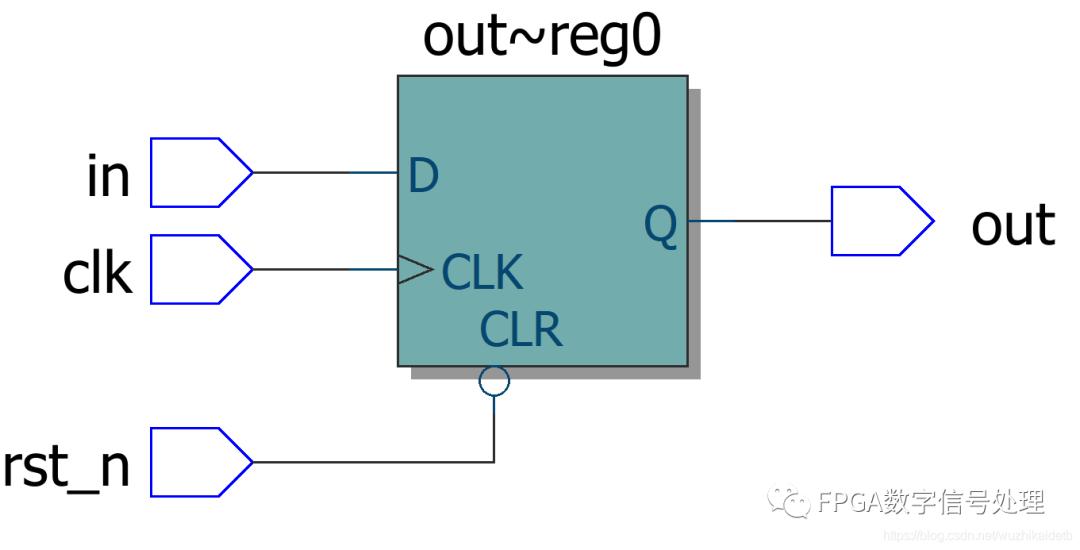

使用Quartus II綜合出的RTL如下:

可以看到,異步復位信號rst_n直接接入了觸發器的異步復位端,從而實現復位清零的作用。

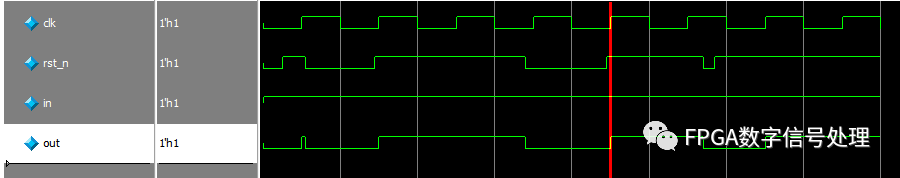

依然使用之前用的Testbench進行仿真,結果如下:

從仿真結果可以看到:

只要復位信號被置為低電平,就執行復位操作,與時鐘無關

高頻毛刺信號會對系統造成誤復位

在不考慮亞穩態的前提下,復位時間沒有要求

a、在復位信號釋放(release)的時候容易出現問題。具體就是說:倘若復位釋放時恰恰在時鐘有效沿附近,就很容易使寄存器輸出出現亞穩態,從而導致亞穩態。

b、復位信號容易受到毛刺的影響

異步復位電路的優點:

大多數目標器件庫的dff都有異步復位端口,因此采用異步復位可以節省資源

設計相對簡單,異步復位信號識別方便,而且可以很方便的使用FPGA的全局復位端口GSR

異步復位電路的缺點:

復位信號容易受到毛刺的影響

因為是異步邏輯,無法避免地存在亞穩態問題

關于異步復位還需要考慮:

恢復時間(Recovery Time)是指異步控制信號(如寄存器的異步清除和置位控制信號)在“下個時鐘沿”來臨之前變無效的最小時間長度。這個時間的意義是,如果保證不了這個最小恢復時間,也就是說這個異步控制信號的解除與“下個時鐘沿”離得太近(但在這個時鐘沿之前),沒有給寄存器留有足夠時間來恢復至正常狀態,那么就不能保證“下個時鐘沿”能正常作用,也就是說這個“時鐘沿”可能會失效。

去除時間(Removal)是指異步控制信號(如寄存器的異步清除和置位控制信號)在“有效時鐘沿”之后變無效的最小時間長度。這個時間的意義是,如果保證不了這個去除時間,也就是說這個異步控制信號的解除與“有效時鐘沿”離得太近(但在這個時鐘沿之后),那么就不能保證有效地屏蔽這個“時鐘沿”,也就是說這個“時鐘沿”可能會起作用。

換句話來說,如果你想讓某個時鐘沿起作用,那么你就應該在“恢復時間”之前是異步控制信號變無效,如果你想讓某個時鐘沿不起作用,那么你就應該在“去除時間”過后使控制信號變無效。如果你的控制信號在這兩種情況之間,那么就沒法確定時鐘沿是否起作用或不起作用了,也就是說可能會造成寄存器處于不確定的狀態。而這些情況是應該避免的。所以恢復時間和去除時間是應該遵守的。

4、異步復位、同步釋放

結合兩種復位的優點,可以使用異步復位、同步釋放設計,Verilog代碼如下:

//*******************同步復位模塊**************************

//-----------端口定義-------------------------------

modulerst_test(

inputclk,//工作時鐘

inputrst_n,//復位,低電平有效

inputin,//輸入信號

outputregout//輸出信號

);

//-----------reg定義-------------------------------

reg arst_n_r;

reg arst_n;

//-----------復位信號同步模塊-------------------------------

always@(posedge clk or negedge rst_n)begin

if(!rst_n)begin

arst_n_r <= 1'b0;//復位將輸出置零

arst_n <= 1'b0;//復位將輸出置零?

end

else begin

arst_n_r <= 1'b1;//跟接rst_n是一樣的,都是邏輯1

arst_n <= arst_n_r;??

end

end

//-----------輸出模塊-------------------------------

always@(posedge clk or negedge arst_n)begin

if(!arst_n)

out <= 1'b0; ? ?//復位將輸出置零

else

out <= in; ? ?//其他時候將輸入賦值給輸出

end

endmodule

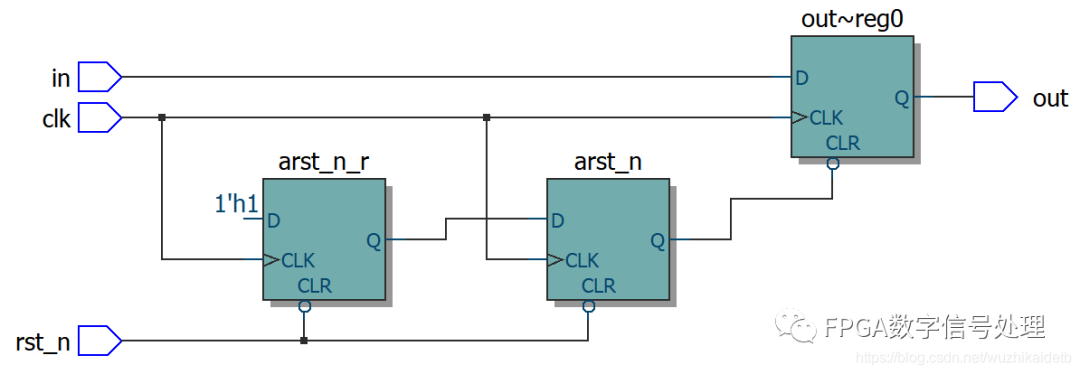

綜合出來的RTL視圖:

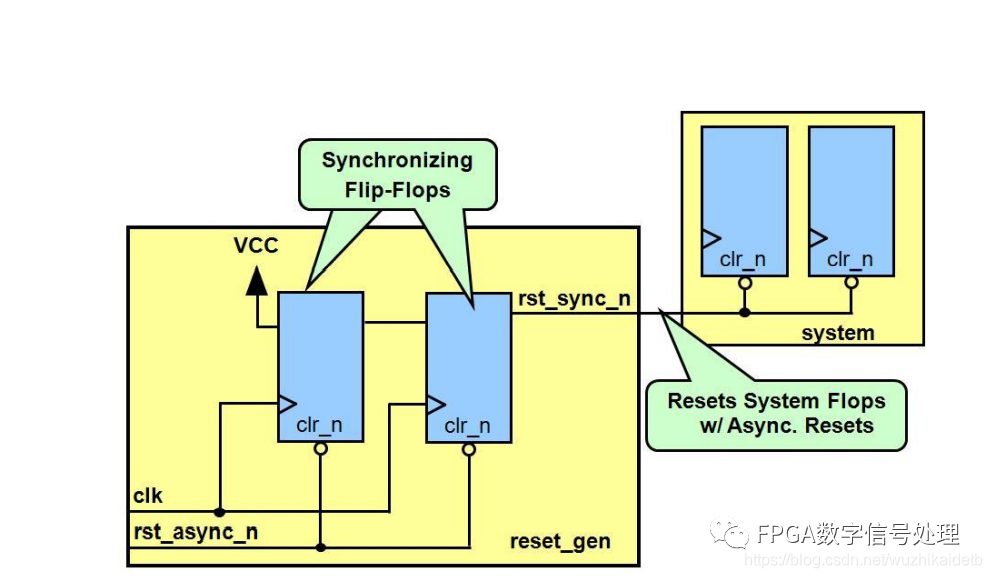

實際的電路圖如下:

復位信號 rst_sync_n 由高拉低時實現 y 寄存器的異步復位。同步釋放,這個是關鍵,即當復位信號 rst_async_n 撤除時(由低拉高),由于雙緩沖電路(雙觸發器)的作用,rst_sync_n 不會隨著rst_async_n 的 撤除而撤除。假設 rst_async_n 撤除時發生在 clk 上升沿,如果不加此電路則可能發生亞穩態事件,但是加上此電路以后,假設第一級 D 觸發器 clk 上升沿時 rst_async_n 正好撤除,(第一個 DFF 此時是處于亞穩態 的;假設此時識別到高電平;若是識別到低電平,則增加一個 Delay)則 DFF1 輸出高電平,此時第二級觸發器也會更新輸出,但是輸出值為前一級觸發器 clk 來之前時的 Q1 輸出狀態,顯然 Q1 之前為低電平,所以第二級觸發器輸出保持復位低電平,直到下一個 clk 來之后,才隨著變為高電平,即同步釋放。

使用如下Testbench進行仿真:

//------------------------------------------------

//--同步復位仿真

//------------------------------------------------

`timescale 1ns/1ns//時間單位/精度

//------------<模塊及端口聲明>----------------------------------------

module tb_rst_test();

reg clk;

reg rst_n;

regin;

wireout;

//------------<例化被測試模塊>----------------------------------------

rst_testrst_test_inst(

.clk(clk),

.rst_n(rst_n),

.in(in),

.out (out)

);

//------------<設置初始測試條件>----------------------------------------

initial begin

clk = 1'b0;

rst_n <= 1'b0;

in <= 1'b1;

#25

rst_n <= 1'b1;

#6

rst_n <= 1'b1;

#18

rst_n <= 1'b1;

#39

rst_n <= 1'b0;

#21

rst_n <= 1'b1;

end

//------------<設置時鐘>----------------------------------------------

always #10 clk = ~clk;//系統時鐘周期20ns

endmodule

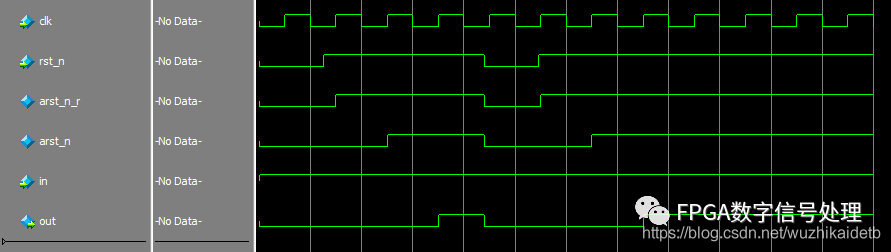

仿真結果如下:

可以看到:復位是異步進行的,一旦復位信號為低電平,則輸出復位,而復位的撤除則被同步到了時鐘域下。如此一來,既解決了同步復位的資源消耗問題,也解決了異步復位的亞穩態問題。其根本思想,也是將異步信號同步化。

聲明: 本文轉載自csdn:孤獨的單刀,如涉及作品內容、版權和其它問題,請于聯系工作人員微(in0723mango),我們將在第一時間和您對接刪除處理! 投稿/招聘/廣告/課程合作/資源置換請加微信:13237418207

Xilinx FPGA的約束設計和時序分析總結

-

寄存器

+關注

關注

31文章

5336瀏覽量

120232 -

RAM

+關注

關注

8文章

1368瀏覽量

114643 -

數字電路

+關注

關注

193文章

1605瀏覽量

80580

原文標題:FPGA同步復位、異步復位、異步復位同步釋放

文章出處:【微信號:FPGA研究院,微信公眾號:FPGA研究院】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

數字電路的復位可分為哪些

數字電路的復位可分為哪些

評論