現(xiàn)如今,ASML幾乎成了***的代名詞。尤其是隨著EUV、甚至High-NA EUV***的推出,ASML更是獨(dú)霸高端***市場(chǎng)。

眾所周知,光刻是芯片制造過程中最重要、最復(fù)雜也最昂貴的工藝步驟,其成本占總生產(chǎn)成本的30%以上,同時(shí)占據(jù)了將近50%的生產(chǎn)周期。

數(shù)十年來,在DUV、EUV***的支持下,摩爾定律得到了延續(xù)。然而,迭代至今,面對(duì)芯片晶體管線寬已趨近物理極限,以及EUV***產(chǎn)能有限、成本高等問題,業(yè)界開始加強(qiáng)探索繞開EUV***生產(chǎn)高端芯片的技術(shù)和工藝。

其中,納米壓印技術(shù)(NIL)走到了臺(tái)前。

近日,有消息披露,SK海力士從佳能引進(jìn)了納米壓印設(shè)備,目前正在進(jìn)行測(cè)試,計(jì)劃在2025年左右使用該設(shè)備開始量產(chǎn)3D NAND閃存,到目前為止的測(cè)試結(jié)果良好。

這里提到的納米壓印技術(shù),就是被認(rèn)為最有可能替代EUV的下一代光刻技術(shù)。

納米壓印技術(shù)如何對(duì)標(biāo)EUV光刻?

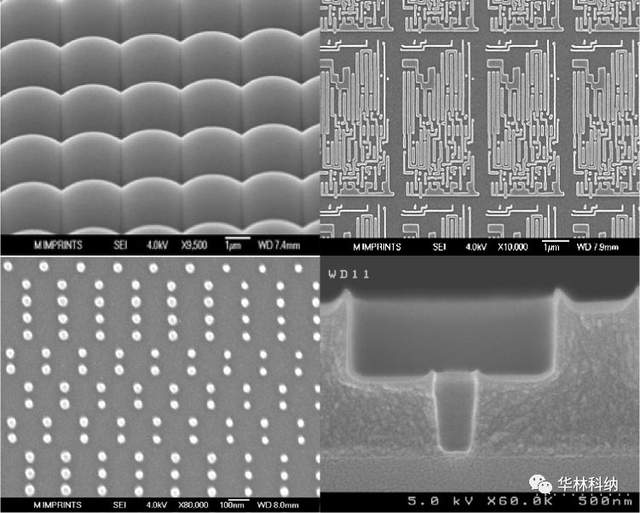

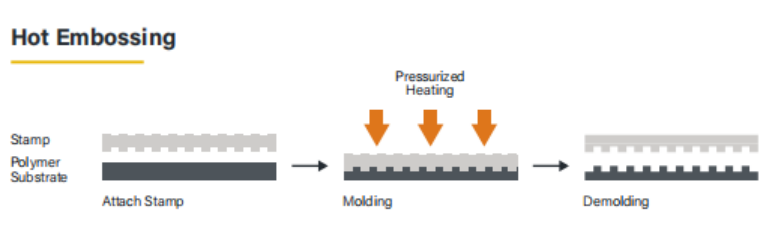

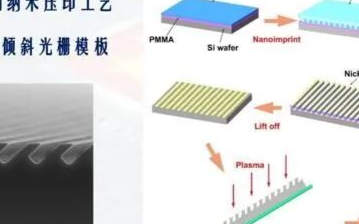

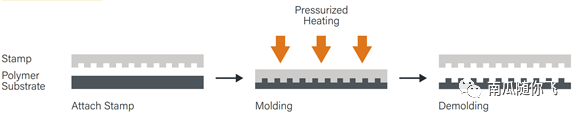

納米壓印技術(shù),即Nanoimprint Lithography(NIL),是一種新型的微納加工技術(shù)。該技術(shù)將設(shè)計(jì)并制作在模板上的微小圖形,通過壓印等技術(shù)轉(zhuǎn)移到涂有高分子材料的硅基板上。納米壓印的分辨率由所用印模板圖形的大小決定,物理上沒有光刻中的衍射限制,納米壓印技術(shù)可以實(shí)現(xiàn)納米級(jí)線寬的圖形。

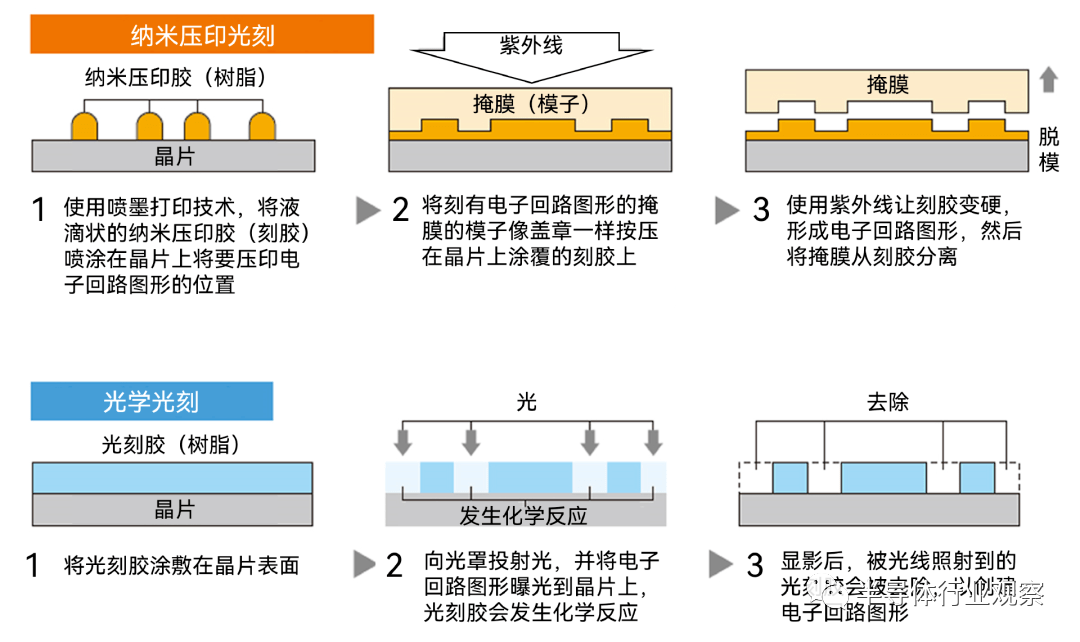

紫外納米壓印光刻與光學(xué)光刻流程對(duì)比

(圖源:果殼硬科技)

可以理解為,納米壓印技術(shù)造芯片就像蓋章一樣,把柵極長度只有幾納米的電路刻在印章(掩膜)上,再將印章蓋在橡皮泥(壓印膠)上,實(shí)現(xiàn)圖形轉(zhuǎn)移后,然后通過熱或者UV光照的方法使轉(zhuǎn)移的圖形固化,以完成微納加工的“雕刻”步驟。

納米壓印替代的是光刻環(huán)節(jié),只有光刻的步驟被納米壓抑技術(shù)代替,其他的刻蝕、離子注入、薄膜沉積這些標(biāo)準(zhǔn)的芯片制造工藝是完全兼容的,能很好的接入現(xiàn)有產(chǎn)業(yè),不用推翻重來。

光刻技術(shù)的本質(zhì)是掩膜版用于對(duì)光刻膠進(jìn)行圖案化,從而實(shí)現(xiàn)圖案化沉積和蝕刻工藝。光刻工藝的最終分辨率由所用光源的波長決定。

而如今業(yè)界依賴的光學(xué)光刻存在諸多局限性:

SDAP、SAQP工藝是二維圖案化解決方案,嚴(yán)重限制了設(shè)計(jì)布局;

由于精度有限,想要將更精密的芯片線路曝光出來,還需要采用多重曝光技術(shù);

提高光學(xué)光刻分辨率主要通過縮短光刻光源波長來實(shí)現(xiàn),盡管光源已從紫外的436nm、365nm縮短到深紫外(DUV)的193nm和極紫外(EUV)的13.5 nm,但在光學(xué)衍射極限限制下,分辨率極限約為半個(gè)波長;

光刻光源波長縮短使得光刻設(shè)備研制難度和成本成倍增長,其成本與規(guī)模化能力已無法與過去25年建立的趨勢(shì)相匹配。

因此,業(yè)界開始寄望于納米壓印光刻技術(shù)。

在芯片制造中引入的任何新光刻技術(shù)都必須提供性能優(yōu)勢(shì)或成本優(yōu)勢(shì)。

與傳統(tǒng)的光刻技術(shù)相比,首先,納米壓印技術(shù)不需要復(fù)雜的光路系統(tǒng)和昂貴的光源,可以大幅降低制造成本。

另外,納米壓印的模板比***用的掩膜版圖案設(shè)計(jì)更簡單,壓印出來的圖案尺寸完全由模板上的圖案決定,所以不會(huì)受到傳統(tǒng)光刻膠技術(shù)中光源波長、光學(xué)衍射的限制和影響。與光刻設(shè)備產(chǎn)生的圖案相比,納米壓印技術(shù)忠實(shí)地再現(xiàn)了更高分辨率和更大均勻性的圖案。

同時(shí),納米壓印技術(shù)只要預(yù)先在掩膜上制作好圖案,即使是復(fù)雜結(jié)構(gòu)也能一次性形成,同時(shí)也避免了傳統(tǒng)光刻工藝中的多次重復(fù)曝光,進(jìn)一步提升了成本優(yōu)勢(shì)。據(jù)日經(jīng)中文網(wǎng)報(bào)道,納米壓印能省掉成本巨大的光刻工序的一部分,與極紫外光刻相比,能將該工序的制造成本降低4成,耗電量降低9成。

此外,納米壓印技術(shù)在三維立體結(jié)構(gòu)加工方面有著它獨(dú)特的優(yōu)勢(shì),傳統(tǒng)的光刻技術(shù)都是基于二維平面的加工方式,三維結(jié)構(gòu)獲取比較困難,同時(shí)可控性較差,但是對(duì)于納米壓印技術(shù),只要制作成模板,就可以批量生產(chǎn)三維產(chǎn)品。

納米壓印技術(shù),突破與挑戰(zhàn)并存

1995年,華裔科學(xué)家周郁(Stephen Chou)教授首次提出納米壓印概念,從此揭開了納米壓印制造技術(shù)的研究序幕。

到2003年,納米壓印作為一項(xiàng)微納加工技術(shù),被納入國際半導(dǎo)體技術(shù)藍(lán)圖(ITRS)。

2009年,美國從事納米壓印基礎(chǔ)技術(shù)研發(fā)的Molecular Imprints公司(MII)曾規(guī)劃將NIL技術(shù)用于32nm邏輯節(jié)點(diǎn)生產(chǎn)制造。但進(jìn)展也未及預(yù)期——據(jù)說是因?yàn)樯a(chǎn)速度慢,而且缺陷率高,資金問題也成為MII發(fā)展技術(shù)的掣肘。

五年后的2014年,佳能收購了MII。實(shí)際早在十年前,佳能從2004年就開始一直秘密研發(fā)納米壓印技術(shù),直到收購MII公司,將其更名為Canon Nanotechnologies,從而進(jìn)入NIL市場(chǎng)。

此后,佳能與東芝聯(lián)合開發(fā)NIL技術(shù)——東芝(2019年,東芝儲(chǔ)存器改名為鎧俠)很早就想將NIL用在平面NAND閃存制造上。不過似乎193nm光刻和多重曝光就能將NAND單元尺寸從120nm縮減到1xnm節(jié)點(diǎn);然而到這個(gè)節(jié)點(diǎn),原有工藝就很難再實(shí)現(xiàn)存儲(chǔ)單元和浮柵的微縮。

因此,NAND開始向3D化演進(jìn),東芝對(duì)于NIL技術(shù)的應(yīng)用也有了轉(zhuǎn)向。大約五六年前,東芝稱非易失性存儲(chǔ)器件的光刻需求,正從更高分辨率走向更低的成本,所以計(jì)劃在3D NAND時(shí)代應(yīng)用NIL。

也大概是自此之后,一直有佳能將納米壓印技術(shù)用于量產(chǎn)存儲(chǔ)芯片的新聞。

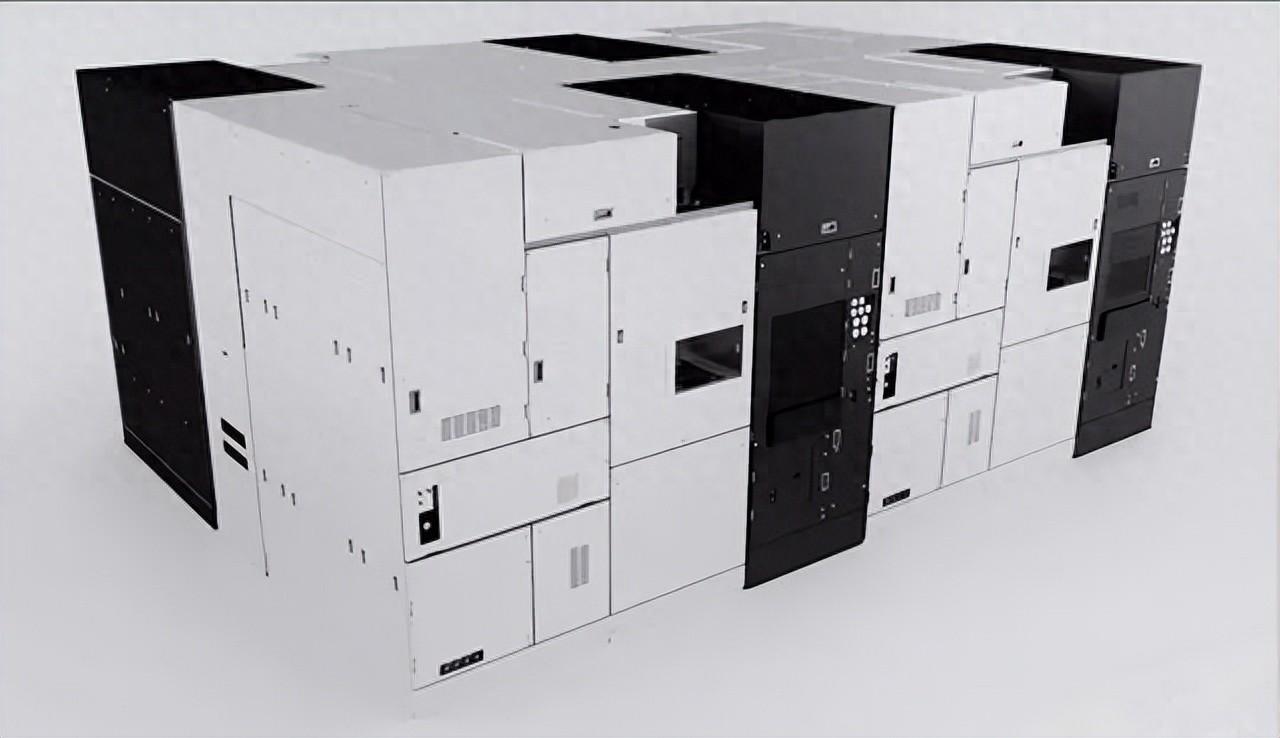

據(jù)了解,佳能最新的納米壓印設(shè)備的參數(shù)指標(biāo)不錯(cuò),套刻精度為2.4nm/3.2nm,每小時(shí)可曝光超過100片晶圓,納米壓印技術(shù)已經(jīng)達(dá)到3D NAND大規(guī)模生產(chǎn)水平和要求。

上文也提到,除了鎧俠之外,SK海力士也從佳能購買了納米壓印設(shè)備,正在進(jìn)行用于3D NAND型閃存生產(chǎn)工程的測(cè)試,這也被認(rèn)為是業(yè)界最尖端制造工藝中使用的EUV***的下一代設(shè)備。

有業(yè)內(nèi)人士表示:“與EUV相比,納米壓印技術(shù)形成圖案的自由度較低,因此預(yù)計(jì)將優(yōu)先用于生產(chǎn)維持一定圖案的NAND型閃存。”SK海力士開始采購設(shè)備也是因?yàn)檫@個(gè)原因。”如果納米壓印設(shè)備實(shí)現(xiàn)商用化,以SK海力士為首的NAND閃存企業(yè)將能夠提高從200層開始的工序難度越來越高的3D NAND閃存領(lǐng)域的生產(chǎn)效率。

另一方面,存儲(chǔ)芯片巨頭三星電子也為了解決引進(jìn)多圖案工藝導(dǎo)致的成本上升問題,迅速導(dǎo)入了EUV***,除此之外還開發(fā)了包括納米壓印技術(shù)在內(nèi)的3-4種解決方案。

除了在NAND閃存領(lǐng)域的探索外,佳能正在嘗試將NIL技術(shù)應(yīng)用到DRAM和CPU等邏輯芯片上。

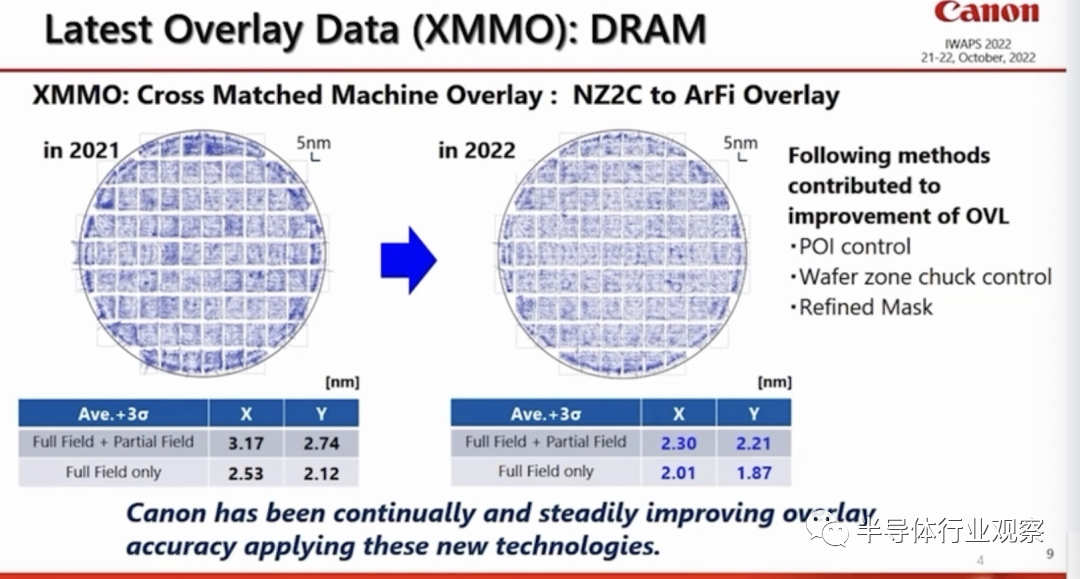

針對(duì)DRAM方面,佳能一直在不斷改進(jìn)套刻精度。使用POI 控制技術(shù)、晶圓區(qū)卡盤控制、精細(xì)掩膜等方式有助于改善套刻精度。

圖源:佳能

高級(jí)的NIL工具和掩膜相結(jié)合可以為許多不同的應(yīng)用提供多種解決方案,佳能展示了2.3nm套刻精度應(yīng)用于各種新技術(shù),主要用在DRAM方面。

在芯片領(lǐng)域,納米壓印光刻更擅長制造3D NAND、DRAM等存儲(chǔ)芯片,與微處理器等邏輯電路相比,存儲(chǔ)制造商具有嚴(yán)格的成本限制,且對(duì)缺陷要求放寬,納米壓印光刻技術(shù)與之較為契合。

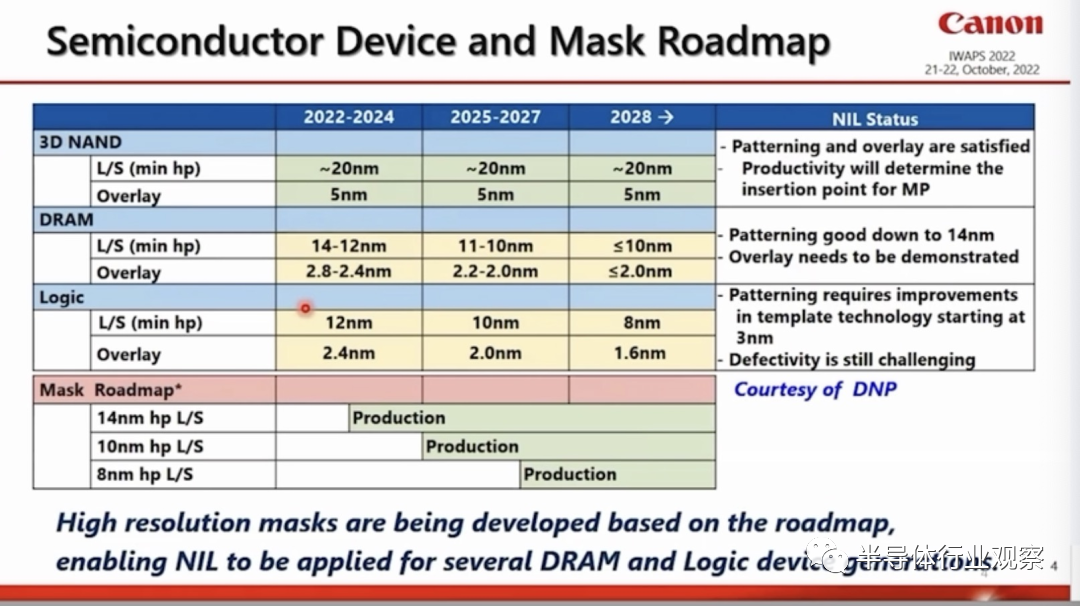

據(jù)佳能在納米壓印設(shè)備未來路線圖顯示,應(yīng)用將從3D NAND存儲(chǔ)芯片開始,逐漸過度到DRAM,最終實(shí)現(xiàn)CPU等邏輯芯片的制造。

圖源:佳能

據(jù)了解,佳能目前量產(chǎn)的納米壓印設(shè)備,能用于生產(chǎn)15納米的芯片,預(yù)計(jì)到2025年,能進(jìn)一步研發(fā)出生產(chǎn)5納米芯片的設(shè)備。初期將率先導(dǎo)入生產(chǎn)NAND、DRAM等,未來還有望導(dǎo)入應(yīng)用在PC和手機(jī)中的需要高階先進(jìn)制程的邏輯IC生產(chǎn)。

為了實(shí)現(xiàn)這一目標(biāo),佳能日前在法說會(huì)上提出將在日本斥資逾500億日?qǐng)A,擴(kuò)增其微影設(shè)備產(chǎn)能,佳能表示該廠房將于2023年興建,預(yù)計(jì)從2025年開始營運(yùn)。該工廠除了生產(chǎn)其現(xiàn)有的***系列產(chǎn)品,還將生產(chǎn)納米壓印光刻設(shè)備。

此前,佳能和鎧俠、DNP(大日本印刷)在納米壓印技術(shù)上就有了不少的合作。DNP 2015年據(jù)說是建立了納米壓印模板(template)的商業(yè)化生產(chǎn)系統(tǒng);而東芝是2016年宣布計(jì)劃用納米壓印來造NAND閃存。

可見,從設(shè)備試產(chǎn)、晶圓廠試運(yùn)行,再到新廠生產(chǎn)線投產(chǎn)設(shè)備,日企欲通過半導(dǎo)體“納米壓印技術(shù)”來追趕ASML的腳步。

此外,目前這一技術(shù)方向的其他設(shè)備供應(yīng)商還包括Nanonex、EVG、SUSS MicroTec、Obducat等歐美公司。

EVG公司日前宣布與凸版印刷分拆成立的光掩膜子公司Toppan Photomask合作,共同開發(fā)NIL 技術(shù),進(jìn)一步加速其在光學(xué)微納制造領(lǐng)域應(yīng)用。納米壓印工藝設(shè)備提供商與納米壓印母版制造商之間的首次合作是該行業(yè)的巨大成就,將幫助行業(yè)迅速擴(kuò)大納米壓印作為先進(jìn)光學(xué)設(shè)備的大規(guī)模生產(chǎn)技術(shù)和組件。

從1995年至今,經(jīng)過不斷的改進(jìn)和技術(shù)突破,納米壓印技術(shù)已經(jīng)被應(yīng)用到LED、屏幕顯示、DNA測(cè)序、AR/VR、傳感等領(lǐng)域。

但應(yīng)用于集成電路制造,尚處于產(chǎn)業(yè)化初期階段。目前,納米壓印技術(shù)在ITRS中被列為下一代32nm、22nm和16nm節(jié)點(diǎn)光刻技術(shù)的代表之一。經(jīng)過近30年的研究,納米壓印技術(shù)已經(jīng)在許多方面有了新進(jìn)展,國內(nèi)外半導(dǎo)體設(shè)備制造商、材料商以及工藝商紛紛開始涉足這一領(lǐng)域。

芯片制造領(lǐng)域,納米壓印技術(shù)挑戰(zhàn)仍在

雖然前面提到了不少納米壓印技術(shù)的優(yōu)勢(shì),甚至被奉為新的行業(yè)希望,但是納米壓印技術(shù)距離大規(guī)模商業(yè)化量產(chǎn)還有一些短板沒有補(bǔ)足。

良品控制:納米壓印由于是晶圓和掩膜直接接觸,容易出現(xiàn)電路上混入細(xì)小垃圾和灰塵等的殘次品,要實(shí)現(xiàn)實(shí)用化,必須進(jìn)行制造技術(shù)和運(yùn)用方面的改良。

模板壽命低,更換成本高:不管是DUV光刻、EUV光刻還是納米壓印,最貴的耗材都是掩膜版或者壓印模板。納米壓印的模板,因?yàn)槭切枰苯咏佑|壓印膠工作的,在接觸的過程中,難免會(huì)有各種各樣的損傷或者污染,縮短模板壽命。

對(duì)準(zhǔn)復(fù)雜:壓印模板需要與承載壓印膠的基臺(tái)精確對(duì)準(zhǔn)與貼合,需要精密的機(jī)械裝置配合檢測(cè)設(shè)備實(shí)施壓印過程。然而現(xiàn)有納米壓印設(shè)備在平行與垂直對(duì)準(zhǔn)方面缺少高精密的調(diào)準(zhǔn)機(jī)構(gòu)。雖然我們可以沿用紫外光刻上的光學(xué)對(duì)準(zhǔn)、或者莫爾條紋技術(shù)做對(duì)準(zhǔn),但是納米壓印不僅有固化、還有垂直方向的壓印運(yùn)動(dòng)過程,所以會(huì)帶來多方向的偏差。

這幾個(gè)問題,其實(shí)不能全說是納米壓印技術(shù)的問題,降低工藝成本、提高良品率和提高生產(chǎn)效率對(duì)于發(fā)展初期的***來說也是同樣要面對(duì)的問題,任何一項(xiàng)技術(shù)從實(shí)驗(yàn)室走向成熟,都會(huì)面對(duì)這些問題,都需要在發(fā)展過程中解決這些問題。

NIL能否替代EUV光刻?

回顧芯片光刻產(chǎn)業(yè)歷程,21世紀(jì)的前20年里,由于全球芯片產(chǎn)業(yè)鏈條在浸入式DUV、EUV等投影式光刻技術(shù)的持續(xù)巨大投入,投影式光刻成為IC制造的主流技術(shù),誕生了荷蘭ASML光刻設(shè)備巨頭,以及應(yīng)用層面的臺(tái)積電、三星等國際芯片加工企業(yè),納米壓印光刻逐漸退出IC制造技術(shù)的競(jìng)爭(zhēng),進(jìn)入沉默期。

而隨著產(chǎn)業(yè)向前發(fā)展,DUV、EUV***等系統(tǒng)復(fù)雜度、技術(shù)瓶頸和成本問題等日益突出,納米壓印技術(shù)似乎又迎來了新的目光。

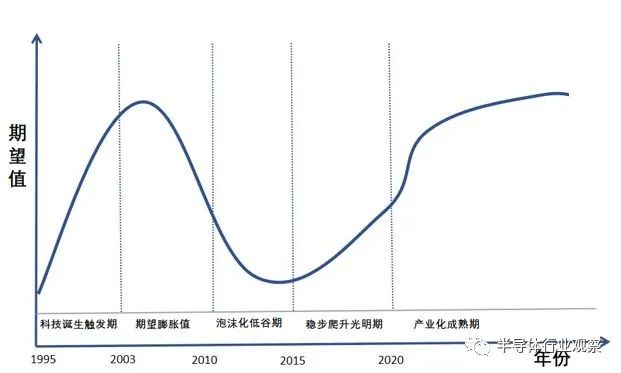

根據(jù)Gartner提出的新科技技術(shù)成熟度曲線,綜合技術(shù)發(fā)展歷程中的專利、論文、市場(chǎng)情報(bào)等數(shù)據(jù),以年度和期望值維度,繪制了納米壓印技術(shù)產(chǎn)業(yè)化曲線。

納米壓印技術(shù)產(chǎn)業(yè)化曲線

科技誕生觸發(fā)期:自1995年納米壓印技術(shù)提出后,引起學(xué)術(shù)界和產(chǎn)業(yè)界廣泛關(guān)注和跟進(jìn),目前領(lǐng)先的技術(shù)和設(shè)備提供商大多在這一階段進(jìn)入。

期望膨脹期:2003年,納米壓印技術(shù)首次納入國際半導(dǎo)體藍(lán)圖(ITRS),技術(shù)的研究和期望進(jìn)入高潮,這一時(shí)期,納米壓印相關(guān)設(shè)備被科研機(jī)構(gòu)大量采購。

泡沫化低谷期:受制于工藝不成熟,產(chǎn)業(yè)化不及預(yù)期。一批企業(yè)倒閉或被收購,標(biāo)志性事件是2014年佳能收購MII。但是這段時(shí)間,納米壓印大面積、連續(xù)生產(chǎn)的相關(guān)技術(shù)被開發(fā)出來,在生產(chǎn)光子晶體LED芯片領(lǐng)域?qū)崿F(xiàn)產(chǎn)業(yè)化。

穩(wěn)步爬升光明期:技術(shù)工藝逐步突破,在LED、微流控、MEMS、AR等領(lǐng)域?qū)崿F(xiàn)產(chǎn)業(yè)化應(yīng)用。國內(nèi)企業(yè)也加大納米壓印技術(shù)的研發(fā)和應(yīng)用布局。

產(chǎn)業(yè)化成熟期:2021年后,隨著工藝成熟和下游應(yīng)用領(lǐng)域的突破發(fā)展,納米壓印技術(shù)或?qū)⒂瓉泶竺娣e產(chǎn)業(yè)化。

TechNavio數(shù)據(jù)顯示,2026年納米壓印市場(chǎng)有望達(dá)到33億美元,2021年至2026年年復(fù)合增長率可達(dá)17.74%。納米壓印市場(chǎng)雖然沒有想象中那樣大,但整體正逐漸走強(qiáng)。

納米壓印技術(shù)有著其獨(dú)特的優(yōu)勢(shì),也有相對(duì)應(yīng)的缺點(diǎn),在未來的科研生產(chǎn)中,需要進(jìn)一步的優(yōu)化工藝條件,幫助拓展改進(jìn)納米壓印技術(shù)的應(yīng)用。

最后回到本篇內(nèi)容的核心——在芯片制造領(lǐng)域,雖然日本最早完成實(shí)踐,但能否替代EUV光刻呢?

老實(shí)來講,難度是非常大的,除非臺(tái)積電、三星、英特爾、SK海力士等行業(yè)大廠放棄成熟技術(shù)轉(zhuǎn)戰(zhàn)納米壓印技術(shù)。其實(shí)從行業(yè)動(dòng)態(tài)也能看到,每隔幾年都會(huì)有納米壓印光刻即將突破的消息,但每次又延后進(jìn)入產(chǎn)業(yè)的時(shí)間。

一切信號(hào)都在表明這項(xiàng)技術(shù)的不容易。但未來,當(dāng)光學(xué)光刻真正達(dá)到極限難以向前時(shí),納米壓印技術(shù)或?qū)⑹且粭l值得期待的路線,而那時(shí),芯片制造或許也會(huì)迎來全新的范式,一切都會(huì)被顛覆。

畢竟,沒有一種技術(shù)能夠長期存在,倘若有,那也只是因?yàn)槿藗冞€沒有來得及發(fā)現(xiàn)新的東西來取代它而已。

審核編輯 :李倩

-

晶體管

+關(guān)注

關(guān)注

77文章

9682瀏覽量

138080 -

納米

+關(guān)注

關(guān)注

2文章

696瀏覽量

36976 -

光刻機(jī)

+關(guān)注

關(guān)注

31文章

1150瀏覽量

47378 -

EUV

+關(guān)注

關(guān)注

8文章

605瀏覽量

86004 -

ASML

+關(guān)注

關(guān)注

7文章

718瀏覽量

41228

原文標(biāo)題:納米壓印,終于走向臺(tái)前?

文章出處:【微信號(hào):WW_CGQJS,微信公眾號(hào):傳感器技術(shù)】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

納米壓印光刻技術(shù)的詳細(xì)介紹

就JXTG在功能性材料和納米級(jí)別壓印技術(shù)上做了深入交流和探討

Inkron對(duì)納米壓印材料和元件開發(fā)設(shè)備進(jìn)行了戰(zhàn)略投資

納米壓印技術(shù)及UV NIL 與 Embossing 工藝的差別

納米壓印光刻,能讓國產(chǎn)繞過ASML嗎?

蘇州新維度微納科技有限公司舉行落成儀式,聚焦納米壓印

璞璘科技獲數(shù)千萬元天使輪融資,聚焦納米壓印技術(shù)

什么是納米壓印技術(shù)?能否取代***?

佳能押注納米壓印技術(shù) 挑戰(zhàn)***老大ASML

佳能推出5nm芯片制造設(shè)備,納米壓印技術(shù)重塑半導(dǎo)體競(jìng)爭(zhēng)格局?

佳能預(yù)計(jì)到2024年出貨納米壓印光刻機(jī)

基于納米壓印超構(gòu)透鏡陣列的增強(qiáng)現(xiàn)實(shí)方案

納米壓印技術(shù)的分類和優(yōu)勢(shì)

納米壓印,終于走向臺(tái)前?

納米壓印,終于走向臺(tái)前?

評(píng)論