毋庸置疑,UVM大大提高了我們開發驗證平臺的效率。但同時,熟練掌握UVM搭建驗證平臺也并不是一件容易的事情。同時由于不同驗證工程師搭建環境的風格不太一致,所以在一個項目中常會出現不好管理,甚至前后不一相互矛盾的UVM代碼。對于這些問題UVM 代碼生成器基本都可以解決,更為關鍵的是,這對于項目的開發效率提高也是一件極有意義的事情。

簡單的UVM代碼生成器在2011年就有了雛形,最初是Cadence的Jim McGrath開發的,它在2011年9月16日作為UVMWorld投稿上傳。后來腳本經由ChristophSühnel、David Long以及John Aynsley進行了修改。當前版本的簡單UVM代碼生成器 已獲得了Apache 2.0開源認證。

這篇文章就旨在談論UVM代碼生成器的優點,及開發使用時需要注意的問題。

一.模板代碼應具有的特性

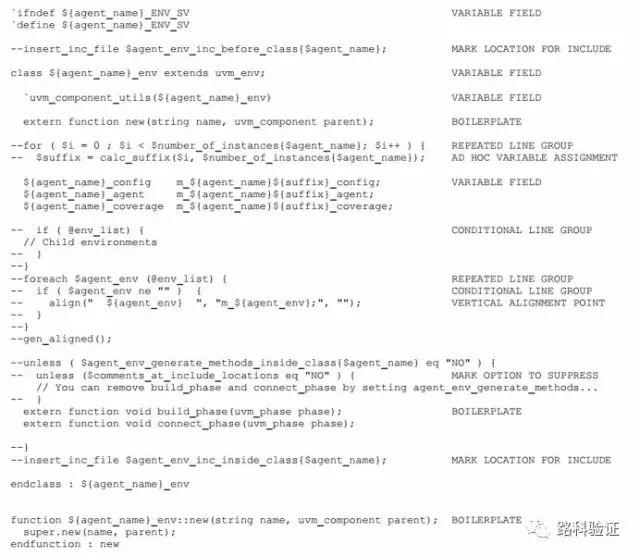

每個UVM測試平臺代碼庫可以分為兩部分,封裝好且基本保持不變的樣板代碼部分和需要用戶自定義的代碼部分。基于此,就要求我們所生成的代碼能夠包含相當多的用戶自定義元素。理論上,我們生成代碼的基本原則是,先調用UVM,定義好一些結構語法都正確的SystemVerilog模板代碼,然后我們基于此進行復制和配置得到我們的代碼。這就要求我們的模板代碼至少要能包含以下幾個元素:

- 能夠根據用戶自定義的名稱來替換的變量字段。這里的替換主要是指代碼塊名稱的替換。

- 循環變量,代碼常要求可以循環遍歷任意的agent或配置等,這就要求有循環變量的存在。

- 條件變量,某些代碼塊是否存在是需要用戶自定義的。

- 任意嵌套重復的語句

- 標記可以包含用戶自定義的代碼片段(使用“include”或“inline”)

- 標記自動生成方法被禁用的部分

- 以及一些其他的特定用法,詳見下圖

我們使用這些變量元素表明,我們期待自動生成的UVM代碼是具有一定靈活性的,不能僅僅簡單復制一段源文件來實現。我們希望以腳本來實現UVM 代碼生成器的功能。這個代碼生成器會生成一系列的class、package、module、和interface。

二.代碼生成器的實現

使用簡單代碼生成器實現自動生成UVM代碼,生成器腳本文件可以按照按以下流程走。

- 解析命令行開關

- 解析通用的配置文件,設置內部變量

- 檢查這些設置相互之間的約束

- 對于每個 interface/agent

- 解析配置文件并配置內部變量

- 檢查這些設置的所有相互約束

- 根據代碼模板和內部變量生成代碼

- 根據代碼模板和內部變量生成頂層代碼

- 生成仿真腳本

如上所述,使用一些配置文件對變量、對代碼進行約束,然后基于模板代碼生成目標代碼,這一方法能夠使得代碼具備一定的靈活性。除了用戶定義的代碼片段可能會引入的錯誤之外,我們原本生成的生成的代碼應該是完整的,可以使用生成的仿真腳本運行操作。

讀者可以自行嘗試前文提到的開源代碼生成器,這種代碼生成器的優點在于

- 它可以生成完整且可以運行的代碼

- 是開源的,可以自由使用

- 已經經過測試,并擁有自己的回歸測試套件

當然,本文的目的不是說服你使用這個特定的代碼生成器,而是讓你更好地了解UVM代碼生成的基本內在步驟。

**代碼生成器在實現特定的代碼時,要考慮哪些要求呢?**如前所述,每個工程師的代碼風格都不盡相同,當在文件級別考慮實現我們的代碼生成器時,以下這些問題我們就一定要注意到了:

- 目錄結構組織和文件命名

- 在生成的每個文件的頂部插入標準頭文件

- 在每個編譯單元周圍插入條件編譯器

- 使用`include指令包括類代碼將類組織成包

- 縮進,間距,對齊和空白行規范

- 變量和類型的命名約定,具有標準前綴和后綴名稱

- 將UVM對象的字符串名稱與相應的變量名匹配

- 每個類中的聲明和語句的常規排序

在結構層面上,UVM 代碼生成器也有一些需要考量的地方 ,具體可如下實現:

- 將實例化DUT的SystemVerilog模塊與實例化UVM test的模塊分開

- 支持頂層agent,agent中包含這一層級的envs及多個agent的實例化

- 使用配置對象,每個agent對應一個,頂級的env對應一個

- 如何配置test和頂層env呢:1,修改配置對象并在test中設置factory overrides 2,在env中實例化根寄存器模型,并在啟動底層virtual sequence

本文中的要點不是為了在UVM對testbanch的生成方法中作出具體的選擇,只是給出參考,選擇任何類似可行的的結構都是有效的。

在更詳細的層面上,簡單的UVM代碼生成器就需要對UVM的具體feature進行選擇了,如下:

- 選取哪些UVM component 基類進行擴展呢?

- 選取使用哪些UVM marcro呢?

- 全部使用factory 方法T :: type_id :: create來實例化所有組件,序列和事務嗎?

- 配置類中包含的默認變量集的選擇,需要check_enable和coverage_enable嗎?

- 從頂層模塊通過配置數據庫傳遞virtual interface到agent要選擇哪種機制呢?

- 在哪里為driver和monitor中的interface賦值呢?

- 通過什么機制來設置和替換is_active變量呢?

- 是否要使用用戶自定義的sequencer呢?還是直接使用UVM_sequencer?

- 諸如此類的其他feature

上述都是只代表了常規的編碼選擇,除此之外,代碼生成器還要求對另外一些文件的自動化生成,這些文件手寫起來是相當費時的。

- 產生一個test封裝文件,其中包含DUT實例化、DUT和interface之間的連接。

- 產生每個tranction類都會用到的通用方法,包括打包、解包等

- 為寄存器模型產生合適的adapter 和predictor

基于提高生產力的考慮,UVM 代碼也要生成一些可供擴展的代碼塊,如下

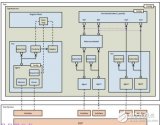

上圖顯示了一個簡單UVM代碼生成器能夠產生的結構類型的示例,包括多個DUT接口和相關agent,嵌套envs以及寄存器塊,參考模型和記分板的實例化。 請注意,代碼生成器不會生成寄存器模型,參考模型或記分板的內容。 寄存器模型通常來自單獨的生成器,現在可有許多文章對此進行討論。參考模型則是必須要手動編碼的。

三**.總結**

代碼生成器的好處是不言而喻的:

- 對于新用戶:代碼生成器可以迅速生成有效的代碼示例模板。對于新手搭建和理解環境的好處是巨大的。

- 對于所有用戶:提高了生產效率,避免了環境搭建中出現的繁瑣的重復和容易出錯的工作。保持了代碼風格的一致性,自動生成的代碼風格一定是統一的,避免了因代碼風格問題導致的意外,使測試平臺代碼更易讀、易維護。

本文只起到拋磚引玉的作用,提出了要實現自動生成UVM代碼的生成器需要考慮的問題及參考。

對UVM代碼生成器的功能是沒有上限的,應該實現多復雜的功能,取決于你們的需要和付出回報比。代碼生成器總是要不斷向前發展的,以改進編碼風格和處理新的問題,同時該進的時候還要注意要能能向后兼容配置文件,保證隨時可以重新生成整個代碼庫。

-

寄存器

+關注

關注

31文章

5357瀏覽量

120637 -

UVM

+關注

關注

0文章

182瀏覽量

19189 -

代碼生成器

+關注

關注

0文章

25瀏覽量

9139 -

Verilog語言

+關注

關注

0文章

113瀏覽量

8278 -

DUT

+關注

關注

0文章

189瀏覽量

12419

發布評論請先 登錄

相關推薦

AllJoyn C++代碼生成器

介紹一下ABOV提供的代碼生成器

STM32庫函數代碼自動生成器V1.2

YIE002開發探索10-隨機數生成器

談談UVM代碼生成器的優點及開發使用時需要注意的問題

談談UVM代碼生成器的優點及開發使用時需要注意的問題

評論