HC89S003AF4/HC89S001AJ4是一顆采用高速低功耗 CMOS 工藝設計開發的增強型 8 位單片機,內部有 16K Bytes FLASH 程序存儲器,256Bytes IRAM+768Bytes XRAM,最多 18 個雙向 I/O 口,5 個 16 位定時器 /計數器,3 組 12 位帶死區控制互補 PWM,1 路 8 位 PWM,2 個 UART,1 個 SPI,1 個 IIC,16 個外部 中斷,16+2 路 12 位 ADC,1 個低壓檢測模塊,四種系統工作模式和多個中斷源。

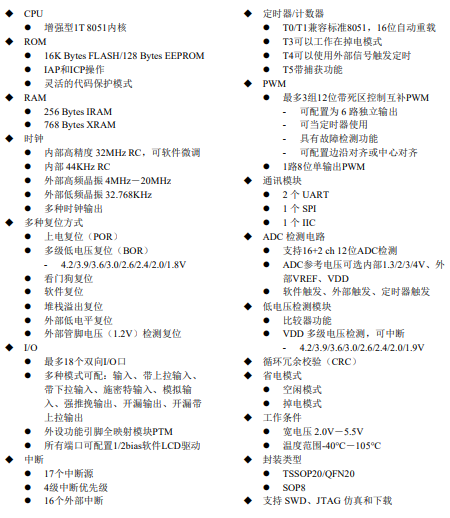

特點→

V:runzexin-18

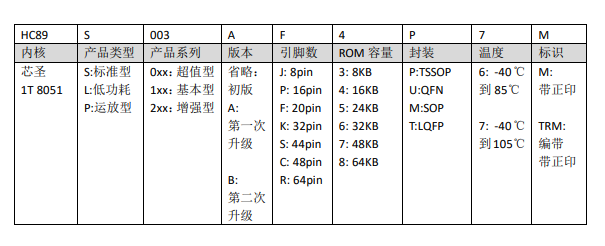

命名規則

1. 為保證系統的穩定性,必須在VDD和GND之間接一電容(容值須大于或等于0.1μF)。

2. 可以直接燒錄HC89S003F4的燒錄文件,但需要將HC-PM51燒錄器的固件版本升級到最新版。

3. P2.7引腳出廠時默認為復位管腳,端口模式為施密特輸入帶上拉,可以通過配置代碼選項將此口配 置為普通IO引腳。

4. 在進行IAP操作時,不響應任何中斷。

5. ADCEN 置 1 或切換轉換通道后,建議延時 20us 后再啟動 ADC 轉換,如果外部輸入阻抗很大時, 需要延長這個時間。

6. 當 ADC 的參考電壓為 VDD 時,ADC 轉換時鐘可以為 8MHz,一次轉換只需要 15 個 ADC_CLK, 這樣可以得到最快的 ADC 轉換速度。

7. P2.7、P2.5、P2.4、P2.3 這四個端口的模式配置和其他端口的不一樣,請仔細看 7.4.6 小節。

8. 使用 PWM3 時,要先配置時鐘分頻、周期、占空比等寄存器,最后再使能 PWM3 模塊。

9. UART2 在使用全雙工時,需要配置 CPU 頻率為 16MHz 以上,波特率配置 9600 或以下,而且在 UART2 中斷服務函數里盡早清零 TI 或 RI,請參考相關例程。

10. 在LVD中斷中,若要關閉比較器或LVD中斷,應先禁止 LVD/比較器,再失能LVD中斷允許位。

11. 在使用LVD比較器功能的時候,如果比較器輸出狀態(CMPSTA)為高(即比較器正端電壓大于負 端電壓),則芯片無法進入掉電/空閑模式。

12. QFN20 的封裝片中間的焊盤是與 PIN5(VDD)相連接的。

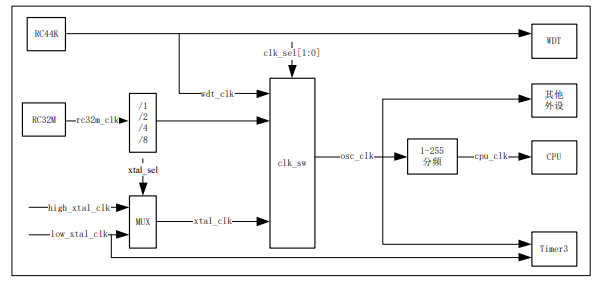

HC89S003A/001A 單片機系統時鐘有 4 種時鐘源可選:

? 外部高頻晶振時鐘(4MHz~20MHz)

? 外部低頻晶振時鐘(32.768KHz)

? 內部高頻 RC 時鐘(32MHz)

? 內部低頻 RC 時鐘(44KHz)

用戶選擇后的系統時鐘(如果選擇的是內部高頻 RC,則經 RC32M_DIV[1:0]分頻后的時鐘)記做 osc_clk,其頻率為 Fosc,周期為 Tosc,主要用于外設模塊,osc_clk 可以進行 1-255 之間任意值的分頻, 分頻后的時鐘記做 CPU 時鐘,其頻率為 Fcpu,周期為 Tcpu。

芯片上電復位后,默認選擇內部高頻 RC 作為系統時鐘,其 Fosc 為 4MHz,Fcpu 為 2MHz,可以通過 配置相關寄存器改變 osc_clk 和 cpu_clk 的頻率。

CPU 最高可以運行在 16MHz 頻率下,如果所選時鐘源頻率高于 16MHz,需要對其進行分頻,使 CPU 時鐘頻率等于或低于 16MHz。

系統時鐘框圖

本文章僅展現了產品一部分內容 具體內容可咨詢。

審核編輯黃宇

-

單片機

+關注

關注

6039文章

44575瀏覽量

636394 -

adc

+關注

關注

98文章

6512瀏覽量

545016

發布評論請先 登錄

相關推薦

STM8S003F的作用是什么,如何編寫單片機程序去控制?

性價比高的8位單片機有哪些?

有哪些便宜的8位單片機可供選擇?

CMS8S69xx可代替STM8S003F3P6 5.5V多個封裝

stm32單片機引腳介紹及功能

XL32F003單片機 M0+內核 主頻48M,64 K flash加8K SRAM存儲器

STM8AF5288T不帶ADC1嗎?

用STM8S003單片機做2路ADC實驗,單次模式可以分別讀取2路ADC嗎?

能否直接用STM8S003替代STM8S103,這樣做有哪些風險?

STM8S003F3如何切換到GPIO模式呢?

請問STM8S外設模塊的GPIO引腳如何配置?

芯圣SDK工具,讓開發更方便——SDK-HC89S105A

芯圣SDK工具 讓開發更方便——HC89S103K6

HC89S003AF4/HC89S001AJ4 20/8 引腳 8 位 ADC 型 FLASH 單片機 外設功能引腳全映射

HC89S003AF4/HC89S001AJ4 20/8 引腳 8 位 ADC 型 FLASH 單片機 外設功能引腳全映射

評論