隨著后摩爾時代的到來, AI、5G、自動駕駛等眾多熱門應用不斷涌現,芯片規模呈指數級增長,十億門甚至幾十億門的芯片設計比比皆是,芯片規模越大、工藝節點越高,流片成本也是水漲船高。為了提高流片成功率,EDA驗證成為高端芯片設計必不可少的環節,貫穿從設計到量產的全流程。驗證在整個芯片開發過程中,投入時間最長、耗費資源最多,也面臨著諸多技術挑戰。如何解決大芯片的驗證痛點,成為芯片設計公司的關注焦點。

一、EDA驗證為何至關重要

如今芯片設計軟件已走過了60多年的浩浩蕩蕩發展史,其過程是從輔助繪圖CAD,到能夠仿真驗證的CAE階段,再到模塊化的自動化工具EDA。EDA作為集成電路設計的基礎工具,隨著大規模集成電路、計算機和電子系統設計技術的不斷發展,發揮了至關重要的作用,已經從輔助性技術成為了芯片產業的核心支柱技術之一,是IC設計最上游、技術壁壘最高的部分。沒有EDA軟件的支持,芯片的設計成本將幾十上百倍地增加。

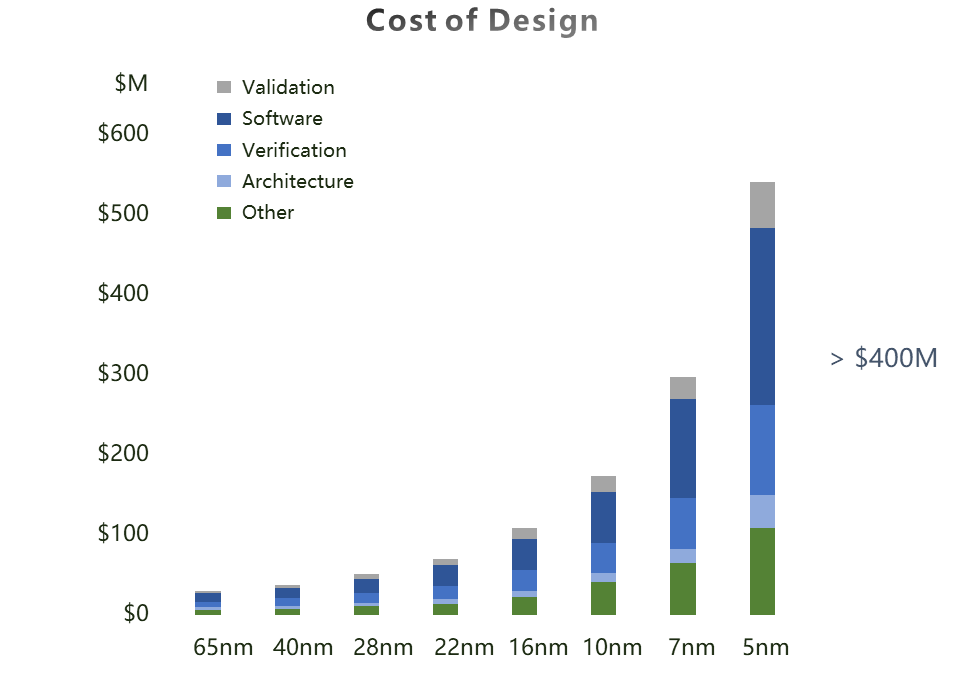

根據應用場景的不同,EDA工具的使用主要分為設計、驗證、封裝、制造等幾大類,其中驗證(Verification)在EDA工具中覆蓋從前端邏輯設計、到后端物理設計、最終制造量產的整個環節,隨著芯片設計成本越來越高昂,以及集成度的提高,復雜性也在大幅提升,通過驗證發現所有的設計缺陷和錯誤已命系成敗,驗證EDA工具已成為責任擔當。

數據來源:IBS, Design Activities & Strategic Implications, July 2018

從驗證來看,EDA軟件非常復雜,技術壁壘也很高,最重要的是不僅要開發出工具,而且一定要不斷迭代,要有生態和客戶的支持,才能形成閉環。盡管國際三大巨頭經過多年的積累,在驗證市場已有相應的成熟產品,但如果想進一步創新和迭代,則必須要考慮向前兼容,這無疑是一個沉重的歷史包袱。這也促成了中國在驗證EDA領域破局的機會。

二、大芯片有哪些驗證痛點

大芯片一般指大型SoC芯片,包含AI engine、CPU、GPU等,多使用12nm以下先進制程,應用于機器學習、自動駕駛、圖像識別、自然語言處理、數據中心等領域。對大芯片的驗證,是一項復雜且具有挑戰的任務,主要痛點體現在如下四個方面。

第一,驗證工具需要支持足夠大的芯片設計容量。大芯片的流片成本居高不下,流片失敗的損失難以估量,因此驗證工具需要與時俱進,能夠靈活堆疊,從而支持超大規模的芯片設計,并且保障正確性、可靠性。

第二,驗證時間需要盡可能縮短。有些驗證工具的自動化程度較低,部分流程需要手動干預,這將耗費工程師的精力,影響芯片上市時間。比如,在原型驗證方面,因芯片設計過大,需要進行分割后才能驗證,傳統方法是采用手動分割,既費時費力,又極易出錯,自動、智能的分割方法及工具是必然趨勢。

第三,需要高效的調試工具。一旦出現問題,需要盡快找到設計中的問題點進行調試,實現最快的迭代速度。面對復雜芯片,有些驗證平臺的觀測性和調試性較差,影響驗證效率。此外,調試工具在迭代過程中,還要不斷引入方法學和流程的創新,不僅支持功能的調試,還應拓展至功耗、覆蓋率、安全等方面的調試;不僅要支持不同設計層級如RTL和Gate級的需求,還要支持事務級和系統級的驗證調試。

第四,流片前的驗證算力峰值需求如何解決。IC企業流片前存在3-6個月的算力峰值需求,芯片驗證需要大內存、高主頻的算力以及高性能存儲等。如果本地搭建,會耗費大量人力、物力、財力,還會存在計算、存儲等硬件資源的限制,加上耗時的采購與部署流程,導致驗證工程師難以在預定上市時間內完成所有期望的作業。

三、FPGA原型驗證是大芯片驗證的首選方法

面臨這些痛點,FPGA(現場可編程門陣列)原型驗證已發展成為芯片公司首選的驗證方法。FPGA原型驗證,是基于FPGA的一種芯片功能驗證方式。它利用了FPGA可以多次擦寫的特性,在芯片RTL代碼開發的過程中,將RTL代碼綜合到FPGA上來做芯片的功能驗證。其目的是在芯片流片之前,為芯片開發團隊提供一個可以反復迭代的邏輯驗證平臺。在芯片設計定型之后,流片回片之前,為軟件開發團隊提供一個可以提前開發軟件功能的硬件環境,縮短芯片回片之后產品的上市時間。這個驗證環境能夠讓芯片驗證與軟件驗證并行,確保芯片軟硬件功能在真實應用場景中準確無誤。

FPGA通過級聯,即可輕松實現大規模的芯片驗證;并且運行速度高,特別適合系統級驗證。再進一步通過級聯數臺FPGA原型驗證仿真器,即可搭建EDA云數據中心,通過云端彈性算力,滿足IC企業峰值算力需求,并能有效降低企業的IT投入和運維成本,提高芯片設計和驗證的效率和質量,還可以實現跨地域、跨平臺、跨設備的協同工作。

四、相比其它驗證手段,FPGA原型驗證有何優勢

現代SoC芯片是一個軟硬件協同運行的系統。上面有復雜的軟件運行,和芯片硬件共同實現各種功能。與芯片協同工作的軟件系統,其設計、開發和驗證工作需要和芯片設計驗證工作同步展開。這樣才能保證芯片功能正確,降低芯片流片失敗的風險,縮短產品的上市周期。

為了保證芯片功能正確,在芯片RTL代碼開發之后,需要經過一系列的驗證流程。常見的數字芯片驗證手段,包括邏輯功能仿真、形式化驗證、硬件仿真和FPGA原型驗證等。

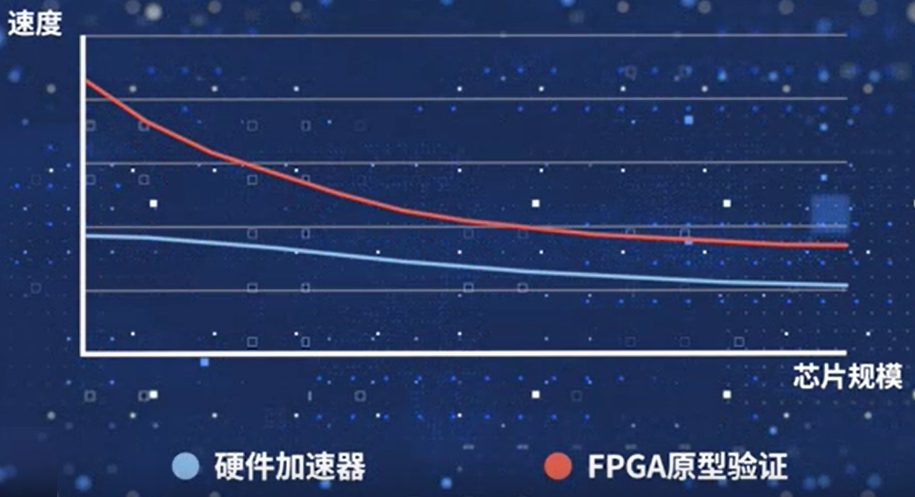

這幾種常見的數字芯片驗證手段中,FPGA原型驗證技術是最適合芯片軟硬件協同功能的驗證技術之一。FPGA原型驗證平臺可以提供調試芯片軟件必要的真實物理接口和硬件環境。這是邏輯功能仿真和形式化驗證無法提供的。相比硬件加速器,FPGA原型驗證平臺的軟件運行速度快一個數量級,很大程度縮短了軟件運行時間和驗證迭代的周期,優化接口邏輯運行頻率可以使之對接真實設備,同時也使得軟硬件開發驗證并行成為可能。在芯片驗證流程中,FPGA原型驗證技術是軟硬件協同功能驗證的必備解決方案,具有顯著的不可替代性。

因此,FPGA原型驗證技術,作為主流且成熟的芯片驗證方法,已成為數字芯片公司不可或缺的驗證工具。

五、合見工軟數字驗證全流程及新一代時序驅動FPGA原型驗證系統UV APS

上海合見工業軟件集團有限公司(簡稱“合見工軟”)作為自主創新的高性能工業軟件及解決方案提供商,核心是數字芯片驗證的全流程支持,實現從點到面的突破。合見工軟現已推出完整的數字芯片驗證全流程工具,包括:商用級別邏輯仿真器UVS,時序驅動的高性能原型驗證系統UV APS、數字功能仿真調試工具UVD、大規模功能驗證回歸測試管理平臺VPS、即插即用的混合原型系統級IP驗證方案HIPK。同時合見工軟還對上海阿卡思、孤波科技進行戰略投資,補充形式化驗證工具和半導體自動化測試工具為全流程驗證平臺。

其中,2022年6月發布的新一代時序驅動FPGA原型驗證系統UniVista Advanced Prototyping System(UV APS)為合見工軟旗艦產品。自產品面世以來,已經在高性能計算、5G通信、GPU、人工智能、汽車電子等領域的IC企業中成功部署應用。

UV APS單套設備使用了4片 FPGA,可靈活堆疊,最大容量支持25套設備級聯(100片FPGA互聯)。集成智能化、自動化的全流程編譯軟件 APS Compiler,為芯片設計者提供了高效的驗證方式,降低在驗證階段的時間成本;同時提供豐富的FMC接口子卡,以適配各種接口驗證,提供充足的One-Bank互聯通道,以支撐系統擴展;配合深度調試方案,縮短測試周期,加快芯片上市。

圖 新一代時序驅動FPGA原型驗證系統UV APS

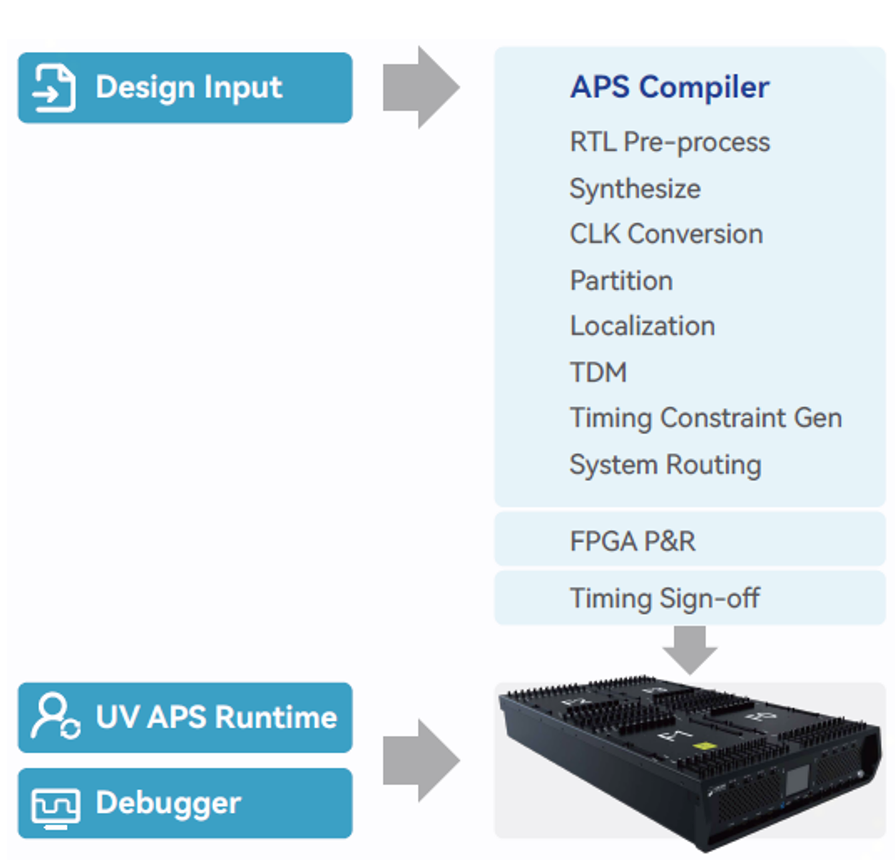

創新點一:創新自研的時序驅動全流程編譯軟件APS Compiler

UV APS集成了創新自研的時序驅動全流程編譯軟件APS Compiler,在性能和自動化程度方面具有明顯優勢。

在性能上:APS Compiler內嵌時序驅動分割引擎,可通過大范圍的TDM Ratio自動最優求解,輕松處理多達100顆FPGA的設計容量,讓邏輯電路運行速度更快。同時,APS Compiler還能實現自動化時序驅動分割、片間走線、邏輯本地化、MCP(多周期路徑)分析等,使時序驅動流程更完整。對于典型的SoC設計,APS Compiler的驗證性能高達20+MHz,可輕松支持10億門以上設計的分割需求。

在自動化程度上:APS Compiler可基于RTL Module的時序驅動分割算法,提供全自動和人工向導兩種模式,助力實現高效驗證。而對于FPGA不能支持的設計單元,比如多端口存儲(Multi-port Memory)、多維數組、跨模塊引用(XMR)、三態門(Tri-state)等,業界一些主流工具會要求用戶修改RTL代碼,而UV APS可實現自動化轉換。

圖 UV APS自動化時序驅動編譯流程

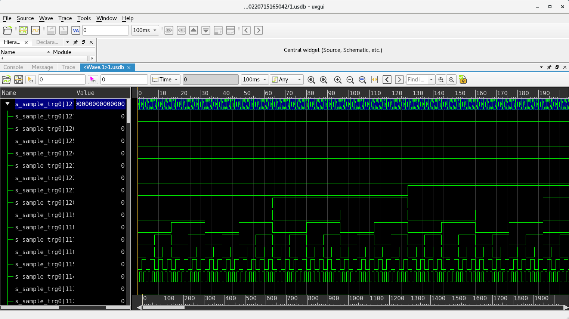

創新點二:多樣化調試手段

在原型驗證過程中,調試功能是不可或缺的。傳統FPGA原型驗證平臺受限于自身容量,其觀測性和調試性較差,而UV APS在這兩方面做出了較大提升。

UV APS中的信號波形采集工具不占用FPGA內部存儲空間,通過可配置的Trigger條件,抓取設計內部信號波形,存儲到外部專用Memory上。可支持多種邏輯組合的觸發條件,波形顯示清晰便于直觀查看。

同時,UV APS支持FPGA芯片回讀捕獲調試,可讀取片內寄存器值;Back Door功能可實現后門讀寫,有效避免用戶頻繁地重啟系統;支持多FPGA、多觸發條件調試,多時鐘域信號采集至單一波形文件,多波形單一窗口組合顯示。此外,ECO功能通過利用VIVADO工具的增量布局布線特性,可以加快周轉時間。這些調試方式都能極大地提高調試效率,大幅縮短測試周期和上市時間。

圖 UV APS豐富的Debug功能

創新點三:大容量、拓展靈活的硬件系統

FPGA原型驗證平臺作為一個生產工具,其硬件系統的大容量與可拓展的靈活性都將直接影響芯片驗證的進度。

在容量方面,UV APS硬件系統能夠支持最多25臺設備級聯。

在靈活性方面,UV APS硬件系統中單顆FPGA便可支持46路以上高速GTY收發器,速度高達28Gbps,支持多路全局可編程時鐘。此外,UV APS中單顆FPGA還擁有超過1700個IO接口,并提供FMC外部標準擴展接口和One Bank連接器,可滿足用戶的互聯需求。

UV APS硬件系統還提供了自檢功能,同時支持上位機軟件控制上電、斷電功能,并且帶有:系統狀態監測、過流過壓保護、溫度監測等一系列的安全保護措施。

創新點四:適配典型應用場景的解決方案

合見工軟UV APS同時提供了面向多種行業應用的原型驗證子卡、Memory Model、Speed Adaptor及快速定制服務;UV APS支持PCIe Gen5、DDR5、HBM2e、HBM3、MIPI、LPDDR5、Gigabit Ethernet等高性能接口速率適配,支持虛擬原型混合驗證等一系列適配多種典型應用的解決方案,以滿足用戶對原型驗證的各種復雜場景需求。

六、大芯片驗證算力集群解決方案——企業級EDA云數據中心

區別于傳統的云數據中心,EDA云數據中心需要搭建專用的硬件仿真器,來進行大規模的芯片驗證。其次,數據安全性對IC企業尤為重要,必須確保芯片設計、驗證是在安全的工作環境中。再結合靈活的付費模式、云端彈性算力,EDA云數據中心可以有效降低企業的硬件投入成本,提高芯片驗證效率。

以合見工軟針對某半導體設計公司的云數據中心項目為例,合見工軟為本項目定制化部署了企業級EDA云數據中心,建設了專用的IDC機房。根據客戶的算力要求,搭建了FPGA硬件驗證云設備集群,級聯數百顆FPGA,全天候7x24小時運行,為客戶的超大規模系統芯片做驗證。并可同步運作多種驗證場景,包括芯片設計仿真Simulation云任務、系統級PCB設計軟件云任務等,同時支持跨地域驗證團隊協同使用云數據中心資源。

七、結語

基于自建的EDA云數據中心,結合新一代時序驅動FPGA原型驗證系統UV APS等旗艦產品,合見工軟在解決大芯片的驗證問題方面實現了升維和突破,不僅進一步提升了我國在EDA驗證工具領域的水平,也將為國內半導體設計業的發展持續助力。

合見工軟秉承兩點原則為中國芯片企業提供支持:“以客戶為中心,以產品為核心競爭力”。EDA是一個產品為王的行業,在保持技術和性能領先的同時,需要更快地把握設計公司的真正需求和痛點,從前端需求上研發和演進EDA設計方法學,打造更好的產品和技術,并持續優化,秉持“守正出新,篤行致遠”的企業精神,合見工軟將不斷的進行迭代和技術更新,以保持產品競爭力。

審核編輯 :李倩

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603053 -

芯片

+關注

關注

455文章

50732瀏覽量

423283 -

eda

+關注

關注

71文章

2755瀏覽量

173219

原文標題:設計大芯片,這個問題不容忽視!

文章出處:【微信號:wc_ysj,微信公眾號:旺材芯片】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

i.MX處理器如何解決工業自動化三大痛點:PLC、人機交互、機器人

【直播預告】ADI &amp; WT·世健MCU痛點問題探索季:MCU應用難題全力擊破!

光伏電站運維系統解決傳統光伏電站運維痛點

IO模塊助力水處理行業升級,破解行業發展痛點

芯片測試和芯片驗證的區別

工業級路由器:解決網絡傳輸的痛點

錫膏點膠時拉絲不均勻,如何解決?

數據采集邊緣網關解決企業數據采集痛點的關鍵

電源測試系統如何解決電源模塊測試痛點?

如何解決大芯片的驗證痛點

如何解決大芯片的驗證痛點

評論