由于存在物理學定律,電阻、電容和電感將繼續成為挑戰。我們對此無能為力,所以自熱離子真空管問世以來,電子設計人員就學會了通過開發巧妙的電路拓撲來解決這些問題。事實證明,物理學就是物理學,過去適用于真空管的理論同樣適用于如今的高性能半導體。了解更多信息。

任何東西都打破不了物理定律。電阻器會將電能轉為熱能耗散,同時降低電壓;電容器需要時間來儲存和釋放電荷;電感器需要時間來產生和消除電磁場。我們對此無能為力,所以自熱離子真空管問世以來,電子設計人員就學會了通過開發巧妙的電路拓撲來解決這些問題。事實證明,物理學就是物理學,適用于真空管的理論同樣適用于如今的高性能半導體。

米勒電容如何限制高頻放大

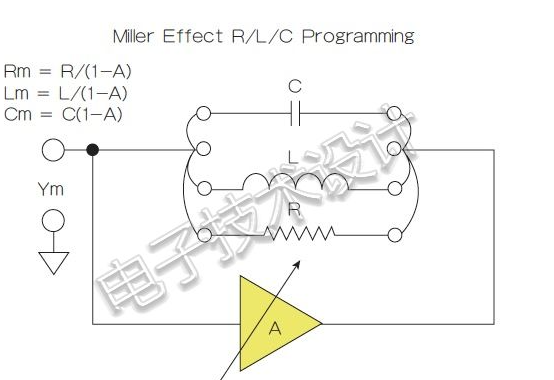

以米勒效應為例。20 世紀 20 年代,美國電氣工程師 John Milton Miller 發現將簡單三極真空管用作放大器時,柵極與陽極之間存在內部電容,這會導致一個問題。當電容阻抗隨工作頻率的上升而下降時,會施加越來越多的負反饋,從而降低放大器的帶寬。

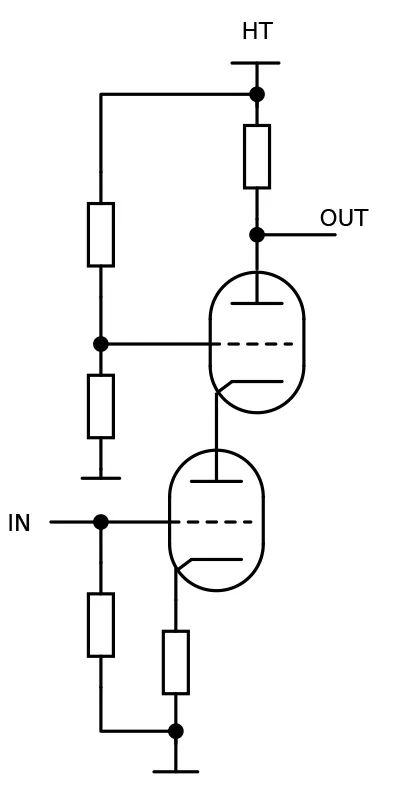

Miller 發現采用級聯三極管或共源共柵拓撲結構,將兩個三極真空管串聯可減少輸入至輸出的總電容,如圖 1中所示。鑒于上部電子管柵極處于固定電壓下,所以上部三極真空管的陰極電壓由下部三極真空管控制。開發出帶內部屏柵極的四極管后,這種內部電容及其相關影響就會降低,從而制造出工作頻率為數百兆赫的單管放大器。

圖 1:初始的級聯三極管或共源共柵電路

米勒效應的回歸

當設計人員開始使用固態半導體替換熱離子真空管時,米勒效應又出現了,并且開始再次限制高頻操作。

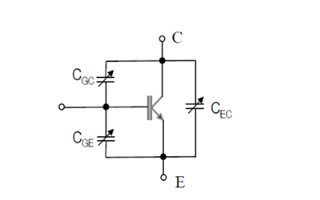

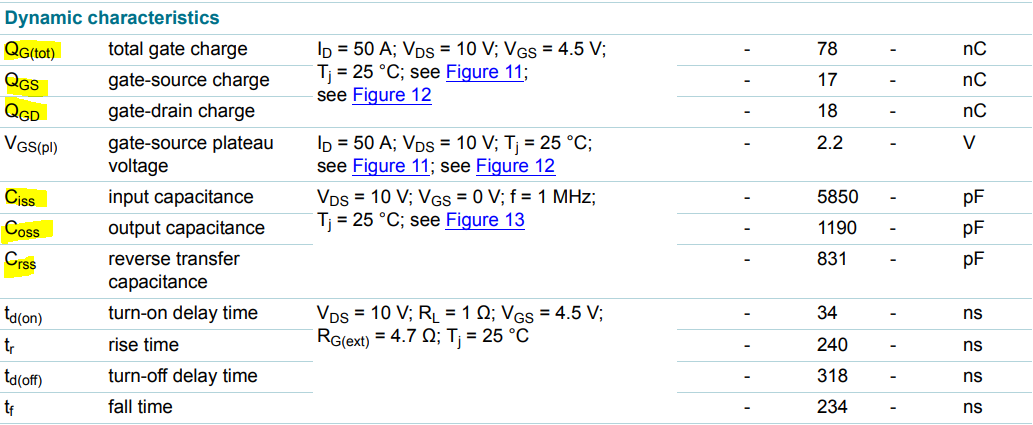

為什么會這樣?在基于 MOSFET 的開關電路中,米勒效應會限制開關速度,因為驅動電路必須以可靠的低損耗方式對輸入電容進行充放電。這種米勒電容效應(即 CGD)會隨著柵極電壓的不同而變化。

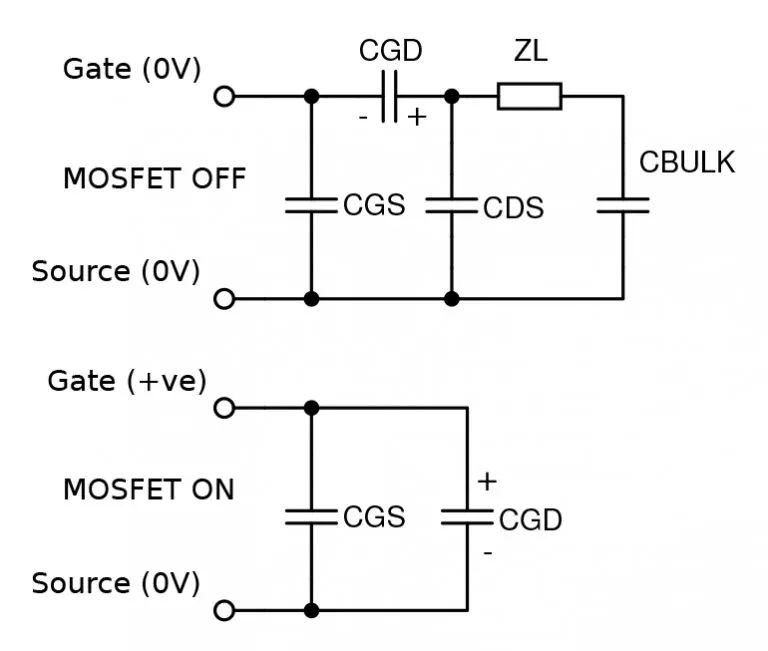

例如:考慮使用在柵極費電壓為 0V 時關斷的增強模式 MOSFET 開關。總柵極輸入電容如同一個網絡(見圖 2),包括 CGS、CGD、CDS、負載 ZL 以及大電容 CBULK。此外,CGD 兩端為正電壓。MOSFET 接通時,漏極電壓降至幾乎為零,且總電容變為 CGD 與 CGS 并聯,與斷開狀態相比,CGD 兩端為負電壓。在接通到斷開以及斷開到接通的開關過程中,輸入電容必須在上述情況之間切換。

圖 2:斷開和接通時,MOSFET 的等效輸入電容

圖 2:斷開和接通時,MOSFET 的等效輸入電容

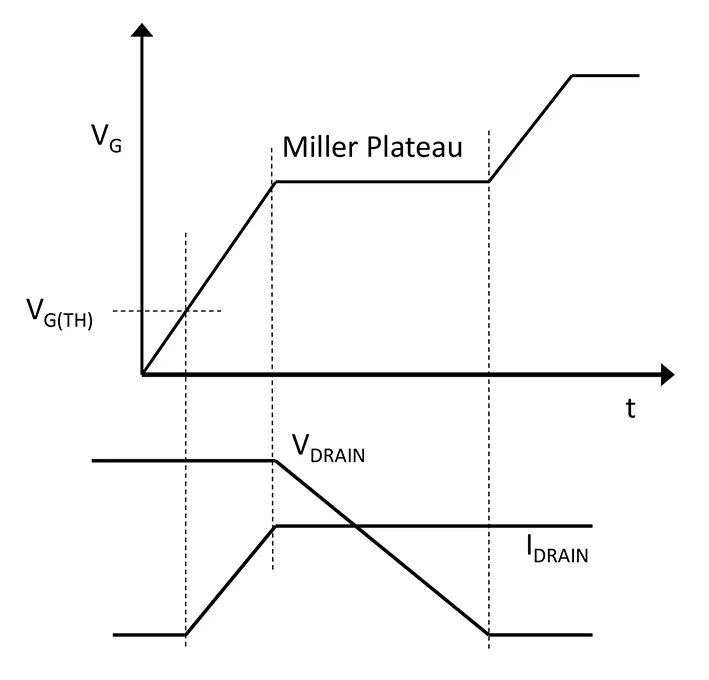

MOSFET 柵極開關波形中正向部分的平穩段(見圖 3)表示兩個輸入電容狀態之間的過渡,因為驅動器必須突然提高工作負荷,所以轉換速度變慢。更糟糕的是,當漏極電壓下降時,會試圖“推動”柵極負壓經過 CGD,與正導通電壓命令相抵觸。當斷開 MOSFET 時,這個過程就會反過來。CGD 會試圖“拉動”柵極正電壓,所以我們鼓勵使用 MOSFET 和 IGBT 的設計人員使用負的關態柵極電壓來抵消這種影響。這會反過來增加驅動柵極所需的功率。

圖 3:柵極驅動電壓的米勒電容 “平穩段”

圖 3:柵極驅動電壓的米勒電容 “平穩段”

控制柵極-漏極電容

器件的柵極-漏極電容 (CGD) 會受半導體器件的架構影響,其變化因器件是橫向構建還是縱向構建而異。我們可以通過縮小 CGD 來獲得低電壓 MOSFET,但這在高壓下會變成一個問題,尤其是當設計人員想要使用碳化硅 (SiC) 或氮化鎵 (GaN) 等材料構建寬帶隙器件時。有些物理問題是無法回避的:這些技術的開關速度仍受限于其米勒電容,而使用共源共柵電路拓撲是消除這種影響的最佳方法。

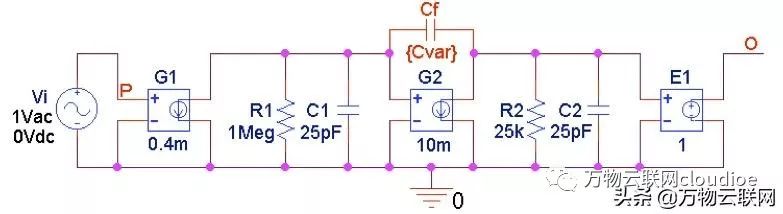

現代共源共柵

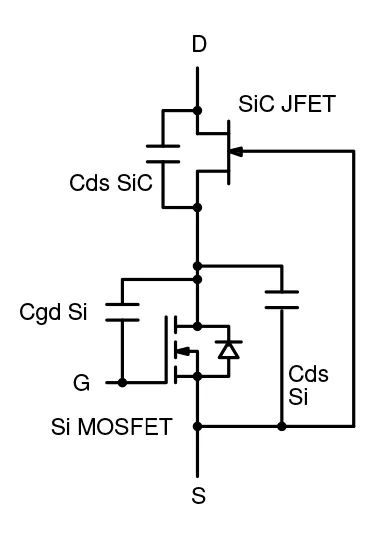

LINKS NEEDED 基本的 SiC 開關使用結 FET (JFET) 架構。如果 JFET 為縱向結構器件,則其 CGD 可以達到較有利的低點,且其漏極-源極電容 CDS 還可以更低。但是,JFET 為常開器件,其柵極電壓為 0 V,需要負柵極電壓才能關斷。這是橋式電路中存在的一個問題。在橋式電路中,所有器件在瞬時通電時默認為導通狀態。最好使用常閉器件來構建此類電路,該器件可通過將 Si MOSFET 和 SiC JFET 布置在級聯型拓撲中來實現,見圖 4。

圖 4:Si/SiC 共源共柵

當 MOSFET 的柵極和源極電壓均為 0 V 時,其漏極電壓會上升。JFET 柵極也為 0V,所以當其源極電壓(來自 MOSFET 漏極)上升至 10 V 時,JFET 柵極與源極之間的負電壓為 -10V,從而會使 JFET 關斷。當 MOSFET 柵極為正時,MOSFET 處于接通狀態,并且會使 JFET 的柵極-源極短路,從而接通 JFET。這種電路拓撲可實現 MOSFET 柵極電壓為 0V 的常閉器件。此外在該拓撲中,串聯輸入-輸出電容(包括 JFET 的 CDS)接近于 0,從而可以減少米勒效應及其對高頻增益的影響。

其他優勢

在開關時,由于 JFET 的源極電容 CDS 幾乎為零而 MOSFET 的 CDS 不為零,所以 Si MOSFET 漏極電壓會 “全然涌入” JFET 漏級,使得 MOSFET 漏極始終保持在低電壓狀態。換句話說,MOSFET 可以是低電壓類型,且漏極與源極間導通電阻非常低,因此柵極驅動變得更容易。其另一個優勢在于,低電壓 MOSFET 的體二極管具有非常低的正向壓降,且快速恢復性能出色。JFET 沒有體二極管,所以在換向橋接電路或同步整流等應用中,需要進行第三象限換向開關導通時,MOSFET 體二極管就會導通。這會將 JFET 柵極-源極電壓保持在大約 +0.6 V,確保能夠硬接通 JFET,使反向電流以低壓降流動。

米勒效應的終結

SiC 共源共柵拓撲能夠解決米勒電容問題,同時輕松實現柵極驅動、常關運行和高性能體二極管。這與 SiC MOSFET 和 GaN HEMT 均不同——前者的體二極管的性能比較差,后者的 CDS 比較高。物理學定律的不變性導致了熱離子器件中出現限制高頻增益的米勒效應,也在半導體器件中帶來了許多問題。然而,這種不變性也意味著基于共源共柵的解決方案在現代 SiC 器件中的作用與在老式真空管中的一樣有效。事物越是看似在變,就越是亙古不變。

審核編輯:劉清

-

MOSFET

+關注

關注

147文章

7156瀏覽量

213148 -

驅動器

+關注

關注

52文章

8226瀏覽量

146253 -

FET

+關注

關注

3文章

632瀏覽量

62948 -

CGD

+關注

關注

0文章

11瀏覽量

8167 -

米勒電容

+關注

關注

0文章

31瀏覽量

10805

原文標題:使用共源共柵拓撲消除半導體開關中的米勒效應

文章出處:【微信號:Qorvo_Inc,微信公眾號:Qorvo半導體】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

米勒效應使電壓放大器的輸入和輸出實例分析

米勒效應對MOSFET的危害

米勒電容如何限制高頻放大?

米勒電容如何限制高頻放大?

評論