寫(xiě)在前面

本文是本系列的第二篇,本文主要介紹FPGA常用運(yùn)算模塊-加減法器和乘法器,xilinx提供了相關(guān)的IP以便于用戶進(jìn)行開(kāi)發(fā)使用。

加減法器模塊

在xilinx中,有一個(gè)IP模塊提供加減法運(yùn)算的功能,

概述

加法器/減法器IP 提供 LUT 和單個(gè) DSP slice 實(shí)現(xiàn)加減法實(shí)現(xiàn)。加法器/減法器模塊可以創(chuàng)建加法器(A+B)、減法器(A–B) 和可動(dòng)態(tài)配置的加法器/減法器,用于操作有符號(hào)或無(wú)符號(hào)數(shù)據(jù)。該功能可以在一個(gè)單個(gè) DSP slice 或 LUT(但目前不是兩者的混合)。該模塊可以流水線化。支持fabric實(shí)現(xiàn)輸入范圍從1到256位寬,該IP核支持DSP片實(shí)現(xiàn),輸入高達(dá)58位。可選進(jìn)位輸入和輸出、時(shí)鐘啟用和同步清除、旁路(負(fù)載)能力、設(shè)置B值為一個(gè)常量。

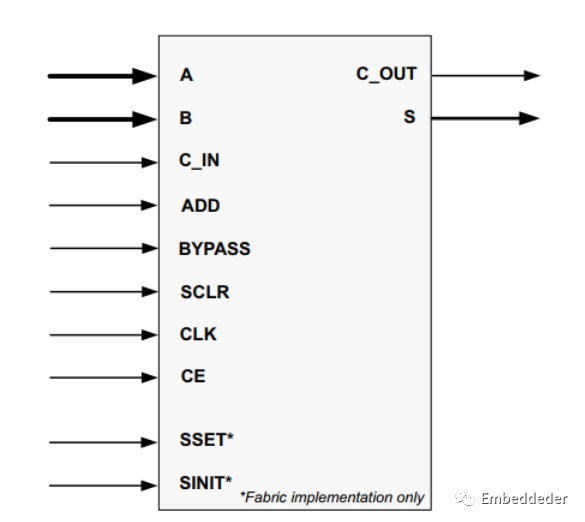

IP核圖示以及端口介紹

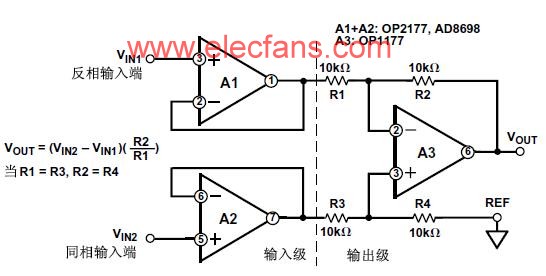

| Name | Direction | Description |

|---|---|---|

| A[N:0] | Input | 輸入端口A,位寬為N+1 |

| B[M:0] | Input | 輸入端口B,位寬為M+1 |

| ADD | Input | 控制加法器/減法器執(zhí)行的操作(1=加法,0=減法) |

| C_IN | Input | 進(jìn)位輸入 |

| C_OUT | Output | 進(jìn)位輸出 |

| S[P:0] | Output | 結(jié)果輸出 |

| BYPASS | Input | 旁路控制,將B輸出給S |

| CE | Input | 時(shí)鐘使能,高有效 |

| CLK | Input | 時(shí)鐘信號(hào),上升沿有效 |

| SCLR | Input | 同步復(fù)位,將重置核心中的所有寄存器,定制內(nèi)核時(shí)可以選擇SCLR和CE引腳的優(yōu)先級(jí) |

| SINIT | Input | Synchronous Initialization - forces outputs to a user defined state when driven High |

| SSET | Input | Synchronous Set - forces outputs to a High state when driven High |

如果Constant Input = TRUE and Bypass = FALSE,則B端口不存在。一個(gè)用戶定義的核心內(nèi)部常量被應(yīng)用到B操作數(shù)的位置。

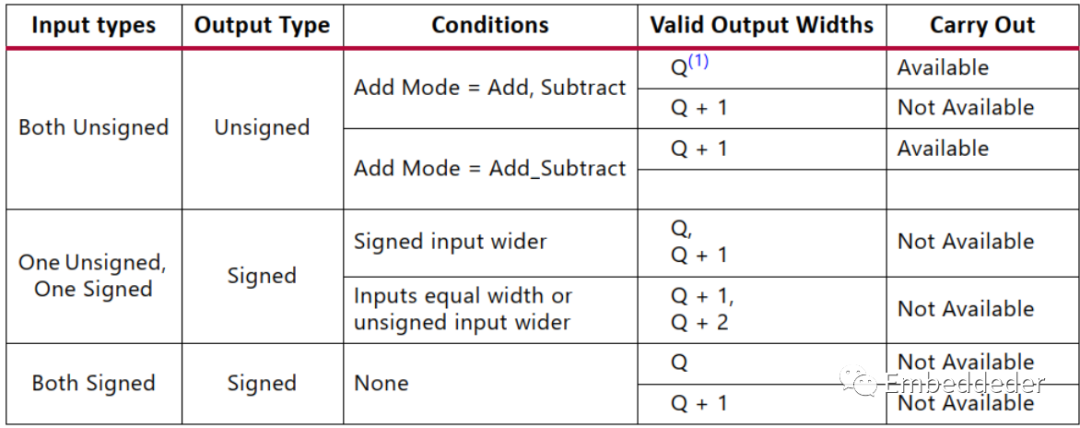

輸出位寬設(shè)計(jì)

Q的值等于AB輸入兩者之間的最大值。

流水線操作

加法器/減法器模塊可以選擇流水線操作用來(lái)提高速度。 流水線操作由延遲參數(shù)控制。 將延遲配置設(shè)置為自動(dòng),以實(shí)現(xiàn)最優(yōu)的流水線速度。 將延遲配置設(shè)置為手動(dòng),以允許在延遲參數(shù)中輸入有效數(shù)量的流水線層級(jí)數(shù)。

DSP片

對(duì)于DSP片的實(shí)現(xiàn)方式,單個(gè)的DSP片可以用0、1或2級(jí)寄存器進(jìn)行流水線操作。 Latency Configuration = Automatic ,此時(shí)優(yōu)化速度延遲獲得最優(yōu)的流水操作速度; 如果Latency = 1, 只有輸出寄存器存在。 Latency = 2,輸出和輸入寄存器都存在。

Fabric 實(shí)現(xiàn)

對(duì)于使用PFGA的邏輯資源的實(shí)現(xiàn)方式,流水線操作是通過(guò)將輸入總線 分成許多總線片(等于流水線階段的數(shù)量)來(lái)實(shí)現(xiàn)的。 在第一階段,對(duì)每個(gè)總線片做盡可能多的工作,將它們加在一起,并存儲(chǔ)結(jié)果和每個(gè)結(jié)果的進(jìn)位輸出。 在第二階段,從最低有效位的部分得到的進(jìn)位被輸入到下一個(gè)較高有效位的結(jié)果中,它產(chǎn)生一個(gè)進(jìn)位被輸入到下一個(gè)階段的下一個(gè)結(jié)果中,直到進(jìn)位被傳播到頂部。

因?yàn)樾枰鎯?chǔ)的數(shù)據(jù)較少,所以這比存儲(chǔ)每個(gè)切片的輸入直到生成該切片的進(jìn)位的更直觀的技術(shù)更有效。 此外,該設(shè)計(jì)更小且更易于布線。

上電或復(fù)位后,流水線模塊需要幾個(gè)時(shí)鐘周期才使輸出變?yōu)橛行В裳舆t控制參數(shù)指定。

如果在流水線模塊上請(qǐng)求旁路,則旁路值會(huì)在延遲控制指定的時(shí)鐘周期數(shù)之后出現(xiàn)在輸出上。 如果同時(shí)請(qǐng)求旁路和時(shí)鐘使能,則必須設(shè)置旁路優(yōu)先級(jí),以便旁路不會(huì)覆蓋時(shí)鐘使能。 對(duì)于流水線模塊,資源使用率大約是非流水線模塊的延遲倍數(shù)。 為了提高時(shí)鐘速度,流水線導(dǎo)致面積使用量的顯著增加。 如果需要延遲但面積比速度更重要,請(qǐng)?jiān)诖四K的 S 輸出中添加一個(gè)基于 SRL16 的移位寄存器,以優(yōu)化面積使用。

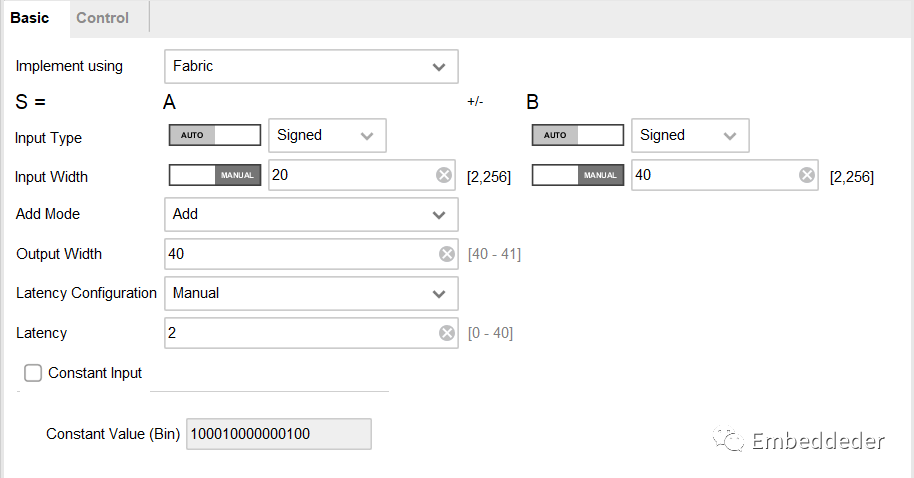

加法器IP配置

加法器IP配置如圖所示,

在basic界面,可以對(duì)IP的實(shí)現(xiàn)方式,輸入的數(shù)據(jù)類(lèi)型,位寬,IP的方式(加法器、減法器、加減法器)、流水操作延遲方式和延時(shí)周期,常數(shù)輸入進(jìn)行配置。

Constant Input and Constant Value :當(dāng)常量輸入為 TRUE 時(shí),端口 B 設(shè)置為參數(shù) Constant Value 指定的值。 常數(shù)值必須是以二進(jìn)制格式輸入且不得超過(guò) B 輸入寬度。 在大多數(shù)情況下指定端口 B 是一個(gè)常量時(shí)候,會(huì)自動(dòng)創(chuàng)建一個(gè)沒(méi)有端口 B 的模塊。 但是在當(dāng)請(qǐng)求旁路功能時(shí),因?yàn)樾枰丝?B 來(lái)提供旁路數(shù)據(jù)。 默認(rèn)是端口 B 提供的端口 B 值。 會(huì)生成B端口。

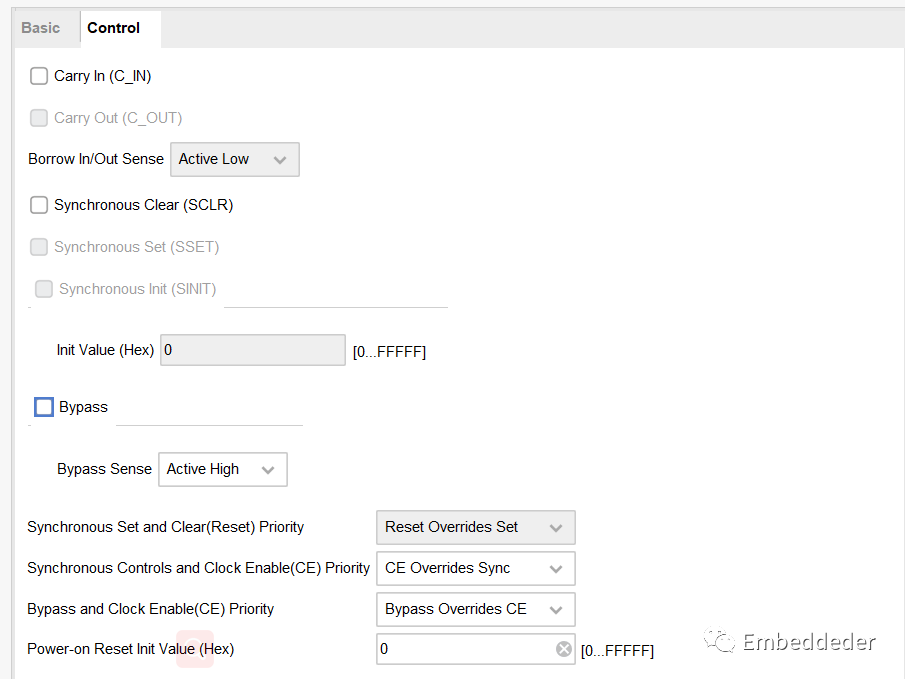

加減法器的控制配置界面如下,

在控制界面可以配置加減法器進(jìn)位、旁路、復(fù)位等控制操作。

Carry In :設(shè)置為T(mén)RUE時(shí),創(chuàng)建一個(gè)C_IN端口。 這是用于加法器的高電平有效進(jìn)位端口和用于減法器和加/減法器的可編程(高電平有效/低電平有效,帶借入/輸出檢測(cè))進(jìn)位端口。

Carry Out :當(dāng)設(shè)置為T(mén)RUE時(shí),創(chuàng)建一個(gè)端口C_OUT。 實(shí)現(xiàn)了加法器和加減法器的高有效同步進(jìn)位,以及可編程(設(shè)置高低有效,借入/借出檢測(cè))的減法器和加減法器中的減法器的借位標(biāo)志。

Bypass :設(shè)置為 TRUE 時(shí),創(chuàng)建旁路引腳。 激活 BYPASS 引腳設(shè)置輸出為端口 B 上給定的值。 此功能用于創(chuàng)建可加載的計(jì)數(shù)器和累加器。

Bypass and Clock Enable (CE) Priority :該參數(shù)控制是否旁路輸入由時(shí)鐘使能限定。 當(dāng)設(shè)置為Bypass_Overrides_CE時(shí),BYPASS 信號(hào)的激活也使能寄存器。 當(dāng)設(shè)置為CE_Overrides_Bypass,寄存器必須有 CE 激活才能加載 B 端口數(shù)據(jù)。

Bypass Sense :控制旁路的敏感電平,是高有效還是低有效,因?yàn)楦叩碗娖接行г谟行r(shí)候都能獲得更好的效率。

Borrow In/Out Sense :當(dāng)設(shè)置為Active_Low時(shí),用于減法的C_IN和C_OUT引腳是低有效的。 這符合fabric實(shí)現(xiàn)規(guī)則,是一個(gè)最佳設(shè)置。

Synchronous Set :指定是否包含 SSET 引腳。 在DSP實(shí)現(xiàn)模式下,SSET 引腳無(wú)效。

Synchronous Init :指定是否包含一個(gè)SINIT引腳,當(dāng)斷言時(shí),該引腳同步地將輸出值設(shè)置為Init value定義的值。 如果SINIT存在,那么SSET和SCLR都不存在。 在DSP實(shí)現(xiàn)模式下,SINIT引腳是無(wú)效的。

Init Value :十六進(jìn)制指定當(dāng)斷言SINIT時(shí)輸出初始化為指定的值。 如果Synchronous Init = false 則忽略。

Power on Reset Init Value :指定(十六進(jìn)制)S寄存器在上電復(fù)位時(shí)初始化的值。

Synchronous Controls and Clock Enable (CE) Priority : 該參數(shù)控制SCLR(以及邏輯單元模式下的SSET和SINIT)輸入是否由時(shí)鐘使能限定。 當(dāng)設(shè)置為 Sync_Overrides_CE 時(shí),同步控制覆蓋 CE 信號(hào)。 當(dāng)設(shè)置為 CE_Overrides_Sync 時(shí),控制信號(hào)僅在 CE 為高時(shí)有效。 請(qǐng)注意,在結(jié)構(gòu)原語(yǔ)上,SCLR 和 SSET 控制覆蓋 CE,因此選擇 CE_Overrides_Sync 通常會(huì)導(dǎo)致額外的邏輯。

Sync Set and Clear (Reset) Priority :控制 SCLR 和 SSET 的相對(duì)優(yōu)先級(jí)。 當(dāng)設(shè)置為 Reset_Overrides_Set 時(shí),SCLR 會(huì)覆蓋 SSET。 默認(rèn)值是Reset_Overrides_Set,因?yàn)檫@是原語(yǔ)的排列方式。 使 SSET 優(yōu)先需要額外的邏輯。

乘法器

乘法器IP實(shí)現(xiàn)高性能、優(yōu)化的乘法器方案。 可以使用資源和性能權(quán)衡選項(xiàng)來(lái)為特定的應(yīng)用程序定制IP。 該IP支持輸入范圍從1到64位,輸出從1到128位。 所有乘法器都可配置延遲。 當(dāng)使用DSP Slice時(shí),支持對(duì)稱(chēng)四舍五入到無(wú)限。

概述

乘法器IP允許設(shè)計(jì)者精細(xì)地構(gòu)建定點(diǎn)乘法器。 可以使用 DSP Slices、Slice 邏輯或組合的方式進(jìn)行構(gòu)建乘法器IP,并且針對(duì)性能或資源進(jìn)行了優(yōu)化的結(jié)構(gòu)。 常數(shù)系數(shù)乘法器也可以使用許多不同的邏輯資源選項(xiàng)來(lái)實(shí)現(xiàn)。 并且可以通過(guò)流水線操作層級(jí)數(shù)量以適應(yīng)延遲和性能要求。 DSP Slice的對(duì)稱(chēng)舍入特性可用于并行乘法器。

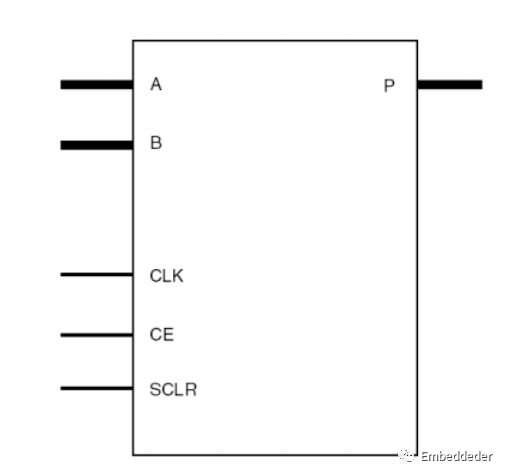

IP核圖示以及端口介紹

| Signal | Direction | Description |

|---|---|---|

| A[N-1:0] | Input | 乘數(shù)A,位寬為N |

| B[M-1:0] | Input | 乘數(shù)B,位寬為M,只有在parallel multipliers模式下有該端口。 |

| CLK | Input | 時(shí)鐘信號(hào) |

| CE | Input | 高有效時(shí)鐘使能信號(hào) |

| SCLR | Input | 高有效同步復(fù)位信號(hào),(SCLR/CE 優(yōu)先級(jí)可以配置) |

| P[X:Y] | Output | 乘法輸出 |

乘法器IP配置

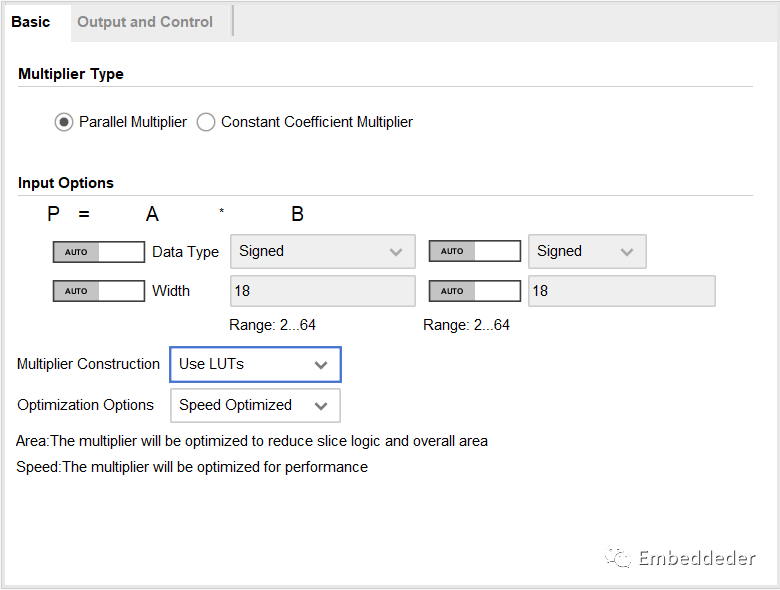

乘法器IP的basic配置界面如下:

在該界面可以進(jìn)行配置乘法器的類(lèi)型,乘數(shù)的數(shù)據(jù)類(lèi)型,位寬,乘法器的實(shí)現(xiàn)方式以及優(yōu)化方式。

Multiplier Type :在并行和常數(shù)系數(shù)乘法器選項(xiàng)之間進(jìn)行選擇。

并行乘法器選項(xiàng):這些選項(xiàng)只有當(dāng)選擇的乘法器類(lèi)型是并行乘法器時(shí)才可見(jiàn)。

Multiplier Construction :選擇用于IP實(shí)現(xiàn)的結(jié)構(gòu)是LUT還是專(zhuān)用乘法器原語(yǔ)。

優(yōu)化選項(xiàng) :

DSP48E1 Slice:可以為高達(dá) 47x47 的乘法器大小選擇速度或面積優(yōu)化。 速度優(yōu)化 :充分利用乘法器原語(yǔ)來(lái)提供最高性能的實(shí)現(xiàn)。 面積優(yōu)化 :混合使用切片邏輯和專(zhuān)用乘法器原語(yǔ)來(lái)降低基于 DSP 切片的乘法器利用率,同時(shí)仍提供合理的性能。 對(duì)于 47x47 以上的尺寸,只允許優(yōu)化速度。

LUT-based multipliers : 區(qū)域優(yōu)化降低了延遲和LUT利用率,以可實(shí)現(xiàn)的時(shí)鐘頻率為代價(jià)。 當(dāng)兩個(gè)輸入操作數(shù)都是無(wú)符號(hào)且兩個(gè)輸入操作數(shù)都小于16位時(shí),區(qū)域優(yōu)化是最有效的。

Constant-Coefficient Multiplier Options :這些選項(xiàng)只有當(dāng)選擇的乘數(shù)類(lèi)型是常數(shù)系數(shù)乘法器時(shí)才可見(jiàn)。

Coefficient :在顯示的范圍內(nèi)輸入系數(shù)的整數(shù)值。 支持正系數(shù)和負(fù)系數(shù)。 常量 (B) 端口的輸入類(lèi)型(有符號(hào)或無(wú)符號(hào))由 Vivado IDE 根據(jù)輸入的整數(shù)常量自動(dòng)配置。 可以選擇 A 端口是有符號(hào)的還是無(wú)符號(hào)的。

Memory Options : 選擇乘法器是使用分布式內(nèi)存、塊內(nèi)存還是使用 DSP Slices 來(lái)實(shí)現(xiàn)。

乘法器IP的輸出控制配置界面如下:

Output Product Range: 根據(jù)輸入操作數(shù)的寬度自動(dòng)配置輸出產(chǎn)品寬度。

Use Custom Output Width :如果通過(guò)設(shè)置 MSB 和 LSB 范圍,對(duì)輸出進(jìn)行切片。

Use Symmetric Rounding :對(duì)于基于 DSP Slice 的并行乘法器,如果需要,可以將乘積對(duì)稱(chēng)舍入到無(wú)窮大。這與MATLAB的 round 函數(shù)的行為相同。

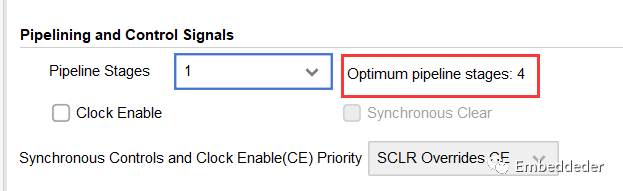

流水線和控制信號(hào):

流水線階段:

為乘數(shù)實(shí)例選擇流水線操作的層級(jí)。右邊的標(biāo)簽提供了關(guān)于實(shí)現(xiàn)最佳性能的流水操作的最佳數(shù)量的反饋。

Pipeline Stages = 0 意味著IP是組合的。

Pipeline Stages = 1 意味著IP的輸出是寄存器型的。

Pipeline Stages > 1 使寄存器插入到輸入和輸出之間,直到最優(yōu)的流水線操作的層級(jí)。添加更多寄存器可以提高可實(shí)現(xiàn)的時(shí)鐘速度,同時(shí)增加延遲。

流水線操作的層級(jí)設(shè)置的值大于最優(yōu)值的值,將導(dǎo)致在輸出時(shí)添加基于SRL16的移位寄存器,以實(shí)現(xiàn)額外的延遲。

Clock Enable :選擇設(shè)計(jì)中的所有寄存器是否都具有時(shí)鐘使能控制。

Synchronous Clear :選擇是否該設(shè)計(jì)中的所有寄存器都具有同步復(fù)位控制。

SCLR/CE Priority :當(dāng)SCLR和CE引腳同時(shí)存在時(shí),可以選擇scr和CE的優(yōu)先級(jí)。選擇 SCLR overrides CE ,使用的資源最少,實(shí)現(xiàn)的性能最好。

-

dsp

+關(guān)注

關(guān)注

553文章

7987瀏覽量

348757 -

FPGA

+關(guān)注

關(guān)注

1629文章

21729瀏覽量

603009 -

Xilinx

+關(guān)注

關(guān)注

71文章

2167瀏覽量

121305 -

乘法器

+關(guān)注

關(guān)注

8文章

205瀏覽量

37043 -

減法器

+關(guān)注

關(guān)注

1文章

26瀏覽量

16839

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

數(shù)字電路中加法器和減法器邏輯圖分析

減法器電路與原理 減法器電路圖分享

如何設(shè)計(jì)一個(gè)16比特的減法器呢?

怎么設(shè)計(jì)基于FPGA的WALLACETREE乘法器?

乘法器對(duì)數(shù)運(yùn)算電路應(yīng)用

乘法器的基本概念

基于IP核的乘法器設(shè)計(jì)

8位加法器和減法器設(shè)計(jì)實(shí)習(xí)報(bào)告

進(jìn)位保留Barrett模乘法器設(shè)計(jì)

乘法器原理_乘法器的作用

FPGA常用運(yùn)算模塊-復(fù)數(shù)乘法器

FPGA常用運(yùn)算模塊-加減法器和乘法器

FPGA常用運(yùn)算模塊-加減法器和乘法器

評(píng)論