現代FPGA綜合工具會自動執行門控時鐘轉換,而無需更改RTL代碼中的設計,然而,我們可能需要適當地手動指導綜合工具執行門控時鐘變換。需要注意的是,在這項任務中,各種綜合工具的能力是不一樣的,這是綜合工具效果的一個展示功能。

以下是使綜合工具成功轉換門控時鐘的一些簡單的指導。

識別基準時鐘,并通過添加頻率或周期約束將其定義到綜合工具中,例如vivado或者synplify。

不要將下游門控時鐘定義為時鐘。去掉在SoC設計流程中可能指定的門控時鐘的任何周期或頻率限制。

在綜合工具中設置任何必要的控件,以啟用門控時鐘轉換。

識別設計中由門控時鐘驅動的任何黑盒。要修復驅動黑盒的門控時鐘,必須識別黑盒的時鐘和時鐘啟用信號輸入。應使用特定于綜合工具的指令來識別它們。

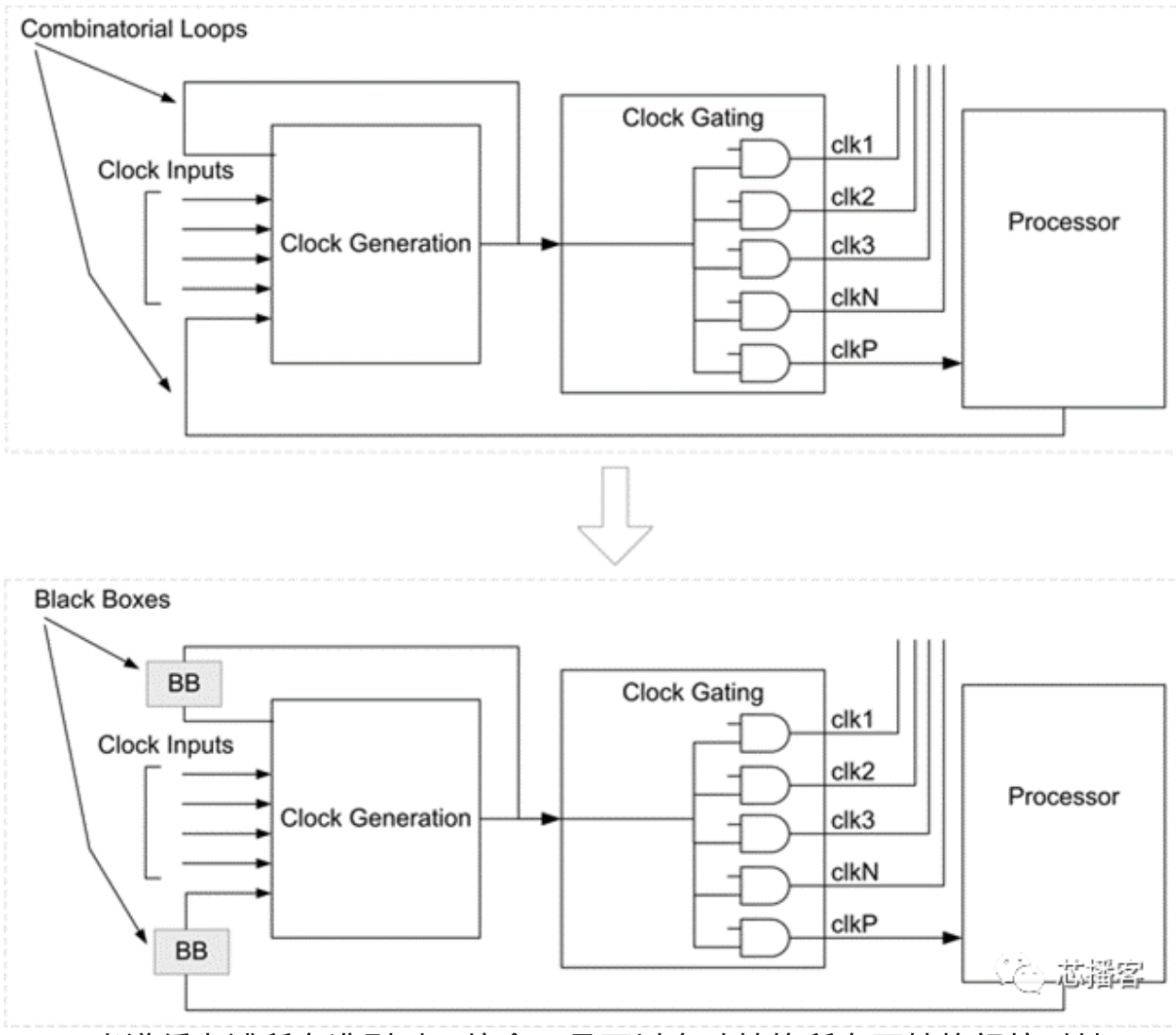

如果在時鐘門控邏輯中存在組合回路,則組合回路應該被斷開。這可以通過插入一個通路黑盒來實現,該黑盒是一個具有一個輸入和一個輸出的黑盒,位于組合環路路徑中,如圖所示。然后,我們可以為黑盒創建一個單獨的網表,輸出僅連接到輸入。然后,必須在放置和布線期間將為黑盒創建的網表添加到設計中。

當遵循上述所有準則時,綜合工具可以自動轉換所有可轉換門控時鐘。

當滿足以下所有條件時,門控時鐘可轉換。

1 對于選通信號的某些組合,選通時鐘輸出必須能夠被禁用。

2 對于選通信號的其余組合,選通時鐘輸出應等于基準時鐘或其反相值。

3 門控時鐘僅基于一個基準時鐘導出。

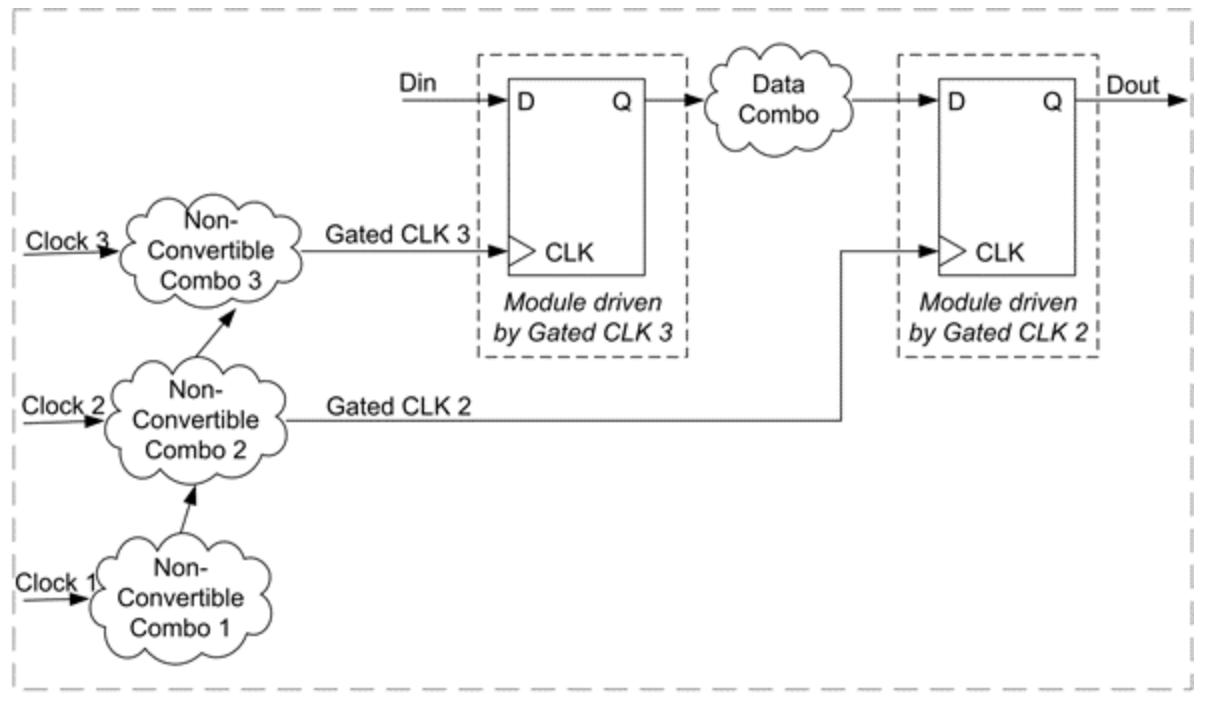

為了使SoC設計在基于FPGA的原型驗證平臺上可靠地工作,設計中的所有門控時鐘都應該被轉換。如果門控時鐘是基于多個時鐘導出的,或者門控邏輯是復雜的,那么合成工具不能進行門控時鐘轉換。然而,這些場景有時在SoC設計中很常見,這會導致許多設置和保持時間沖突。以下是處理這些場景的一些方法。如果適用,請共同使用所有這些方法。

如果在由基本時鐘驅動的時序元件和未轉換的門控時鐘之間沒有路徑,則后者將不會產生任何跨域時序沖突。然而,它們在FPGA中的布線可能需要仔細控制,以避免上述競爭。

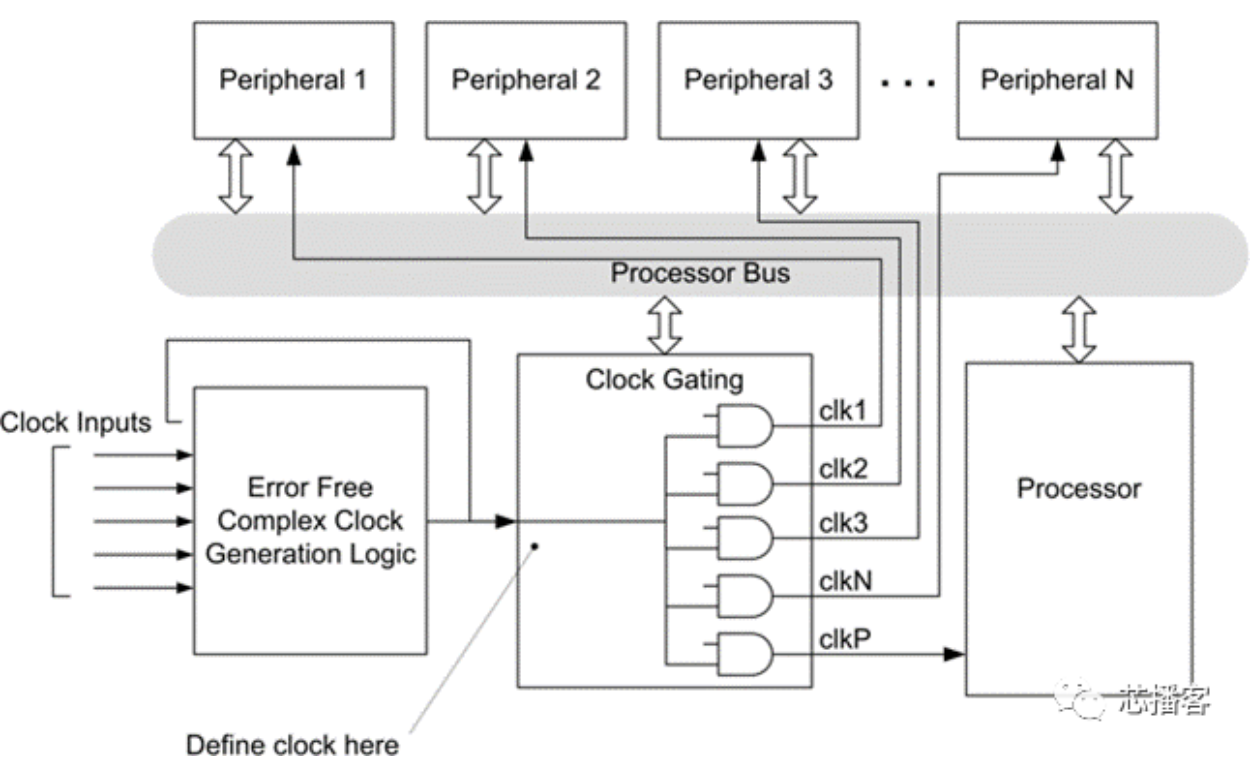

設計中的中間節點可以被識別并定義為基準時鐘,使得由該節點驅動的門控邏輯是可轉換的。通常,SoC設計將具有時鐘生成邏輯塊crg模塊,該邏輯塊具有復雜的邏輯以生成一個理想的時鐘。該時鐘將基于許多不同時鐘之間的切換而創建。該生成的時鐘將用作設計中具有單獨選通邏輯的其余塊的基準時鐘。在時鐘生成邏輯塊的輸出上定義時鐘將確保基于該時鐘創建的所有門控時鐘將由FPGA綜合工具轉換。

如果一個基本時鐘與其復雜門控時鐘之間存在有效的定時路徑,則嘗試手動平衡這些路徑之間的時鐘路徑。通過在

其中一個時鐘路徑中引入饋通LUT、時鐘緩沖器、PLL和數字時鐘管理器,可以實現平衡。

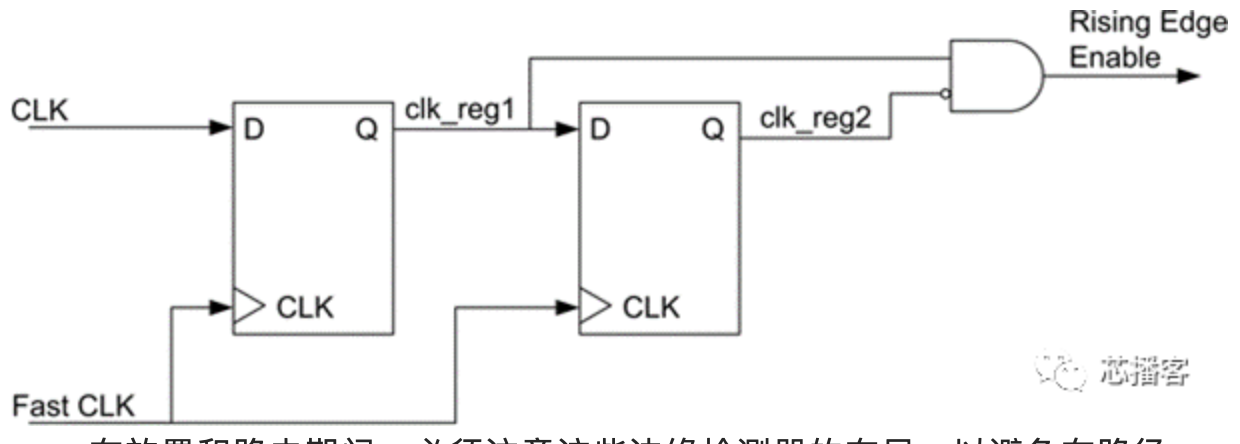

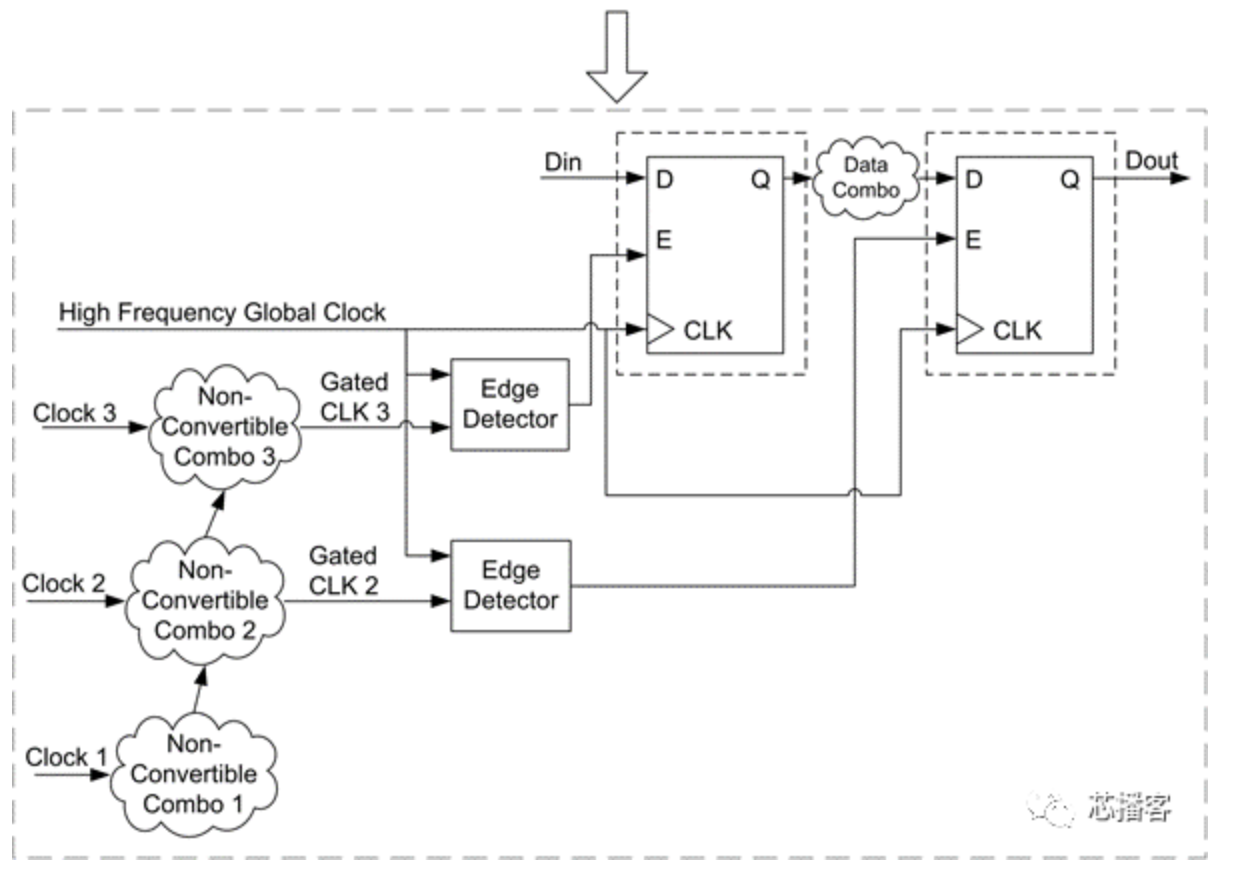

如果仍有一些門控時鐘未被轉換,并且存在巨大的有效時序沖突,則嘗試以非常高的頻率運行FPGA中的所有時序元件——大約是設計中最快時鐘的10倍。對于設計中的所有門控時鐘,插入相對于較快時鐘的上升沿檢測器。

該上升沿檢測器可以通過使用更快的時鐘對門控時鐘信號進行雙重注冊(例如clk_reg1和clk_reg2),然后形成邏輯以檢測從低到高的變化(~clk_reg2和 clk_reg_1)來設計,如果原始時鐘驅動也在負邊緣上工作的FF,則也需要負邊緣檢測器電路。

在放置和路由期間,必須注意這些邊緣檢測器的布局,以避免在路徑clk_reg1和clk_reg2之間引入差分延遲。使用這些邊緣檢測器的輸出作為所有順序元件的啟用,這些順序元件最初由相應的門控/生成時鐘驅動。

這樣,整個FPGA由一個更快的時鐘源驅動,如圖所示。該時鐘將使用FPGA中的專用全局路由資源,因此相關的時鐘偏差將非常小,并且可以很容易地滿足時序要求。

時鐘門控在SoC設計中很常見,為了在FPGA上成功原型化SoC設計,應謹慎處理門控時鐘。當受到適當約束時,現代FPGA綜合工具會自動處理大多數的門控時鐘。

-

時鐘緩沖器

+關注

關注

2文章

146瀏覽量

51352 -

SoC設計

+關注

關注

1文章

151瀏覽量

19191 -

RTL

+關注

關注

1文章

390瀏覽量

61182 -

FPGA開發板

+關注

關注

10文章

126瀏覽量

31991

發布評論請先 登錄

fpga門控時鐘問題

高頻RFID芯片的FPGA原型驗證平臺設計及驗證

什么是時鐘門控?如何去實線時鐘門控的設計呢

基于FPGA的時鐘設計

評論