現(xiàn)在,工程師比以往任何時候都更多地選擇基于碳化硅 (SiC) 的產(chǎn)品,因為它們比基于硅 (Si) 的組件具有更高的效率、功率密度和更好的整體系統(tǒng)成本效益。除了SiC和Si之間常見的基本設(shè)計原則,以及需要牢記SiC的不同特性、功能和優(yōu)勢之外,工程師還必須進行建模和仿真,以確保它們能夠滿足其設(shè)計目標。

與硅一樣,SiC現(xiàn)在擁有來自各種供應商的優(yōu)化工具和模型,并且可以應用標準建模緩解措施。雖然LTSpice、PLECS和Wolfspeed的SpeedFit 2.0設(shè)計模擬器?等工具之間存在差異,但Wolfspeed的電源專家的提示將有助于實現(xiàn)SiC的仿真精度。

使用 LTSpice 進行靜態(tài)仿真

Wolfspeed 的 Spice 型號針對 25oC 和 150oC 進行了優(yōu)化。體二極管操作針對驅(qū)動電壓 VGS進行了優(yōu)化,第 4 代器件為 -3 V,第 5 代器件為 -2 V。工程師可以結(jié)合自發(fā)熱和瞬態(tài)熱能力以及寄生電感。然而,沒有對寄生雙極性和相關(guān)效應、雪崩倍增過程以及體二極管導通電壓隨柵極到源極的變化進行建模。

LTSpice 靜態(tài)仿真結(jié)果(各種 VGS 值下的 IV 曲線和體二極管曲線)與實際測量結(jié)果非常吻合。對于電容 — 輸入電容 Ciss、輸出電容、Coss 和反向傳輸電容 Crss,靜態(tài)仿真結(jié)果也相當接近。因此,工程師可以對Spice建模的靜態(tài)參數(shù)充滿信心。

雙脈沖測試

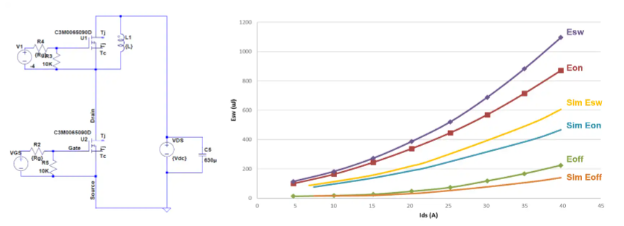

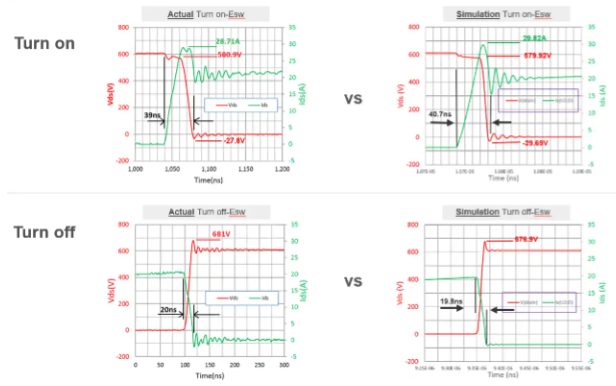

了解動態(tài)行為的典型表征基準是半橋雙脈沖測試。在沒有任何考慮寄生效應等因素的情況下進行建模時,仿真結(jié)果明顯偏離測量結(jié)果(圖 1)。由于能耗會影響效率,因此如此大的差異會對熱計算產(chǎn)生重大影響。

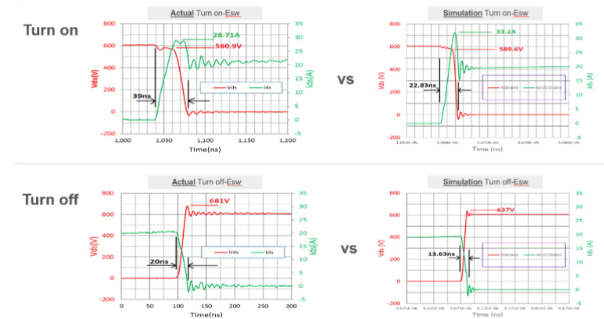

在測試用例中,長脈沖后跟1 μs間隙,后跟短脈沖。導通和關(guān)斷以傳統(tǒng)方式測量,就像使用硅基器件一樣。仔細觀察波形(圖2)可以發(fā)現(xiàn)實際仿真結(jié)果和理想仿真結(jié)果之間的差異。

圖1:理想的雙脈沖測試仿真開關(guān)損耗結(jié)果比DUT、U45數(shù)據(jù)表中的結(jié)果低約2%。

仿真中的上升和下降時間都比測量的要快得多,因為實際結(jié)果受電感的影響——兩個器件之間的寄生雜散電感Lm和封裝電感Lpkg,即封裝的源極電感。開啟和關(guān)閉的過沖結(jié)果也存在差異。這些差異導致了開關(guān)損耗的總體差異。

圖2:波形比較顯示,實際導通上升時間為39 ns,模擬上升時間為22.83 ns,實際下降時間為20 ns,仿真為13.63 ns。

為了獲得精確的模型,必須提取電感并將其手動導入LTSpice。另一方面,PLECS中的熱模型不包括寄生元件。

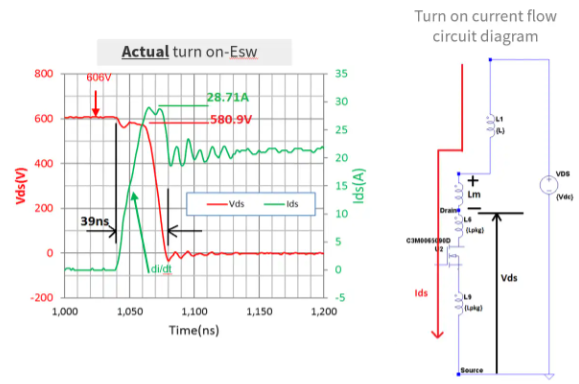

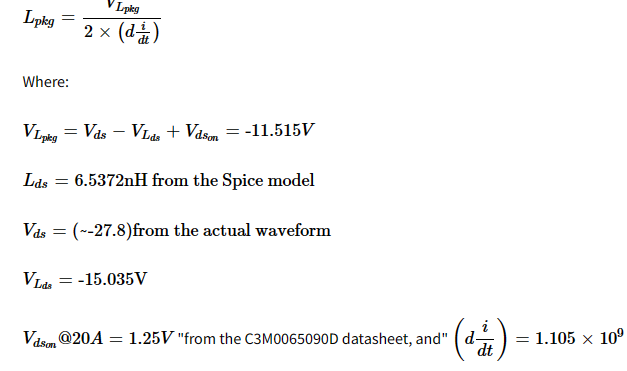

圖3:從實際波形中提取的信息可用于計算Lm

發(fā)現(xiàn) Lm

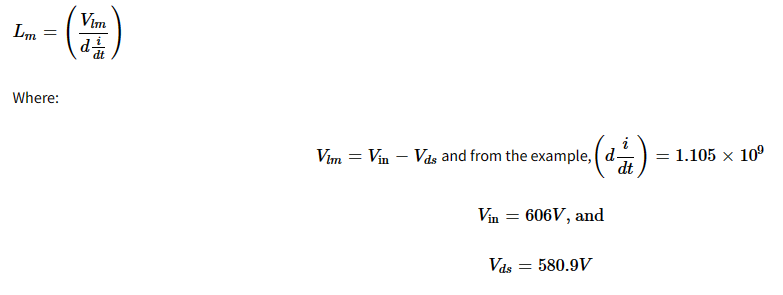

Lm是高邊U1器件的源極和低邊U2器件的漏極之間的電感。雖然可以直接測量,但也可以這樣提取(圖3):

這給出了 Lm 的值為 23.1674 nH

無論是同步降壓、同步升壓、半橋還是全橋,該設(shè)計都可能通過PCB配置高端和低端器件。如果遵循良好的布局實踐,Lm 在 20 nH 至 25 nH 范圍內(nèi)。工程師可以將其視為在仿真中使用的經(jīng)驗法則。

提取升包

設(shè)計人員可能希望 Lpkg 在標準封裝(如 TO-247)的供應商中是相同的。但是,由于引線框架的厚度、源極引線鍵合和封裝肩部長度的差異,存在差異。如果數(shù)據(jù)表中可用,則可以輕松將其插入模型。如果沒有,則可以從測量波形中提取它,并外推到手頭封裝的良好估計值。

圖4:將計算出的電感添加到LTSpice模型中,使其接近實際測量值

在我們的示例中,這給出了 Lpkg 值為 2.503 nH。盡管存在變化,但該值可以被視為一個很好的估計和可靠的經(jīng)驗法則。在考慮電感后進行仿真可使動態(tài)模型準確(圖 4)。

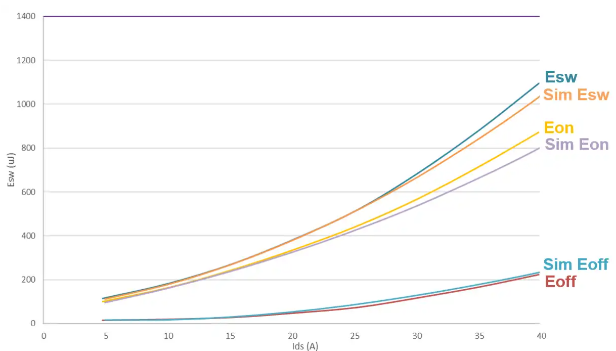

圖5:使用設(shè)置寄生效應后,仿真開關(guān)損耗與C3M0065090D數(shù)據(jù)手冊相匹配。

考慮到電感,實際和模擬雙脈沖測試的總開關(guān)能量Esw以及Eon和Eoff變得非常接近(圖5)。

使用這些 Lm 和 Lpkg 的經(jīng)驗法則,工程師可以對其熱預算進行相當準確的損耗和熱計算。

并聯(lián) MOSFET

SiC MOSFET通常并聯(lián)放置,以提高載流能力和功率水平。但是,有一些注意事項需要牢記:

寄生電感不對稱導致的電流不平衡

柵極驅(qū)動振蕩

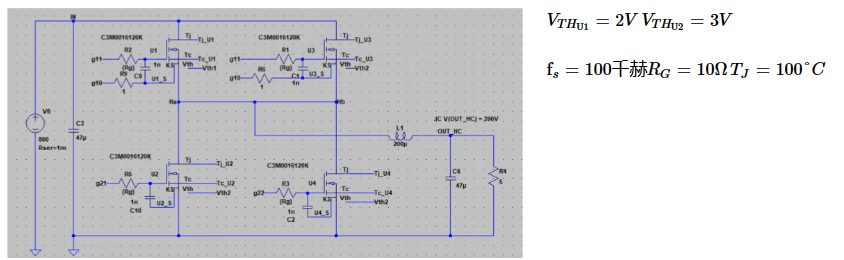

使用Wolfspeed SiC MOSFET,器件特性不匹配的可能性很小。但是,工程師可能需要使用其他規(guī)格公差更寬的SiC器件,并且可能會選擇具有2 V VTH的器件和另一個具有3 V的器件。具有較低閾值的器件具有較高的瞬態(tài),因此,開關(guān)損耗和導通損耗較高,因此總功率損耗較高(圖 6)。

圖6:由于電流不平衡,2 V器件的總損耗幾乎是3 V器件的兩倍。

| 參數(shù) | 場效應管 U1 | 場效應管 U3 |

|---|---|---|

| VTH(V) | 2 | 3 |

| i有效值(A) | 29.821 | 25.745 |

| iDC(A) | 21.11 | 18.69 |

| EON(μJ) | 1011.5 | 609.77 |

| E關(guān)閉(μJ) | 986.29 | 405.58 |

| E總計(μJ) | 1997.79 | 1014.35 |

| 總損失 (W) | 216.53 | 115.87 |

具有較低閾值電壓的 MOSFET

瞬態(tài)和靜態(tài)期間電流較高

更高的開關(guān)損耗、更高的傳導損耗和總功率損耗

盡管兩款器件具有相同的柵極電阻RG,并且在相同的溫度和開關(guān)頻率下工作,但不考慮任何因素的建模導致U1的總損耗超過200 W,U3的總損耗略高于100 W。 仿真波形顯示,U1在降至70 A的穩(wěn)定狀態(tài)之前峰值約為50 A的過沖, 而U3峰值約為49 A,穩(wěn)定狀態(tài)為30 A。因此,兩個器件之間的載流能力存在相當大的不匹配,并且導通和關(guān)斷時間略有不同。

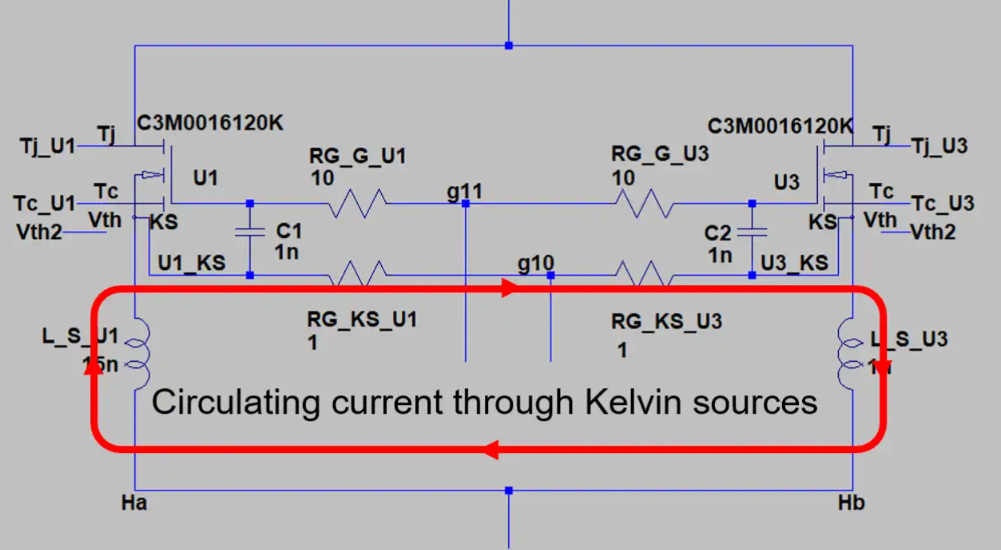

電流不平衡的第二個原因是不對稱寄生效應。考慮兩個器件,U1和U3(圖7),它們的VTH相同,但源極電感不同。這會導致di/dt、雜散電感兩端的電壓、柵極驅(qū)動和漏極電流相當不平衡。仿真波形顯示,U3的電流上升和下降速度要快得多,而IDC和IRMS的電流上升和下降速度要快得多,導致該MOSFET的開關(guān)損耗增加17.9%,總損耗增加18.3%。

圖7:在本例中,U1和U3的雜散電感Ls的差異被夸大了,以證明失配的影響。

| 參數(shù) | 場效應管 U1 | 場效應管 U3 |

|---|---|---|

| VTH(V) | 3 | 3 |

| Stray Ls(nH) | 15 | 1 |

| i有效值(A) | 26.437 | 28.857 |

| iDC(A) | 18.523 | 20.231 |

| EON(μJ) | 391.85 | 1151.6 |

| E關(guān)閉(μJ) | 974.05 | 459.02 |

| E總計(μJ) | 1365.9 | 1610.62 |

| 總損失 (W) | 153.21 | 181.29 |

通過良好的設(shè)計減少不匹配

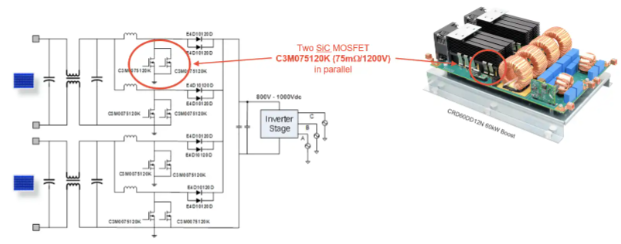

通過采用良好的設(shè)計實踐,可以大大減少不匹配的MOSFET的影響。例如,以 60 kW 太陽能逆變器升壓參考設(shè)計 CRD60DD12N 為例,該設(shè)計并聯(lián)使用兩個 75 mΩ 1,200V C3M075120K MOSFET(圖 8)。如果采用良好的設(shè)計實踐,則使用來自 247 個器件樣本的 TO-4 60 引腳 MOSFET 中的兩個具有最高和最低 VTH 的 TO-<> MOSFET,仍然可以實現(xiàn)運行良好的硬件。

圖8:盡管存在VTH差異,但該測試電路中器件失配的影響降至最低。

| 參數(shù) | 問1 | 問2 |

|---|---|---|

| VTH(V) | 3.006 | 2.666 |

| RDS_ON(mΩ) | 81.82 | 67.96 |

| i有效值(A) | 3.64 | 4.01 |

從 60 個樣品中挑選出兩個具有最高和最低 VTH 的零件

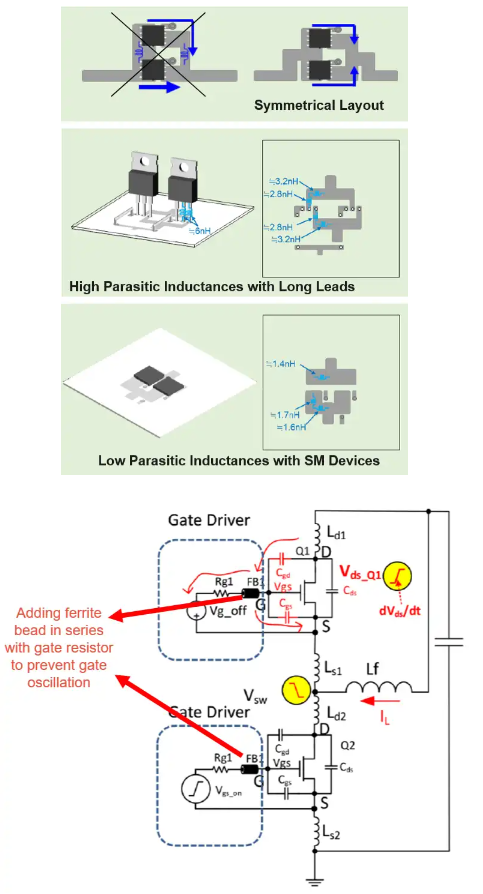

對稱的PCB布局對于降低并聯(lián)開關(guān)柵極環(huán)路中的環(huán)流至關(guān)重要。將電源環(huán)路與柵極環(huán)路分開,提供足夠的阻尼以防止柵極振蕩,并在柵極支腿處添加鐵氧體磁珠,以減少可能導致部件損壞的柵極上的電壓尖峰和振鈴(圖 9)。

圖 9:良好的設(shè)計實踐 – 緊密對稱布局、平衡信號、電源和柵極環(huán)路分離、防止柵極振蕩的阻尼以及帶有鐵氧體磁珠的小 RG 以減少振鈴 – 所有這些都可以減少電流不平衡。

由于這些設(shè)計實踐,測試電路中的Q1承載總電流的47.6%,而Q2承載52.4%,盡管器件不匹配,但仍達到可接受的實際結(jié)果。

增加刀具選擇

基于 SiC 的設(shè)計可以使用 Wolfspeed 的 SpeedFit、LTSpice 或 PLECS 進行建模。雖然SpeedFit和LTSpice可以通過注冊Wolfspeed自由使用,但PLECS需要支付訂閱費。工具之間的差異既影響了生成仿真的方式,也影響了它們的局限性,例如在處理寄生效應和計算損耗方面。

審核編輯:郭婷

-

二極管

+關(guān)注

關(guān)注

147文章

9627瀏覽量

166309 -

MOSFET

+關(guān)注

關(guān)注

147文章

7156瀏覽量

213148 -

SiC

+關(guān)注

關(guān)注

29文章

2804瀏覽量

62608

發(fā)布評論請先 登錄

相關(guān)推薦

基于碳化硅MOSFET的20KW高效LLC諧振隔離DC/DC變換器方案研究

碳化硅深層的特性

碳化硅MOSFET的SCT怎么樣?

功率模塊中的完整碳化硅性能怎么樣?

淺談硅IGBT與碳化硅MOSFET驅(qū)動的區(qū)別

TO-247封裝碳化硅MOSFET引入輔助源極管腳的必要性

圖騰柱無橋PFC中混合碳化硅分立器件的應用

在開關(guān)電源轉(zhuǎn)換器中充分利用碳化硅器件的性能優(yōu)勢

碳化硅MOSFET什么意思

Wolfspeed開始向中國終端客戶批量出貨碳化硅MOSFET

Wolfspeed采用TOLL封裝的碳化硅MOSFET產(chǎn)品介紹

使用Wolfspeed碳化硅MOSFET對常見拓撲進行建模

使用Wolfspeed碳化硅MOSFET對常見拓撲進行建模

評論